Предлагаемое устройство относится к области вычислительной техники и, в частности, к области запоминающих устройств (ЗУ) и может быть применено при построении ЗУ вычислительных машин параллельного действия, к которым предъявляется требование малого времени ремонта.

В известных параллельных ЗУ, содержащих числовые и разрядные тракты, используется подключение числового резервного тракта. Однако это не дает возможности устранить неисправность элементов разрядного тракта (например, усилителей воспроизведения, разрядных формирователей записи и т. д.).

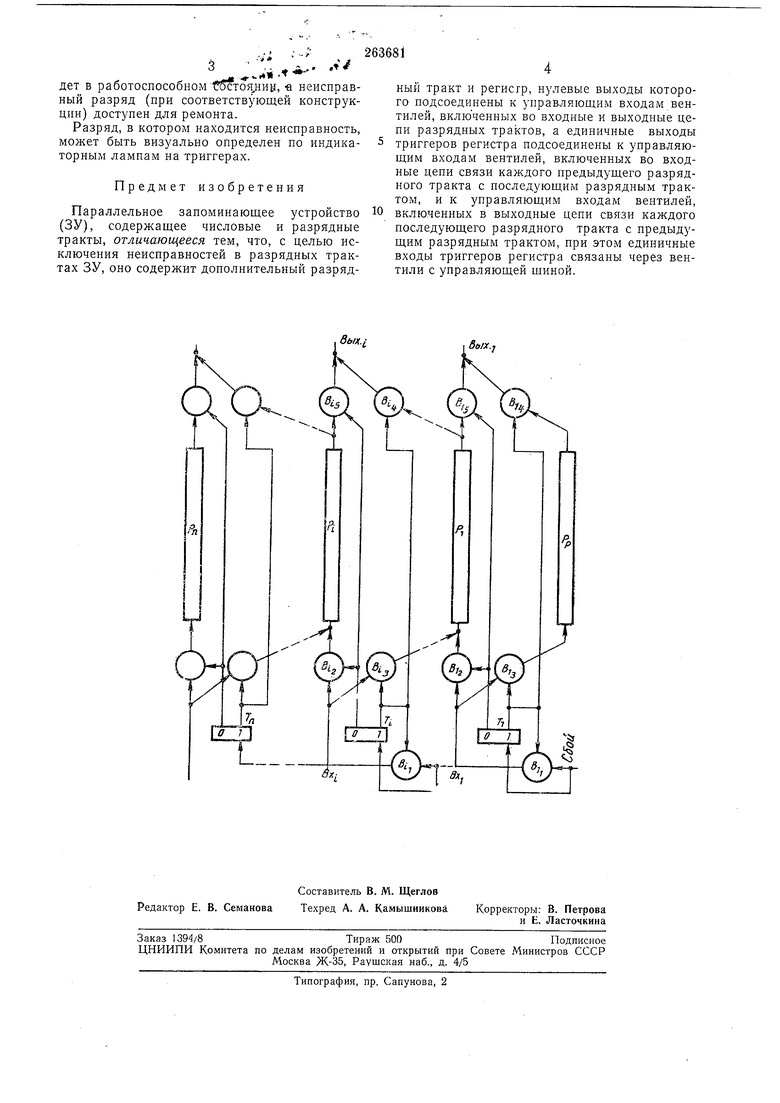

В описываемом устройстве это устранено тем, что оно содержит дополнительный разрядный тракт и регистр, нулевые выходы которого подсоединены к управляющим входам вентилей, включенных во входные и выходные цепи разрядных трактов, а единичные выходы триггеров регистра подсоединены к управляющим входам вентилей, включенных во входные цепи связи каждого предыдущего разрядного тракта с последующим разрядным трактом, и к управляющим входам вентилей, включенных в выходные цепи связи каждого последующего разрядного тракта с предыдущим разрядным трактом, при этом единичные входы триггеров регистра связаны через вентили с управляющей шиной.

Это позволяет исключать неисправности в разрядных трактах ЗУ.

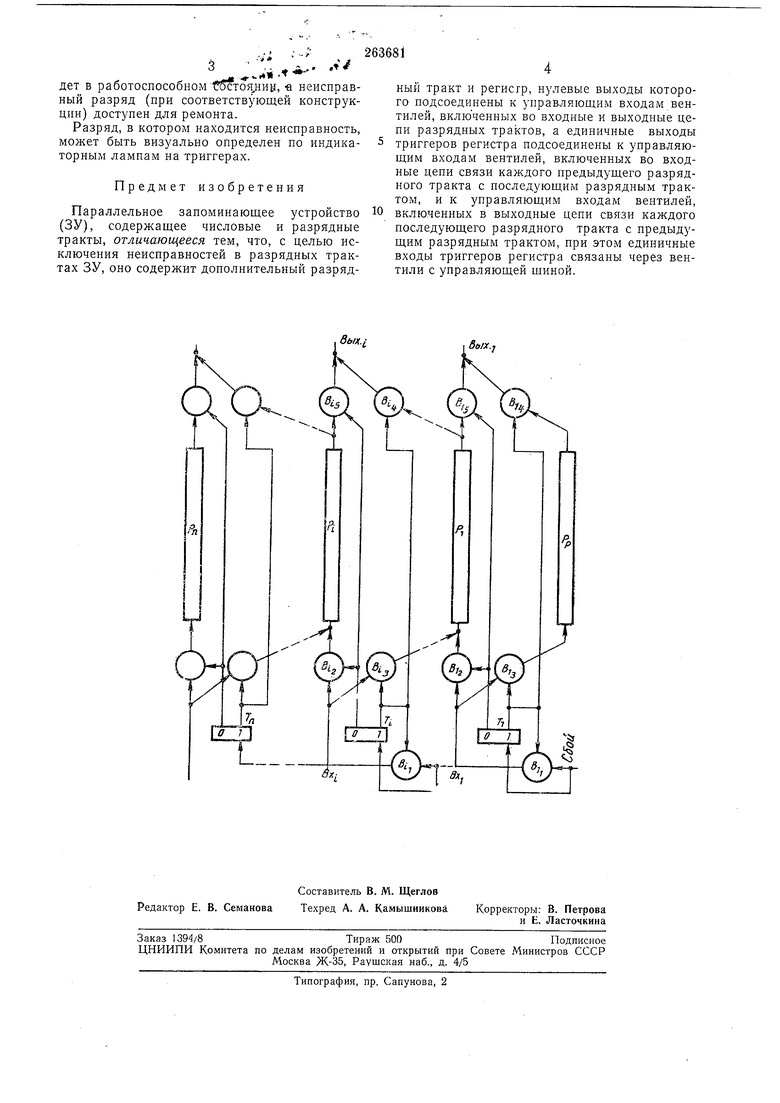

На чертеже изображена схема описываемого ЗУ.

Переключательная схема содержит регистр из триггеров TI-Т„ и вентилей Bi -Bi,, (где i - меняется от 1 до п).

В исходном состоянии для работы используются разряды PI-РЛ , причем каждый разряд Pi соединен со входом Вх через вентиль Bi и с выходом Вх через вентиль Bi,. . Все триггеры Т1 находятся в состоянии «О. Вентили Bi , Б/, и Б/, -закрыты, вентили Bi, и Bi. - открыты.

При наличии сигнала на входе управляющей шины «Сбой триггер Т переходит в состояние «1. При этом вентили Вг, BI., , Bi открываются, а вентили Bi, и Bi. -закрываются.

В результате входы Вх и выход BbiXi будут подключены к дополнительному разрядному (резервному) тракту Pp.

Разряд PI будет заблокирован.

Если тест вновь выявит ошибку, то произойдет новое переключение, в результате чего разряд PI будет соединен со входом Вх-2 и выходом BbiXz, а разряд PZ заблокирован. 5 le. .. HP дет в работоспособном тостоя нин, -а неисправный разряд (при соответствующей конструкции) доступен для ремонта. Разряд, в котором находится неисправность, может быть визуально определен по индикаторным лампам на триггерах. Предмет изобретения Параллельное запоминающее устройство (ЗУ), содержащее числовые и разрядные тракты, отличающееся тем, что, с целью исключения неисправностей в разрядных трактах ЗУ, оно содержит дополнительный разрядныи тракт и регистр, нулевые выходы которого подсоединены к управляющи.м входам вентилей, включенных во входные и выходные цепи разрядных трактов, а единичные выходы триггеров регистра подсоединены к управляющим входам вентилей, включенных во входные цепи связи каждого предыдущего разрядного тракта с послед.ующим разрядным трактом, и к управляющим входам вентилей, включенных в выходные цепи связи каждого последующего разрядного тракта с предыдущим разрядным трактом, при этом единичные входы триггеров регистра связаны через вентили с управляющей шиной.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1978 |

|

SU781973A1 |

| ЛОГИЧЕСКОЕ ПОЛНОТОЧНОВ ЗАПОМИНАЮЩЕЕ L'rifc :ИГ УСТРОЙСТВОI.™™———- | 1973 |

|

SU374658A1 |

| ЛОГИЧЕСКОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1970 |

|

SU258388A1 |

| ЛОГИЧЕСКОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1973 |

|

SU368643A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1973 |

|

SU386442A1 |

| Трехканальная резервированная микропроцессорная система | 1985 |

|

SU1378287A1 |

| Запоминающее устройство с замещениемдЕфЕКТНыХ ячЕЕК | 1978 |

|

SU803009A1 |

| Логическое запоминающее устройство | 1972 |

|

SU474847A2 |

| ЦИФРОВАЯ ВЫЧИСЛИТЕЛЬНАЯ МАШИНА С АВТОМАТИЧЕСКИМ ПРОГРАММИРОВАНИЕМ И МИКРОПРОГРАММНЫМ УСТРОЙСТВОМ УПРАВЛЕНИЯ | 1964 |

|

SU224161A1 |

| Многофункциональное запоминающее устройство | 1972 |

|

SU458037A1 |

вых.

Btjfx.j

Даты

1970-01-01—Публикация