(54) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1975 |

|

SU607276A1 |

| Запоминающее устройство с самоконтролем | 1981 |

|

SU970476A1 |

| Запоминающее устройство с резервированием | 1980 |

|

SU963088A1 |

| Запоминающее устройство | 1979 |

|

SU842955A1 |

| Запоминающее устройство | 1980 |

|

SU858095A1 |

| Запоминающее устройство | 1980 |

|

SU903973A1 |

| Трехканальная резервированная микропроцессорная система | 1985 |

|

SU1378287A1 |

| Оперативное запоминающее устройство с самоконтролем | 1982 |

|

SU1042081A1 |

| Запоминающее устройство с коррекцией однократных ошибок | 1982 |

|

SU1073799A1 |

| Устройство для имитации неисправностей | 1988 |

|

SU1536388A1 |

Изобретение относятся к автоматике i и. вычислительной технике, а именно к эа поминаюаим устройствам (ЗУ) ъычкст тельных машин параллельного действия, |к которым преды вляются требования устранения одной неисправности. Известно параллельное запоминающее . устройство, содержащее числовые в разрядные трактуя, дополнительный разрядныД . тракт и регистр, нулевые выхрды )го подсоединены к упрвЕщякшим входам вентилей, включенных .JBo вводные и ёыхбдныё цепи разрядных тректЧ в, а единичные :выходы триггеров peifacipa подсоединёну ;К управлякшим входам вентипей| вкточенных во входные кепи свиязи кйжДбГ Ьпрёдыдущаго разрядного тракта с последующим разрядным трактом, и к управляющим входам вентилей, включенных в выходные &епи связи каждсво - последукяцего рааряд ц ного тракта с предыдущим разрядным; трактом, при этом единичные входы триггеров адреса связаны через вентили с yiiравляюшей шиной рГ|.

--. ;.- 2,

fleiUtcret атого устройства - низкое дс фсшёйсфвае переключении резервного рвзрбгаа на место отказавшего, так Ksst {$едервйый разряд поДкшочается после1 ате ййй бместо первого, второго, Иг-го Оо тех вор, псйка не заблокируется разряд, яв йнёхцгйсв источником ошибки. Если неHcnpa ioctb в rt -ом разряде, то необходимо h перекйю ёний для устранения неис1фавности.:

НаибЬл ее близк1 м техническим решением к предлагаемому является устройство, cc ep aitiee Группы элементов И, регистр 13Дреса, нулеЁые выходы которого подключены к одним из входов элементов И первой и второй групп, другие входы которых соединены соответственно с входами устрбйства и Шзтходами одноразрядных блоков , Памяти, а выходы подключены соответственно к входам; одноразрядных блоков памяти и выходам устройства, резервный одноразрядный блок памяти, управляющую и контрольные шины, третью, четвертую и пятую группы элементов И, причем пер24s;;i SJS3t -- --, .с:, - 3S-«- -i 376вые входы элементов И третьей и четвертой груЯЯ бД&лючёны к единичным выхо Лам регистра адреса, вторые входы соответственно к входамустройства и вь1: хбДу резервного одноразрядного блока па- ййТйГа бйходы - соответственно к вхо ЙУ резервного одноразрядного блсжа памЗтй и вьлходам устройства, первые входы элементов И пятой группы соединены .с входами устройства, вторые входы с управляющей шиной, а выходы - с вхо ЙШй рбГййТра адреса, нулевые выходы регис-фаадреса подключены к входам первого элемента И, выход которого соединен с перв1ими входами второго и третьего элементов И (входной и выходной элементы И резервного одноразрядного блока памяти), вторые входы которых псэдключевы соответственно к входной контрольной ши БЬ1х6ду резервного одноразрядного бпШа памяти, а выходьт - соответствейнр к входу резервного одноразрядного блогса памяти и выходной контролыюй шине |. Недостатки этого устройства - наличие многовходоЕрго элемента И iina счробиро ЙШй резервного разряда, так как для построения памяти с большим коЛйЧёстВол раз рядов, например 64, при использовании . вмеющейся элементной базы требуется 9 шт. восьмиксодовых элементов И, что значительно усложняет устройство в цепом; резерв лй одноразрядный блок памя г- J-,....jj.y,y ти по входу и выходу также должен иметь менты для согласоваййя нагрузочных режимов, так, при указанной разрядности , HJa етоде резервного одноразрядного блока памяти требуется установка 9 шт. восьмивходовых элементов И, а на 8 шТ. элементов, что увеличивает количёство резервного обо| о 1Й ПГ1гШайвт д н1олнвтельйые задерлскв о тракту юсод резервного разряда, т.е. снижает йШроШйствие резГрвяа б ШШр гШого блока памяти и устройства в целом; резарввый азряд подключаетсй к каждому из основ11ЫХ разрядов, что обусловливает нашгчие дшнных линий CBaaC H i8l pifii-&t%jtb но влияет йа помехоустойчивость и быстродейстше устройства. Целью изобрвтеййя ЯБняетсяуйрстевннв устройс: еа иг «сшышение его бйстрбйвЙствня.. ;. -/, , ; , ,.,..„„, /ПостедШШай ШШ доствг что в запоминающем устройстве, содержаi«Siiiii..,--,--.- :. . . ---- - - - -,- --. . шем групры .элементов И, регистр адреса, которого через элементы И первой группы подключены к управдЯ1С1цей шгане.

, -iV-V -i---- -- - ---t-1 ,-,

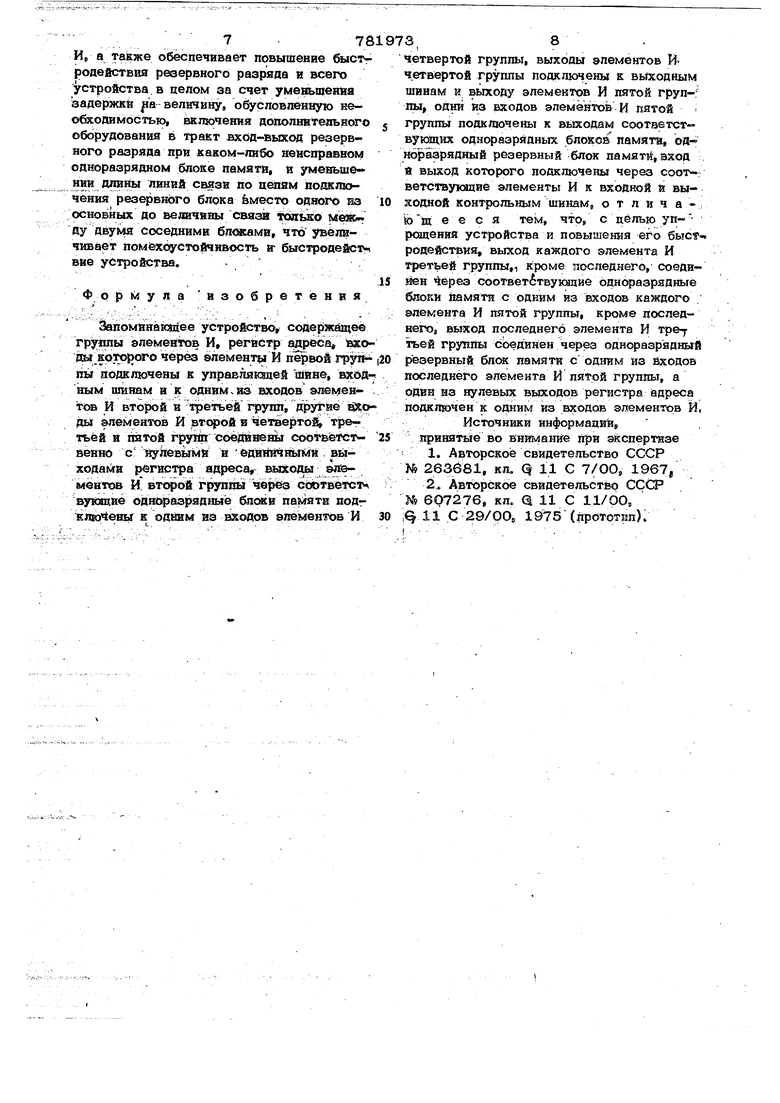

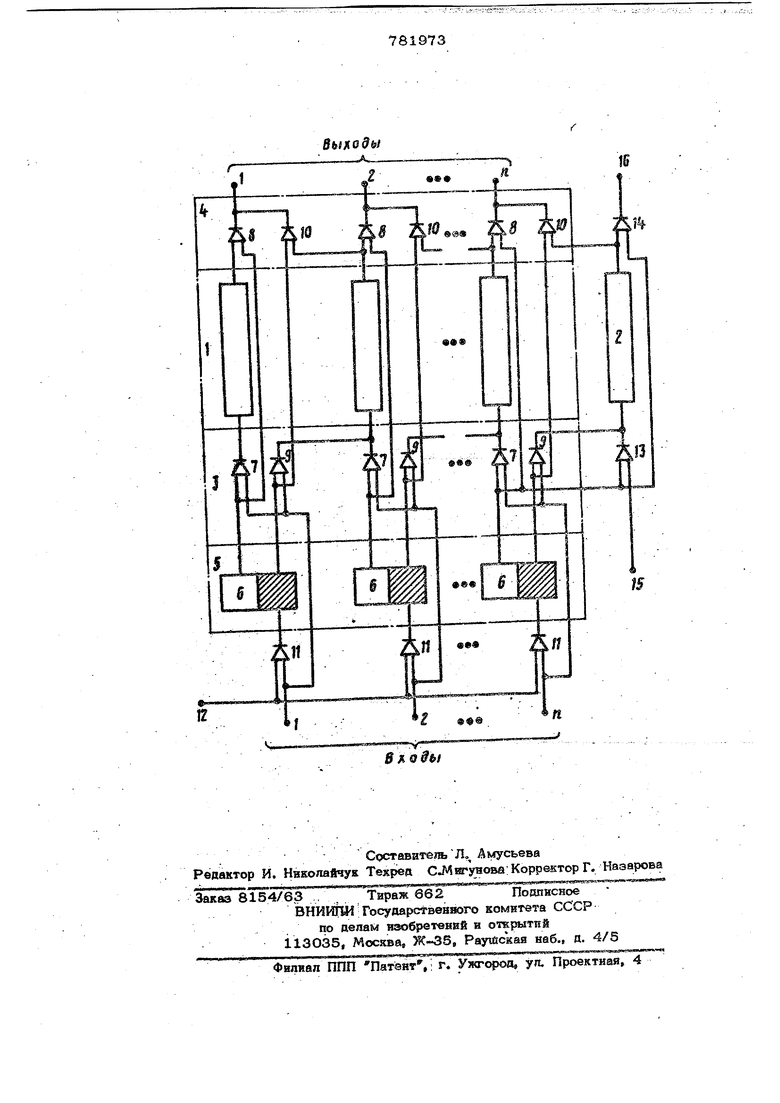

PPfSTS: -. -.,. :-:- ; ; / 4 входнь1М псинам;и к одним из входов элементов И второй и третьей групп, другие входы элементов И второй и четвертой, третьей и пятой групп соединены соответственно с нулевыми и единичными вытиша-г MB регистра адреса, выходы элементов И . второй группы через соответствующие одно разрпдные блоки памяти подключены к одним из входов элементов И четвертой группы, выходы элементов И четвертой группы подключены к выходным цганам и выходу элементов И пятой группы, одни из вхоIgoB элементов И пятой группы подключены к выходам соответствующих одноразрядных блсйсоё памяти, одноразрядный резервный бпок памяти, вход и выход которого подключены через соответствующие элементы И к входной и выходной кой1 рольным шинам, выходы каждого элемента/ И третьей группы, кроме последнего соединены через соответствующие одноразрядные блоки памяти с одним из входов каждогб элемента И пятой группы, кроме последнего, выход последнего элемш та И третьей группы соединен через одноразрядный резервный блок памяти с одним из входов последнего элемента И пятой грутшГ, а одни из вупешх выходга р еестра ajcspebs подкшочвЕгы к однга вз входов элементов И. За счет такетв подктЬченвя обеспечивается ис попь вавве вместо отказавшего одноразрядного блока памяти последующе-. )4f Шнорадрядяого памяти, а резерв ный ftaapm выполняет тлкя последнего одноразрядного блока памяти, что сушественнб упрощает устройство и повышает его быстродействие.; На чертеже представлена фушщвональвая скема запоминающего устройства. ycTpoficTBo содерхшт однс аёрядиые блоки 1 памяти, одноразрядный резервный 2 памяти, блоки 3 и 4 элеклентов И, регистр 5 адреса, состоящий ;вз триггеров в. ЁГблок 3 входят элементы 7 И второй группы, выходы которых подключейь коюсодам одворазрядшях блоков 1 памятв. В блок 4 Екодят элементы 8 И четвертой группы, бдин из входов псшслкжойы к выходам сооТветствукяцих 1 памяти, а выходы - к выходам устройства. В блок 3 также входят элементы 9 И третьей Г1руппы. Выход первого элёмента И третьей группы подключен ко входу второго одноразрядного блока 1 памяти, выход .П -1 элемента - ко входу одяоразрядяо го резервжэго блока 2 . памяти. В бл(ж 4 входят также элементы lO И natou группы. Один ва вхоаов первого элемента И пятой группы подключен к выходу второго одноразрядного блока 1 памяти, вход 1 -1 элемента И этой группы - к выходу п -го блока 1, а вход П-го элемента И этой же группы - к эы-г Ходу одноразрядного резервного блсжа 1 памяти. Выходы элеме1 гов 10 И пятой группы соединены с выходами устройсйа. Нулевые выходы триггеров б соединены с первыми входами элементов И )ой груп пы и четвертой группы, единичные выходы - с первыми входами элементов И третьей группы и вторыми входами элементов И пятой группы. Устройство также содер жит э лементы 11 И первой группы, Ьдни входы которьк подключены к входам устройстве и вторым входам элементов И вто рой и третьей групп другие входы - к управляюшей шине 12, а выхошл - к входам тригг ов Устрбйство также содержит элементы , 13 и 14 И одноразрядного резервного блока памяти, одни из ш:од которьйс под ключены к нулевому выходу триггера б ,fl -го разряда регистра адреса, вторые входы - СООТВеТСТЁвИНО к ЕКОДНрЙ КОНТроПЬ ной ишне 15 и выходу блока 2, а выходы - соответственно ко входу блока 2 и выходной контрольной шине 16. Устройство работает следукшим образом. ..,.,В исходном СОСТОЯНИЙ при отсутс:тв 1и сигнала на шине 12 элементы 11-И закрыты, триггеры б регистра 5 установивны в нулевое состояние (на нулевых выхо дах высокий потетиал, а «а еди пгчнБяс выходах - нвзквй). Элеменпл 9 и 1О И закрыты, {элементы 7 и в И открыты в пропускают сигналы со входе® ЗУ на вмг ходы однс азрядшлх блоков памяти (БП) 1 и с выходов одноразрядт }х БП 1 на выходы устройства. Высокий потещиая на нулевом выходе посяеднего трштера 6 регистра S открывает эпемеяты 13 и 14 И, и вход 15 контрольной шины подсоединяет ся ко входу одноразрядного резервного ВП 2, а выход одноразрядного резервяого БП 2 подсоединяется к выходной конт|ррш ной шине. До появления неисправности одноразрядный резервный БП 2 вспояьзуетсв для контроля на четность. При наличии неисправности однсгр из одноразрядных БП 1 на шину 12 подает ся сигнал, который открывает элементы 11 И. Со входов ЗУ через элементы11 И подаётся «од на единичные входы триггеров б регистра 5. Код состоит из нупей в единиц. На входы триггеров б регистра адреса 5, находящихся перед неисправным разрядом БП 1, подаются нулевые сигналы, а на остальные - единичные. Единичные сигналы устанавливают триггеры б регистра 6 в единичное состояние {на единичных вькодах триггеров б высо,лий потенциал, на : нулевых выходах - низкий) нулевые сигналы кода подтверждают нулевое состояние остальных триггеров 6. Сигнал снимается с шины 12 и элементыИ закрываются. Триггеры 6, находящиеся перед неисправным разряде остаются в нулевом СОСТОЯНИЙ, а триггеры б неисправного и всех посяедугощих разрядов в. единичном, элемвйтъз 7 и 8 И, подключенные к нулевым триггеров б,установлвнньос в ещнйчйое состояние, аакрыватотся, а эпемеаты 9 и 1О И, подК1вочённые к единичным выходам триггерой б, устансшленвьйс в нулевое состояние, открываются и соединяют входы устройства, начиная с неисправного разряда, . со входами последукяайх йдйоразрядных БП 1 таким образом, что последний вход устройства оказывается подклюгенньгм ко EiXdsy одноразрядного резервного БП 2, а внход однораарядкого ВП 2 подключается к последнему выходу устройства, выход последнего одноразряднр;ГоБП 1 подсоединяется к предпоследнему выходу устройства и т.д., выход БП 1, стоящего перед неисправным БП 1, подсоединяется, к выходу устройства неисправного разряда. Таким образом, неисправный одноразрядный БП 1 блокируется, вместо него подягаочается последукшзий ВП 1, вместо П-1 однс азрядного БП 1подключается 1(1-ый однсфазряДныЙ БП 1, а резервный БП 2 вьптопняет функции И -го одноразрядйого БП 1.Одновреме1шо отключается схема контроля, так как с нулевого выхода последнего триггера б подается низkий потенциал на элементов 13 и 14 И. При этом элементы 13 и 14 ,И выключаются в прорывают цепи для сит валов Со входа 15 на вход одноразрядного резервного БП 2 и с выхода однорааряшкаго резервного БП 2 на выход 16.,П{}в этом контроль не производится. Предлагаемое устройство имеет по ердвяевию с т звестным более простую к(1рукцвю вследствие исключения многовхюдового элемента И, формирукяиего сигнал на подключение резервного разряда вместо отказавшего одного из основных разрядов, в применения в данном устройстве только двухвходовых элементов И, а также обеспечивает повышение быстг {зодействвя резервного разряда н всего устройства. в целом за счет умеш щенвя задержЕв |ia величину, обусловпенвую необходимостью, включения допопннтедьного оборудования в тракт вход-выход резервного разряда при каком-либо неисправном одноразрядном блоке памяти, и уменьшении длины линий связи по аепям пошглючения резервного блока Ьместо одного на основных до веяичвны связи ткзаь&о ду двумя соседними блоками, что увеличивает помехоустойчивость и- быстродейС1ч вне устройства.Ф о рмула изобретения Запоминакзгее устройство содержащее груяпы элемейтов И, регистр egpeca, teso HM soTot oro через элемент л И первой гру пы подключены к управляющей Шине, вхЫ1 ным пшнам и к одним.из входов элементе® И второй и третьей групп, другие вхо ды элементов И и четвертой Tjpe тьёй и пятой fpyiada соёдйвены cooTiBteTCTйенж) с йуйевымй и бдйнйчныШ выходами регистра адреса выхоли едемёнтов и второй групйы черкез сдответстч вуквдие однефазрядныё блоки памяти подг клао ены к оашм из входов этемен-гов И четвертой группы, выходы элементов Ичетвертой группы подключены к выходным шинам и выходу элементов И пятой груп-: mj, одни из входов элементов И пятой группы подключены к вьпсодам соотввтст- вукйцих одноразрядных блокой памяти, од норазрядный резервный блок памяти, вход и выход которого подключены через ветствующие элементы И к входной я выходной контрольным шинамв от л и ч а - . Ьш ее с я тем, что, с целью упрощения устройства и повышения его быстродействия, выход каждого элемента И третьей группы,1 кроме поспеднего, соедиsieH iepe3 соответствующие одноразрядные блоки памяти с одним из входов каждого элемента И пятой группы, кроме последнегоа выход последнего элемента И тре-у тьей группы соединен через одноразрядный резервный блок памяти с одним из йходов последнего элемента И пятой группы, а один из нулевых выходов регистра адрес1Э подключен к одник из входов элементов И, Источники ннформааиНа принятые во внимание при экспертизе 1. Авторское свидетегаьство СССР № 263681, кли Q 11 С 7/ОО, 1967, И, Авторское свидетельство СССР Н, 6Q7276, кл. а 11 С 11/00, , 11 С 29/00 1975 (прототш).

BbSKoOtfi

8ло Sbi

Авторы

Даты

1980-11-23—Публикация

1978-11-04—Подача