Изобретение относится к области автоматики и .вычислительной техники.

Известны двоичные потенциальные счетчики с параллельным распределением единиц переноса, состоящие из потенциальных логических схем и триггеров, в которых каждым основным триггером управляет один вспомогательный триггер.

Предложенное устройство отличается тем, что в нем дополнительные триггеры объединены ,в регистр управления, хранящий номер переноса в двоичном коде.

Это позволяет сократить количество оборудования и повысить надежность устройства.

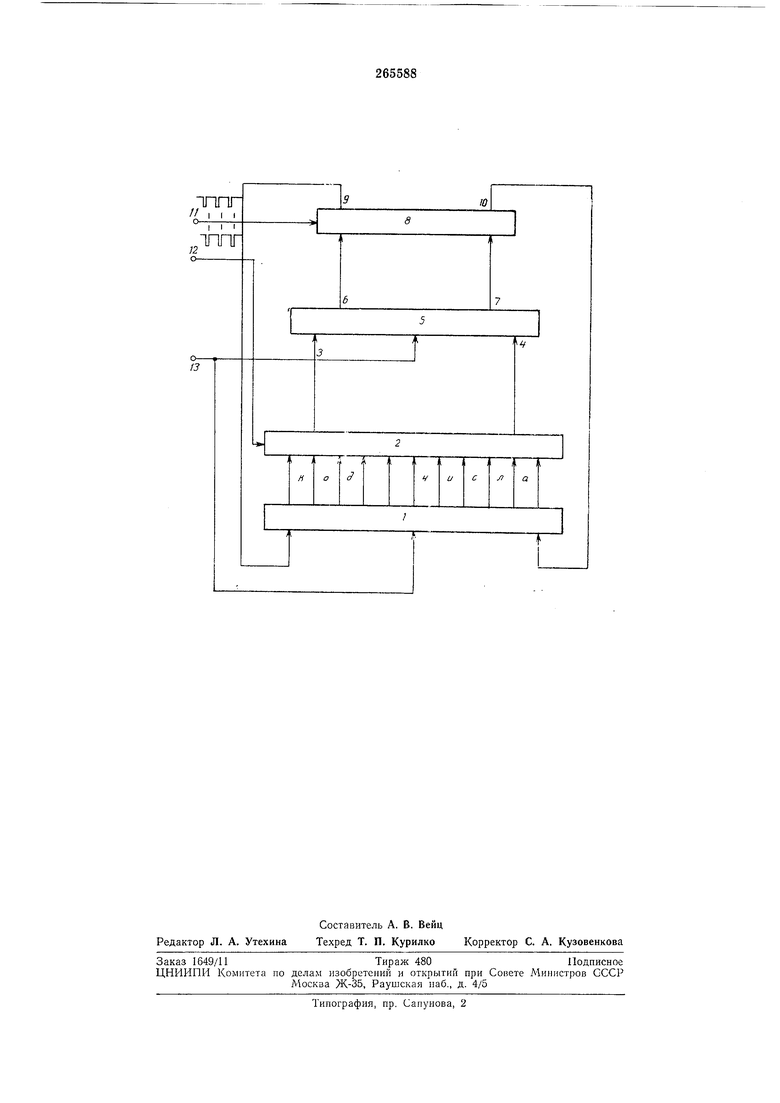

Схема устройства показана на чертеже.

Устройство содержит основной регистр 1, шифратор 2, с выхода 3 которого поступает двоичный код Номера переноса, а с выхода 4- сигнал «Сброс, регистр управления 5, с выхода 6 которого поступает код номера лереноса, а с выхода 7 - сигнал разрещения занесения единицы, дещифратор 8, с выхода 9 которого снимается сигнал единицы лереноса и сигнал «Сброс для разрядов основного регистра, предшествующих разряду, в который произведен перенос, а с выхода 10 - сигнал разрешения занесения единицы в младший разряд основного регистра.

ют основные счетные импульсы, на вход 12 - дополнительные счетные импульсы, сдвинутые по -времени относительно импульсов, приходящих на вход //. Подачей сигнала «Сброс -на вход 13 оба регистра устанавливаются в нулевое состояние. При этом регистр 5 выдает разрешение на занесение единицы в младший разряд регистра 1. Каждым нечетным основным импульсом в младший разряд регисгра

/ заносится единица, а каждым нечетным дополнительным импульсом шифратор 2 записывает в регистр 5 номер переноса в двоичном коде.

Каждый четный основной импульс через Дешифратор 8 согласно коду номера переноса, записанному .в регистре 5, осуществляет перенос и сброс разрядов регистра 1, предшествующих разряду, в который произощел перенос. Каждый четный дополнительный импульс

устанавливает регистр 5 в нулевое состояние, что разрешает занесение единицы в младший разряд основного регистра.

Предмет изобретения

Двоичный потенциальный счетчик, содержащий триггеры и потенциальные логические схемы, отличающийся тем, что, с целью уменьшения количества оборудования и повышения надежности, дополнительные триггеры объедц1ППП

//,,,

I I I

ттп

12

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ВРЕМЕННОГО ИНТЕРВАЛА | 1991 |

|

RU2040854C1 |

| ПАРАЛЛЕЛЬНЫЙ СУММАТОР-ВЫЧИТАТЕЛЬ В ТРОИЧНОЙ СИСТЕМЕ СЧИСЛЕНИЯ НА НЕЙРОНАХ | 2010 |

|

RU2453900C2 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ИНТЕРВАЛА ВРЕМЕНИ | 2004 |

|

RU2260830C1 |

| Программно-управляемый цифровой фильтр | 1985 |

|

SU1338006A1 |

| СЧЕТЧИК ИМПУЛЬСОВ | 2006 |

|

RU2308801C1 |

| Логический анализатор | 1986 |

|

SU1432527A1 |

| Интерполятор | 1984 |

|

SU1196895A1 |

| Цифровой преобразователь полярных координат в прямоугольные координаты | 1987 |

|

SU1441390A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1981 |

|

SU1013942A1 |

| Устройство для прерывания программ | 1978 |

|

SU736101A1 |

Даты

1970-01-01—Публикация