Изобретение относится к области цифровой вычислительной техники и автоматики. Известен счетчик импульсов (далее - объект), построенный на основе триггеров со счетным входом (См. И.Н.Букреев, Б.М.Мансуров и В.И.Горячев. Микроэлектронные схемы цифровых устройств. М.: «Сов. Радио», 1973, стр.137, рис.5.1). Недостатком этого объекта являются счетный триггер, который включает в себя элементы временной задержки счетных импульсов, что снижает быстродействие его работы, усложняет технологию изготовления триггера и повышает требования к формированию параметров счетных импульсов (крутизна фронта, длительность и другие параметры).

Известен также объект, выполненный на основе только трех логических элементов (ЛЭ) И, ИЛИ, НЕ, который устраняет недостатки приведенного выше устройства (см. там же, стр.135-150, рис.5.7). В названном объекте триггеры собраны на основе ЛЭ И-НЕ или ИЛИ-НЕ (RS-триггеры). Этот объект является ближайшим прототипом предлагаемого объекта.

Принятый за прототип объект содержит основной и вспомогательный регистры на основе RS-триггеров, логические элементы И, ИЛИ, НЕ и шину счетных импульсов, подключенную к первым входам первого и второго элементов И самого младшего разряда. Недостатками этого объекта являются: относительно низкое быстродействие, определяемое суммарным временем распространения максимального сквозного переноса и переключением двух RS-триггеров, значительным объемом оборудования, определяемым суммарным числом входов логических элементов (цена Квайна), сравнительно высоким потреблением электроэнергии и выполнением только одной операции счета импульсов.

Целью изобретения является устранение недостатков известных объектов, а именно: повышение быстродействия работы, расширение перечня выполняемых операций, снижение оборудования и потребления объектом электропитания.

Для этого предложен объект, выполненный на основа логических элементов И, ИЛИ, НЕ, отличающийся тем, что содержит в каждом разряде шины управления, информационную шину, четыре элемента И, три элемента ИЛИ, четыре элемента НЕ и RS-триггер, при этом выходы первого и второго элементов И через первый и второй элементы НЕ соединены с R- и S-входами RS-триггера соответственно, первый вход первого элемента И подключен к шине управления операциями счета, инвертирования и сдвига, второй вход первого элемента И соединен с выходом четвертого элемента НЕ, вход которого соединен с информационной шиной и вторым входом первого элемента ИЛИ, третий вход первого элемента И соединен с выходом четвертого элемента И и с входом третьего элемента НЕ, выход которого подключен к первому входу второго элемента И, второй вход второго элемента И соединен с выходом первого элемента ИЛИ, первый вход первого элемента ИЛИ соединен с шиной управления операцией инвертирования, а его третий вход подключен к выходу первого элемента И младшего разряда, выход первого элемента И является выходом импульсного переноса в старший разряд и соединен с первым входом второго элемента ИЛИ, второй вход которого соединен с шиной управления операцией логического умножения, а третий вход соединен с единичным выходом RS-триггера, выход второго элемента ИЛИ соединен с первым входом третьего элемента И, второй вход которого подключен к S-входу RS-триггера, выход третьего элемента И соединен с первым входом четвертого элемента И, второй вход которого подключен выходу третьего элемента ИЛИ, шина управления операциями инвертирования, сдвига, логического умножения и установки нуля подключена к первому входу третьего элемента ИЛИ, кроме того, в каждом нечетном разряде второй вход третьего элемента ИЛИ подключен к выходу потенциала переноса младшего разряда, выход третьего элемента ИЛИ соединен с третьим входом четвертого элемента И старшего разряда, а в каждом четном разряде второй вход третьего элемента ИЛИ соединен с выходом третьего элемента И младшего разряда, при этом в первый разряд счетчика импульсов введен четвертый элемент ИЛИ, выход которого является шиной управления операциями счета, инвертирования и сдвига, первый вход четвертого элемента ИЛИ является входом счетных импульсов и соединен с четвертым входом первого элемента ИЛИ, а второй вход четвертого элемента ИЛИ является входом импульсов сдвига и инвертирования, причем шина потенциального управления операциями счета и вычитания импульсов подключена к третьему входу третьего элемента ИЛИ первого разряда.

Предлагаемый объект позволяет повысить быстродействие работы, снизить число используемых логических элементов, расширить перечень выполняемых операций и снизить потребление электроэнергии.

1. Быстродействие выполнения операции счета импульсов в предлагаемом объекте достигается за счет исключения из цикла работы времени на переключение второго RS- триггера, который в предложенном объекте отсутствует. Если в прототипе суммарное время счета одного импульса равняется

Здесь n - число двоичных разрядов объекта; τ - временная задержка одного элемента И (ИЛИ, НЕ); tтр - время задержки переключения одного RS триггера; tи - длительность счетного импульса; tn - длительность паузы между импульсами. Полагаем, что 2nτ=tи, tп=tи, tтр=tи.

В предлагаемом объекте время счета одного импульса определяется таким соотношением:

Сравнивая соотношения (1) и (2), видим, что время счета одного импульса сократилось в 2 раза. Есть и еще одно преимущество объекта, которое состоит в том, что результат счета импульсов, зафиксированный в RS-триггерах после прихода каждого счетного импульса, появляется через время, разное tи, т.е. по истечении времени переключения одного триггера. В прототипе это время равно 3tи. (Заметим, что эта временная задержка прохождения информации при счете отдельного импульса аналогична т.н. «люфту» в механических счетчиках.) Указанное преимущество объекта также достигается тем, что сигнал потенциального переноса формируется во время паузы между счетными импульсами, а шина счетных импульсов подключена к первым входам первых элементов И всех двоичных разрядов.

2. Снижение суммарного числа входов логических элементов, т.е. снижение оборудования устройства, приблизительно на 15% определяется исключением из состава оборудования второго RS-триггера каждого разряда объекта.

3. Расширение перечня выполняемых операций (сдвиг «единичных» кодов, инвертирование триггеров, вычитание импульсов, прием кода единиц во все разряды, логическое сложение, логическое умножение) достигается за счет введения в состав оборудования объекта трех элементов ИЛИ и шести шин управления выполнением этими операциями. Операция сдвига кода отдельных единиц (101001...) позволяет использовать объект как распределитель импульсов, т.е. последовательное переключение триггеров и выдачу соответствующих потенциалов для управления другими электронными устройствами, блоками, схемами. Эта операция выполняется за счет включения в состав оборудования объекта первого элемента ИЛИ и шины управления выполнения операцией логического умножения. Операция инвертирования кодов счетчика позволяет выработать управляющий потенциал на входах первого и второго элементов И с помощью схемы сквозного переноса и произвести инвертирование триггеров. Эта операция выполняется за счет использования третьего элемента ИЛИ и соответствующих шин управления.

4. Уменьшение потребления электроэнергии достигается за счет исключения из состава оборудования одного RS-триггера. В прототипе в каждом двоичном разряде потребляемый ток равен 2I (I - ток открытого элемента НЕ). В предлагаемом объекте в зависимости от наличия или отсутствия сигнала переноса в каждом разряде суммарный ток может быть равен 2I или I. Среднее значение 1.5 I, т.о. имеет место снижение потребляемого тока.

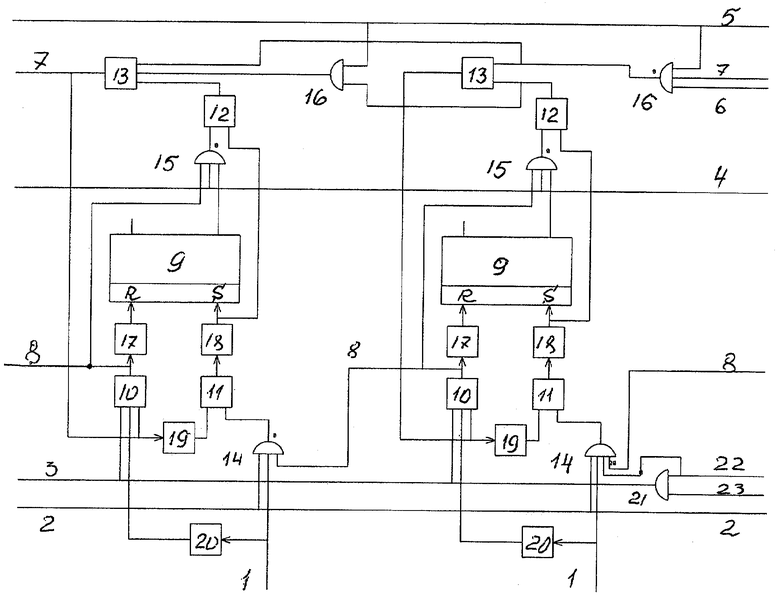

Для пояснения работы предлагаемого объекта на чертеже приведена функциональная схема его двух двоичных разрядов. На схеме приняты следующие обозначения: 1 - информационная шина; 2 - шина управления (ШУ) операцией инвертирования; 3 - ШУ операциями счета, инвертирования и сдвига; 4 - ШУ операцией логического умножения; 5 - ШУ операциями инвертирования, сдвига, логического умножения и установки нуля; 6 - ШУ операциями счета и вычитания импульсов (потенциальное управление); 7 - выход потенциала переноса из четного разряда в нечетный разряд; 8 - выход импульса переноса в старший разряд; 9 - RS-триггер; 10-13 - элементы И; 14-16, 21 - элементы ИЛИ; 17-20 - элементы НЕ; 22 - вход счетных импульсов; 23 - вход импульсов сдвига, инвертирования и установки нуля.

Предложенный объект осуществляется следующим образом. В каждом разряде счетчика первые входы И 10 подключены к ШУ 3, вторые входы связаны с выходом НЕ 20, третьи входы соединены с входом НЕ 19 и выходом И 13, выход элемента И 10 соединен с входами НЕ 17, ИЛИ 15 i-того разряда и с входом ИЛИ 14 i+1-го разряда, выход НЕ 17 подключен к R-входу триггера 9. Первый вход И 12 соединен с выходом НЕ 18, вход которого соединен с выходом И 11. Второй вход И 12 соединен с выходом ИЛИ 15, второй и третий входы ИЛИ 15 подключены к ШУ 4 и к единичному выходу триггера 9. Выход И 12 соединен с первым входом И 13. Выход НЕ 18 подключен к S-входу триггера 9. Первый вход ИЛИ 16 соединен ШУ 5, выход этого элемента подключен к второму входу И 13. Входы ИЛИ 14 соединены с ШУ 2, информационной шиной 1 и с входом НЕ 20, выход ИЛИ 14 соединен с входом И 11. Выход НЕ 19 соединен с входом И 11. В каждом нечетном разряде второй вход ИЛИ 16 соединен с шиной 7. В каждом четном разряде второй вход ИЛИ 16 соединен с выходом И 12 младшего разряда. Третий вход И 13 соединен с выходом ИЛИ 16 нечетного (младшего) разряда. В первом разряде входы 22 и 23 подключены к входам ИЛИ 21, выход которого является ШУ 3. Вход 22 соединен с четвертым входом ИЛИ 14. В исходном положении (в статике) триггеры счетчика установлены в «нуль». На ШУ 2, 3, 4, 5, 6 на входах 22, 23 и на входе 1 отсутствуют высокие потенциалы. На выходах элементов НЕ 17, 18, 19 и 20 присутствуют высокие (разрешающие) потенциалы.

Рассмотрим принцип работы объекта при выполнении всего перечня выполняемых операций.

1. Операция счета импульсов. Операция выполняется за два временных такта t1 и t2. По t1 формируется потенциал сквозного переноса. По t2 формируется результат суммы импульсов и занесение его в триггер 9. Для выполнения операции на ШУ 6 подается высокий потенциал, который сохраняется до окончания счета (вычитания) импульсов. До прихода первого счетного импульса (СИ) переносы ни в одном разряде не вырабатываются, т.к. триггер 9 первого разряда находится в нулевом состоянии. Счетный импульс в первом разряде по цепи вход 22, ИЛИ 21, 14, ШУ 3 поступает на входы И 10, 11. Т.к. на первом входе И 11 присутствует высокий потенциал, то СИ через И 11, НЕ 18 поступает на S-входы триггера 9, устанавливает триггер в единицу и запрещает работу И 12 на время, равное длительности импульса. После окончания действия СИ высокие потенциалы с выходов триггера 9 и НЕ 18 выработают высокий потенциал на выходе И 12, который через И 13 поступит на входы И 10, НЕ 19 первого разряда и через ИЛИ 16 поступит на второй вход И 13 второго разряда. При этом высокий потенциал с ШУ 6 через ИЛИ 16 поступает на вход И 13 первого разряда и на третий вход И 13 вход старшего разряда. Второй СИ по цепи вход 22, ИЛИ 21, ШУ 3, И 10, НЕ 17 поступит на R-вход триггера 9, установит его в нуль и через ИЛИ 15 будет «поддерживать» высокий потенциал с выходом И 12 до прекращения СИ. Одновременно этот же импульс с выхода И 10 первого разряда по цепи ИЛИ 14, И 11, НЕ 18 поступит на S-вход триггера 9 второго разряда, установит его в единицу и будет запрещать работу И 12 этого разряда на время длительности СИ. Третий СИ установит триггер 9 первого разряда в единицу. По истечении времени, равного длительности СИ, с выхода И 12 через ИЛИ 16 на второй вход И 13 поступит высокий потенциал. Теперь на всех входах И 13 второго разряда присутствуют высокие потенциалы, что обеспечивает прохождение сигнала переноса в третий разряд объекта, а элементы И 10 первого и второго разрядов будут подготовлены для прохождения четвертого СИ на R-входы триггеров 9 первого и второго разрядов. Четвертый СИ установит эти триггеры в нуль, а триггер 9 третьего разряда - в единицу. При этом условия распространения потенциала переноса не будут меняться, т.к. импульсы с выходов И 10 первого и второго разрядов через ИЛИ 15, НЕ 12 будут «поддерживать» условия выработки переноса в этих разрядах. Отметим, что рассмотренная операция (базовая операция) осуществляется только на основе одного RS-триггера, а временная задержка сигнала переноса в нечетных разрядах определяется одним элементом ИЛИ 16, а в четных разрядах - одним элементом И 13. Это обеспечивает снижение оборудования и повышение быстродействия работы объекта.

2. Операция инвертирования кода. Положим, в двух разрядах счетчика хранится код «10». Потенциал операции инвертирования подается на ШУ 5. Исполнительный импульс инвертирования кода подается одновременно на ШУ 22 и 2. В первом разряде триггер 9 хранит код «нуля», т.е. на первом входе И 11 будет высокий потенциал. Исполнительный импульс по цепи вход 22, ИЛИ 14, И 11, НЕ 18 поступит на S-вход триггера 9 и установит его в единицу. Во втором разряде в триггере 9 хранится код единицы, т.е. на выходе И 13 будет высокий потенциал, разрешающий прохождение импульса с ШУ 3 по цепи И 10, НЕ 17 на R-вход триггера 9. Исполнительный импульс установит триггер 9 в нуль. Таким образом, в триггерах первого и второго разрядов будет храниться код «01», т.е. инверсный код. Для выполнения этой операции требуется увеличить оборудование каждого разряда на три входа элементов ИЛИ (ИЛИ 14, 16).

3. Операция вычитание импульсов. Операция выполняется аналогично операции сложения. Отличие состоит в том, что до начала и после ее выполнения необходимо выполнить операцию инвертирования кодов, хранящихся в триггерах 9. Операция не требует дополнительного оборудования.

4. Операция сдвига «отдельных» единиц влево (в сторону старших разрядов). Под кодом «отдельных» единиц определяют любые двоичные коды, в которых каждая единица отделена от остального кода нулями слева и справа, например 010010, 1010010, 01000... и т.д. Данная операция используется в цифровых устройствах как операция последовательного распределения импульсов (потенциалов) по n каналам (n - число разрядов объекта). Сдвиг кода на один разряд влево выполняется за два временных такта. Тактами являются импульс сдвига и пауза между этими импульсами. Максимальное время выполнения операции 2 ntи (tи - длительность импульса и паузы между импульсами. Полагаем, что tn=tп.). Допустим, в исходном положении в первый разряд счетчика занесен код единицы. Во всех остальных разрядах триггеры 9 хранят код нуля. Признаком выполнения операции сдвига кодов отдельных единиц является потенциал, поступивший на ШУ 5. В тех разрядах, в которых хранится код единицы, потенциал с ШУ 5 по цепи ИЛИ 16, И 13 поступает на вход И 10 и НЕ 19. Импульс сдвига, поступивший по входу 23, ИЛИ 21 на ШУ 3 и далее по цепи элементов И 10, НЕ 17, R-вход триггера 9, установит его в нуль. Одновременно этот же импульс по цепи ИЛИ 15, И 12 будет "поддерживать" потенциал на первом входе И 13 и поступит в первый старший разряд, где через ИЛИ 14, И 11, НЕ 18 установит триггер 9 в единицу. Таким образом, код единицы будет сдвинут на один разряд влево. (Для выполнения этой операции не требуется дополнительного оборудования.) Операция будет выполняться до тех пор, пока на вход 23 будут поступать импульсы сдвига. При этом если выход 8 самого старшего разряда будет соединен с входом 8 самого младшего разряда, то будет выполняться циклический сдвиг кода.

5. Операция логического сложения. Выполняется за два временных такта. По t1 на информационную шину 1 поступает код второго слагаемого. Выработанный на выходе ИЛИ 14, И 11 импульс через НЕ 18 поступит на S-вход триггера и установит его в единицу. Если на шине 1 отсутствует высокий потенциал, то состояние триггера не меняется. Второй такт (пауза) используется для подготовки выполнения последующей операции. Для выполнения логического сложения не требуется дополнительного оборудования.

6. Операция логического умножения. Выполняется за два временных такта (t1 и t2). На время выполнения операции на ШУ 4, и 5 поступают управляющие потенциалы. На информационной вход 1 - код числа второго сомножителя. По t1 на вход 23, ИЛИ 21, ШУ 3 подается исполнительный импульс. Если код второго сомножителя i-того разряда равен единице, то исполнительный импульс не проходит на R-вход триггера 9, т.к. низкий потенциал с выхода НЕ 20 запрещает его прохождение через И 10. Во всех остальных случаях триггер устанавливается в нуль или сохраняет это состояние. Второй такт используется для подготовки устройства к выполнению следующих операций. Для выполнения логического умножения требуется дополнительно три входа элементов И, ИЛИ, НЕ.

7. Операция приема кода. Устройство позволяет выполнить три модификации приема кода: прием прямого кода с предварительной установкой триггеров 9 в нуль, прием кода единиц во все разряды одновременно и прием прямого кода с предварительной установкой всех триггеров в единицу. Первая модификация приема кода выполняется при поступлении на информационный вход 1 высокого потенциала, соответствующего коду единице. При этом сигнал проходит по цепи элементов ИЛИ 14, И 11, НЕ 18, поступает на S-вход триггера 9 и устанавливает его в единицу. Прием всех единиц в триггеры 9 (вторая модификация) выполняется за счет подачи исполнительного импульса на ШУ 2. Третья модификация приема кода в триггеры с информационных входов выполняется за два такта (t1, t2). По первому такту все триггеры 9 устанавливаются в единицу. По t2 одновременно на информационный вход поступает принимаемый код, а на ШУ 4, 5, 3 - высокие потенциалы. При этом триггеры тех разрядов, на информационных входах которых отсутствуют высокие потенциалы, будут установлены в нуль. В этих разрядах исполнительный импульс по цепи ШУ 3, И 10, НЕ 17 поступит по R-входу и установит триггеры в нуль. Операция приема кода не требует дополнительного оборудования.

8. Операция установки всех триггеров в нуль. Для ее выполнения на ШУ 5 подается высокий потенциал, а на вход 23 и на ШУ 3 - исполнительный импульс. Если триггер i-того разряда хранит код единицы, то управляющий потенциал по цепи ШУ 5, И 16, И 13 поступает на третий вход И 10, а на второй вход этого элемента поступает высокий потенциал с НЕ 20. Исполнительный импульс по цепи ШУ 3, И 10, НЕ 17. поступит на R-вход триггера и установит его в нуль. Для выполнения этой операции не требуется дополнительного оборудования (экономится один вход элемента ИЛИ в каждом разряде).

Таким образом, предлагаемый объект обеспечивает повышение быстродействия работы устройства в 1,5 раза, расширяет перечень выполняемых операций в восемь раз, снижает потребление электропитания при минимальных затратах аппаратурных средств, по сравнению с прототипом. Суммарное число входов логических элементов одного разряда равно 28, в среднем на одну выполняемую операцию требуется около 3.5 входов (цена Квайна).

| название | год | авторы | номер документа |

|---|---|---|---|

| СУММАТОР НАКАПЛИВАЮЩЕГО ТИПА | 2004 |

|

RU2278411C1 |

| НАКАПЛИВАЮЩИЙ СУММАТОР | 2005 |

|

RU2288501C1 |

| УСТРОЙСТВО СУММИРОВАНИЯ ДВОИЧНЫХ КОДОВ | 2008 |

|

RU2381547C2 |

| КОМБИНАЦИОННО-НАКАПЛИВАЮЩИЙ СУММАТОР | 2006 |

|

RU2306596C1 |

| СЧЕТЧИК ИМПУЛЬСОВ | 2004 |

|

RU2284653C2 |

| СЧЕТЧИК ИМПУЛЬСОВ | 2010 |

|

RU2419200C1 |

| СЧЕТЧИК ИМПУЛЬСОВ | 2005 |

|

RU2284654C2 |

| СЧЕТНЫЙ ТРИГГЕР | 2007 |

|

RU2360356C2 |

| СУММАТОР КОМБИНАЦИОННОГО ТИПА | 2004 |

|

RU2275676C1 |

| КОМБИНАЦИОННО-НАКАПЛИВАЮЩИЙ СУММАТОР | 2005 |

|

RU2292073C1 |

Изобретение может быть использовано в цифровой вычислительной технике. Технический результат - повышение быстродействия вычислений, расширение функциональных возможностей, экономия электропитания при минимальных затратах оборудования. Счетчик выполняет операции счета и вычитания импульсов, инвертирование кода, сдвига кода "отдельных" единиц, логического сложения и умножения, параллельного приема кода в триггеры, остановку в нуль всех триггеров. Каждый разряд счетчика содержит один RS-триггер, четыре элемента И, три элемента ИЛИ, четыре элемента НЕ, четыре шины управления и информационный вход. Особенностью счетчика является формирование потенциала переноса до прихода счетного импульса, построение схемы переноса и построение каждого разряда только на основе одного RS-триггера. Суммарное число входов логических элементов одного разряда равно 28, в среднем на одну выполняющую операцию требуется около 3.5 входов (цена Квайна). 1 ил.

Счетчик импульсов, выполненный на основе логических элементов И, ИЛИ, НЕ, отличающийся тем, что содержит в каждом разряде шины управления, информационную шину, четыре элемента И, три элемента ИЛИ, четыре элемента НЕ и RS-триггер, при этом выходы первого и второго элементов И через первый и второй элементы НЕ соединены с R- и S-входами RS-триггера, соответственно, первый вход первого элемента И подключен к шине управления операциями счета, инвертирования и сдвига, второй вход первого элемента И соединен с выходом четвертого элемента НЕ, вход которого соединен с информационной шиной и вторым входом первого элемента ИЛИ, третий вход первого элемента И соединен с выходом четвертого элемента И и с входом третьего элемента НЕ, выход которого подключен к первому входу второго элемента И, второй вход второго элемента И соединен с выходом первого элемента ИЛИ, первый вход первого элемента ИЛИ соединен с шиной управления операцией инвертирования, а его третий вход подключен к выходу первого элемента И младшего разряда, выход первого элемента И является выходом импульсного переноса в старший разряд и соединен с первым входом второго элемента ИЛИ, второй вход которого соединен с шиной управления операцией логического умножения, а третий вход соединен с единичным выходом RS-триггера, выход второго элемента ИЛИ соединен с первым входом третьего элемента И, второй вход которого подключен к S-входу RS-триггера, выход третьего элемента И соединен с первым входом четвертого элемента И, второй вход которого подключен к выходу третьего элемента ИЛИ, шина управления операциями инвертирования, сдвига, логического умножения и установки нуля подключена к первому входу третьего элемента ИЛИ, кроме того, в каждом нечетном разряде второй вход третьего элемента ИЛИ подключен к выходу потенциала переноса младшего разряда, выход третьего элемента ИЛИ соединен с третьим входом четвертого элемента И старшего разряда, а в каждом четном разряде второй вход третьего элемента ИЛИ соединен с выходом третьего элемента И младшего разряда, при этом, в первый разряд счетчика импульсов введен четвертый элемент ИЛИ, выход которого является шиной управления операциями счета, инвертирования и сдвига, первый вход четвертого элемента ИЛИ является входом счетных импульсов и соединен с четвертым входом первого элемента ИЛИ, а второй вход четвертого элемента ИЛИ является входом импульсов сдвига и инвертирования, причем шина потенциального управления операциями счета и вычитания импульсов подключена к третьему входу третьего элемента ИЛИ первого разряда.

| Накапливающий сумматор | 1985 |

|

SU1291968A1 |

| SU 1292479 A1, 07.10.1986 | |||

| Накапливающий сумматор | 1987 |

|

SU1418705A1 |

| Счетчик импульсов | 1986 |

|

SU1422404A1 |

| US 4991186, 05.02.1991 | |||

| БУКРЕЕВ И.Н | |||

| и др | |||

| Микроэлектронные схемы цифровых устройств | |||

| - М.: Сов | |||

| радио, 1973, с.137, рис.5.1. | |||

Авторы

Даты

2007-10-20—Публикация

2006-02-15—Подача