Изобретение относится к области вычислительной техники и предназначено для выполнения операции вычитания чисел.

Известно использование для выполнения операции вычитания цифро-аналоговых устройств, содержащих статические регистры и счетчики, объем оборудования в которых растет пропорционально увеличению числа разрядов.

Предлагаемое устройство отличается тем, что в нем установлены регистры и счетчик динамического типа на магиитострикциоииых линиях задержки с общей -выходной цепью для выделения сигналов перехода из нуля в единицу во всех разрядах счетчика и схемой унравления процессом вычитания на динамическом счетчике, на вход которого подается унитарный код, а выход соединен со схемой выделения сигналов перехода из нуля в единицу. Эте позволяет уменьшить количество оборудования. Для однократной передачи сигналов перехода по каждому разряду числа выход схемы выделения сигналов перехода соединен с логической схемой управления этого регистра через инвертор.

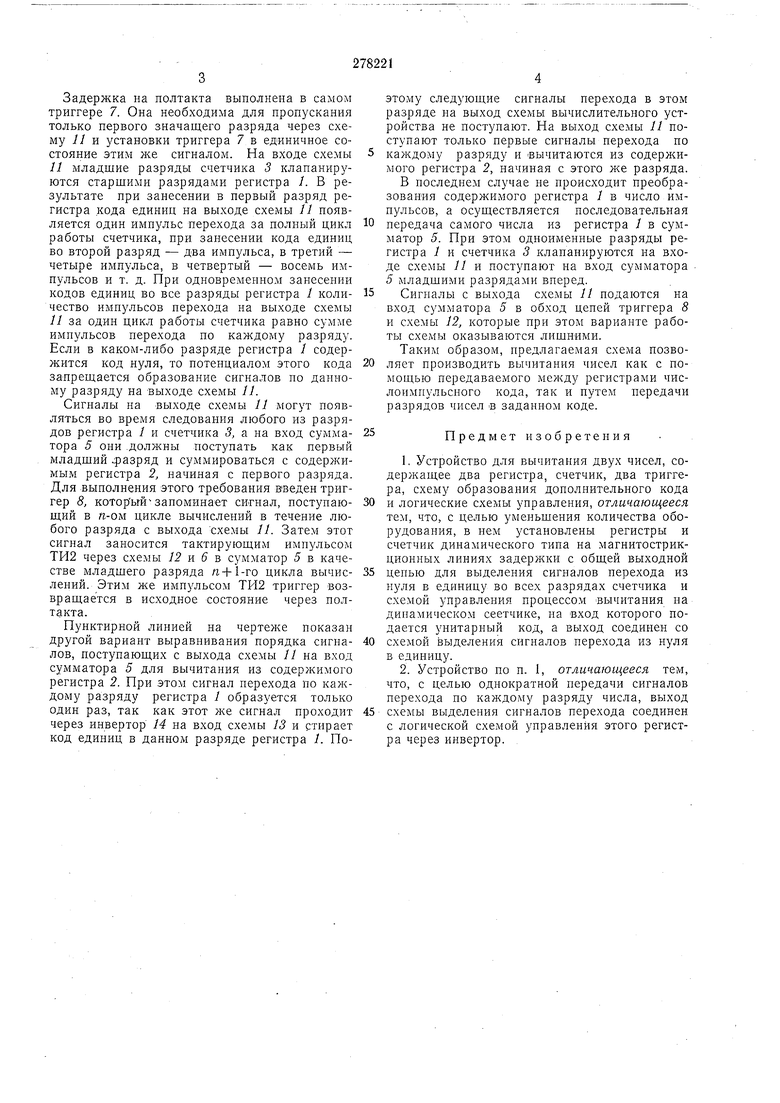

Схема описываемого устройства изображена на чертеже.

ння дополнительного кода, триггеры 7 и 8, схемы 9-13 совпадения и инвертор 14.

Перед выполнением операции вычитания в регистр / через схему 9 совпадения заносится вычитаемое. Уменьшаемое заносится через схему 13 в регистр 2. После занесения чисел потенциалом длительности цикла вычислений по входу 15 разрешается счет импульсов ТИ1, поступающих с входа 16 в счетчик 3 через схему 10 совпадения. Потенциалы с -выходов регистра 1, счетчика 3 и триггера 7 подаются на вход схемы 11. При совпадении иизких уровней (кодов единиц) этих сигналов на выходе схемы // также появляются сигналы, количество которых равно числу, занесенному в регистр 1. Сигналы перехода с выхода схемы 11 через триггер 8 и схемы 12 и 6 поступают на вход сумматора 5 и складываются с содержимым регистра 2. В результате в нем образуется разность двух чисел. Па входы 17 и 18 схем 9 W. 13 подаются сигналы записи и стирания.

Схема 11 пропускает только первый значащий разряд содержимого счетчика 3, так как этим же сигналом, задержанным на полтакта, триггер 7 переводится в единичное состояние, и его потенциалом запрещается образование сигнала на выходе схемы // до установки триггера 7 в нуль очередным сигналом ТИ2, поступающим на вход 19 перед каждым ТИ1,

Задержка на полтакта выполнена в самом триггере 7. Она необходима для пропускания только первого значащего разряда через схему 11 и установки триггера 7 в единичное состояние этим же сигналом. На входе схемы 11 младшие разряды счетчика 3 клапанируются старшими разрядами регистра /. В результате при занесении в первый разряд регистра кода единиц на выходе схемы И появляется один импульс перехода за полный цикл работы счетчика, при занесении кода единиц во второй разряд - два импульса, в третий - четыре импульса, в четвертый - восемь импульсов и т. д. При одновременном занесении кодов единиц во все разряды регистра I количество импульсов перехода иа выходе схемы // за один цикл работы счетчика равно сумме импульсов перехода по каждому разряду. Если в каком-либо разряде регистра / содержится код нуля, то потенциалом этого кода запрещается образование сигналов по данному разряду на выходе схемы 11.

Сигналы на выходе схемы 11 могут появляться во время следования любого из разрядов регистра / и счетчика 3, а на вход сумматора 5 они .должны поступать как первый младший .разряд и суммироваться с содержимым регистра 2, начиная с первого разряда. Для выполнения этого требования введен триггер 8, которыйзапоминает сигнал, поступающий в п-ом цикле вычислений в течение любого разряда с выхода схемы 11. Затем этот сигнал заносится тактирующим импульсом ТИ2 через схемы 12 н 6 в сумматор 5 в качестве младшего разряда я+1-го цикла вычислений. Этим же импульсом ТИ2 триггер возвращается в исходное состояние через полтакта.

Пунктирной линией на чертеже показан другой вариант выравнивания порядка сигналов, поступающих с выхода схемы // на вход сумматора 5 для вычитания из содержимого регистра 2. При этом сигнал перехода по каждому разряду регистра 1 образуется только один раз, так как этот же сигнал проходит через инвертор 14 на вход схемы 13 и стирает код единиц в данном разряде регистра 1. Поэтому следующие сигиалы перехода в этом разряде на выход схемы вычислительного устройства не поступают. На выход схемы // поступают только первые сигналы перехода по

каждому разряду и -вычитаются из содержимого регистра 2, начиная с этого же разряда. В последнем случае не происходит преобразования содержимого регистра / в число импульсов, а осуществляется последовательная

передача самого числа из регистра 1 в сумматор 5. При этом одноименные разряды регистра 1 и счетчика 3 клапанируются на входе схемы 11 и поступают на вход сумматора 5 младшими разрядами вперед.

Сигналы с выхода схемы 11 подаются на вход сумматора 5 в обход цепей триггера 8 и схемы 12, которые при этом варианте работы схемы оказываются лишними. Таким образом, предлагаемая схема позволяет производить вычитания чисел как с помощью передаваемого между регистрами числоимпульсного кода, так и путем передачи разрядов чисел в заданном коде.

Предмет изобретения

1.Устройство для вычитания двух чисел, содержащее два регистра, счетчик, два триггера, схему образования дополнительного кода

и логические схемы управления, отличающееся тем, что, с целью уменьшения количества оборудования, в нем установлены регистры и счетчик дииамического типа на магнитострикционных линиях задержки с общей выходной

цепью для выделения сигналов перехода из нуля в единицу во всех разрядах счетчика и схемой управления процессом вычитания на динамическом сеетчике, на вход которого подается унитарный код, а выход соединен со

схемой выделения сигналов перехода из нуля в единицу.

2.Устройство ио п. 1, отличающееся тем, что, с целью однократной передачи сигналов перехода по каждому разряду числа, выход

схемы выделения сигналов перехода соединен с логической схемой управления этого регистра через инвертор.

l-TTl

ТИ2

| название | год | авторы | номер документа |

|---|---|---|---|

| СПЕЦИАЛИЗИРОВАННОЕ ЦИФРОВОЕ ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО | 1973 |

|

SU408304A1 |

| ВЫЧИСЛИТЕЛЬНЫЙ ЭЛЕМЕНТ ДЛЯ ЦИФРОВЫХ ВЫЧИСЛИТЕЛЬНЫХ УСТРОЙСТВ | 1970 |

|

SU267188A1 |

| Устройство для деления п-разрядных десятичных чисел | 1976 |

|

SU742933A1 |

| ЭЛЕКТРОННАЯ КЛАВИШНАЯ ВЫЧИСЛИТЕЛЬНАЯ МАШИНА | 1973 |

|

SU395837A1 |

| Устройство квантованной временной задержки импульсных сигналов | 1979 |

|

SU866721A1 |

| Устройство для деления десятичных чисел | 1982 |

|

SU1048473A1 |

| Устройство для сортировки | 1989 |

|

SU1661756A1 |

| Устройство для деления десятичных чисел | 1976 |

|

SU744562A1 |

| Преобразователь двоичного кода в двоично-десятичный код угловых единиц | 1986 |

|

SU1349008A2 |

| Цифровой интегратор | 1975 |

|

SU661572A1 |

Авторы

Даты

1970-01-01—Публикация