Изобретение относится к цифровой .вычислительной технике и может найти применение при создании электронных цифровых вычислительных машин.

Известны специализированные цифровые вычислительные устройства, лостроенные на регистрах и счетчиках, содержащие схему управления и логические схемы.

Однако известные устройства имеют недостаточно широкие функциональные возможности.

Целью изобретения является расширение функциональных возможностей устройства.

Для этого оно содержит переменную структуру на динамических регистрах и счетч«ках, логических схемах и вычислительном элементе, схема выделения сигнала перехода которого через программно-управляемые логические схемы соединена со вторыми входами сумматоров двух счетчиков регистров выполнения операций и через схемы совпадения и схемы разделения соединены с выходом счетчика переходов, соединенным со вторым входом схемы выделения сигналов перехода, выход первого регистра операций через схему совпадекия и схему разделения соединен с первым входом схемы выделения сигналов перехода, выход второго регистра соединен через схему совпадения и триггер со входом счетчика переходов, первый регистр через схему разделения соединен с первым входом схемы выделения сигналов перехода.

Вычислительный элемент, построенный на основе использования свойств двоичных счетчиков- изменять значение содержимого счетчика из «О в «1 только в одном первом значащем разряде, позволяет применять вместо статических регистров - динамические, с количеством оборудования в них, не зависящим от разрядности чисел. Применение вычислительного элемента позволяет, в принципе, любой практической схеме на статических элементах составить эквивалентный функциональный аналог на динамических элементах, а также комбинировать эти элементы для создания вычислительных устройств с переменной структурой (последовательной, параллельной, последовательно-параллельной), обладающих возможностью работы с требуемым быстродействием, разрядностью, алгоритмическими данными, системой счисления и наименьщим количеством оборудования по сравнению с известными вычислительными устройствами, предназначенными для решения этого же класса задач.

Изобретение пояснено чертел ами.

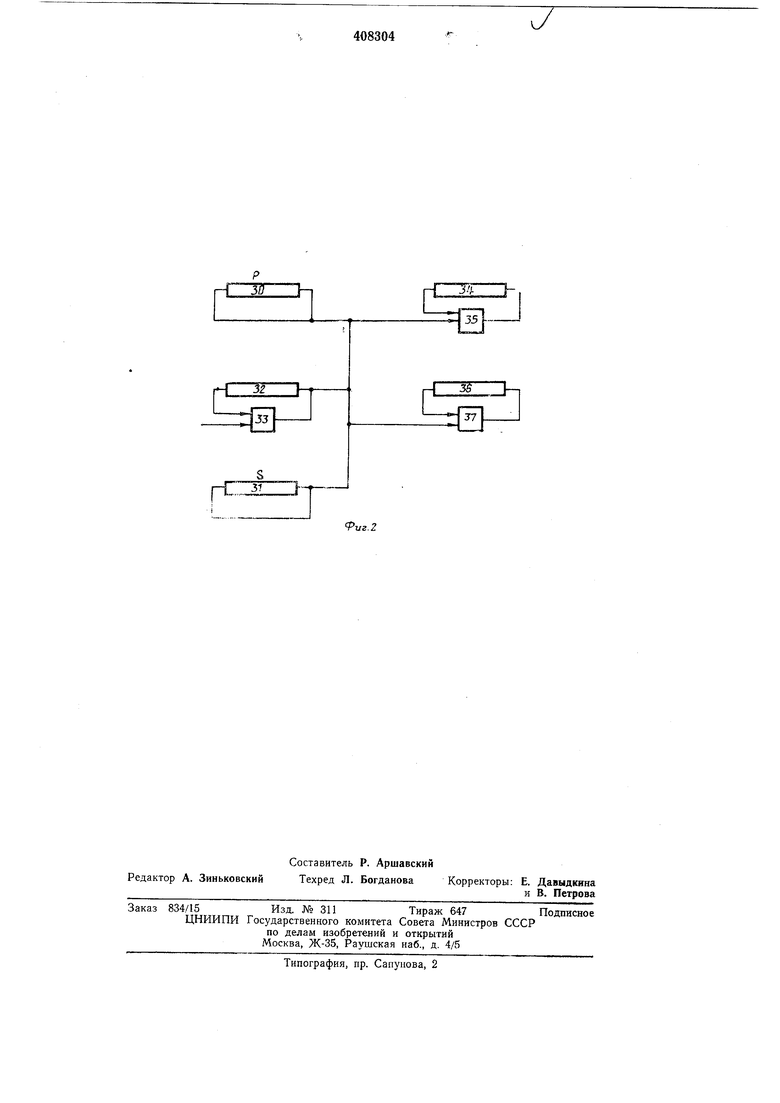

На фиг. 1 приведена блок-схема вычислительного устройства; на фиг. 2 - пример организации вычислительного устройства по принципу построения цифровых аналогов.

Специализированное цифровое вычислительное устройство (СЦВУ) содержит регистр 1, счетчик переходов 2, сумматор 3, схемы совпадения 4 и 5, схему выделения сигналов перехода (СВСП) 6, включающую в свой состав триггеры 7 iH 8 и схемы совпадения 9 и 10.

Триггер 7 И схема совпадения 9 выполняют функцию выделения выходных сигналов. Триггер 8 и схема совпадения 10 выполняют функцию запоминаиня импульса на один такт. Регистр 1, счетчик переходов 2, сумматор 3, схемы совпадения 4, 5, триггер 7 и схема совпадения 9 представляют собой вычислительный элемент.

Сумматор 11, регистр 12 на магнитострикционной линии задержки и схема совпадения 13 в совокупности представляют собой первый счетчик-регистр операций.

Второй счетчик-регистр собран на схеме совпадения 14, регистр 15 на магнитострикционной линии задержки и сумматоре 16.

Кроме того, устройство содержит схему совпадения 17, триггер 18, схемы совпадения 19-24, схемы разделения 25-27, представляющие собой в совокупности блок управления, схему тактирующих импульсов 28 и схему 29 получения потенциалов разрядов PI-

71+1Схема организации СЦВУ по принципу построения цифровых аналогов (фиг. 2) в своем составе содержит регистры исходных данных 30 и 31, счетчики-регистры 32, 33, 34, 35 и 36,

37« две схемы выделения сигналов перехода, аналогичные схеме 6.

Вычислительный элемент через схему выделения сигналов перехода из «О в «I (выход схемы 9) соединен со схемой синхронизации (триггер 8 и схему 10) этих сигналов с первыми разрядами чисел в регистрах 12 или 15. С выхода Схемы совпадения 10 сигналы перехода поступают через схемы 20-22 на вторые входы сумматоров 11 или 16 для сложения, соответственно, с числом в регистре 12 или 15. На эти же входы сумматоров могут поступать сигналы переполнения с выхода счетчика 2 через схемы совпадения 19 и 23.

Сигналы переполнения, возникающие на выходе регистра 15, поступают через схему совпадения 17 и триггер 18 на -вход схемы 5 и прекращают процесс вычисления. Счетчик переходов 2 подсчитывает поступающие на вход

38тактирующие импульсы (ТИ) в унитарном коде. По сигналам перехода этого счетчика производится управление процессом вычисления.

В регистры 1, 12, 15 заносятся исходные данные, а в регистре 12 образуются результаты вычислений. Потенциалы кодов операций

(/), :(П +W.вручную или автоматически подаются «а входы схем совпадения 19-24 и 39, в результате чего устанавливается необходимая структура схемы для выполнения этой операции.

У

408304

Устройство работает следующим образом. Сложение чисел. Перед выполнением операции сложения в регистр 1 через схему совпадения 4 заносят одно из слагаемых. Вто5 рое слагаемое заносят через схему совпадения 13 в регистр 12. Потенциал кода операции сложения подается на первый вход схемы 21. После занесения слагаемых потенциалом «длительность цикла вычислений на входе 40 10 разрешается счет импульсов ТИ 1, поступающих в сумматор 3 через схему совпадения 5 с периодом следования Т. Потенциалы с выходов регистра 1, сумматора 3 и нулевого плеча триггера 7 подаются на вход схемы совпа15 дения 9. Код числа с регистра 1 поступает старщими разрядами вперед, а код с сумматора 3 - младщими разрядами вперед. При совпадении низких уровней (кодов единиц) этих сигналов на входе схемы совпадения 9 20 на ее выходе появляются сигналы перехода, количество .которых равно числу, занесенному в регистр 1. Эти сигналы через триггер 8 и схемы 10 и 21 поступают на вход сумматора 11 и складываются с содержимым регистра 12. 25 В результате в нем образуется сумма двух слагаемых.

Схема 9 пропускает только первый значащий разряд содержимого счетчика переходов 2, так как этим же сигналом 41, задержанным 0 на полтакта (Т/2), триггер 7 переводится в единичное состояние. Потенциалом с нулевого выхода триггера 7 запрещается образование сигналов на выходе схемы 9 до установки триггера 7 в нуль очередным сигналом ТИ2, 5 поступающим перед каждым сигналом ТИ1. Задержка на полтакта выполнена в самом триггере 7, она необходима для пропускания только первого значащего разряда. На входе схемы 9 младщие разряды счетчика пере0 ходов 2 клапанируются старшими разрядами регистра 1. В результате, при занесении в первый разряд регистра 1 кода 1 на выходе схемы 9 появляется один импульс перехода за полный цикл работы счетчика, при занесении 5 кода 1 во второй разряд - два импульса, в третий разряд - четыре импульса, в четвертый разряд - восемь импульсов и т. д. При одновременном занесении кодов единиц во все разряды регистра 1 количество импульсов 0 перехода на выходе схемы 9 за один цикл работы счетчика переходов равно сумме импульсов перехода по каждому разряду. Если в каком-либо разряде регистра 1 содержится код «О, то потенциалом этого кода запрещается 5 образование сигналов по данному разряду на выходе схемы 9.

Сигналы на выходе схемы 9 появляются в любом из разрядов в период п-го цикла вычислений. В сумматоре 11 они должны сум0 мироваться с содержимым регистра 12, начиная с первого младщего разряда. Это возможно только в («+1) цикле. Для временного согласования введен триггер 8, запоминающий сигнал, который поступает в течение любого разряда с выхода схемы 9 в п-ом цикле

вычислений. Затем этот сигнал через схему 21 по ТИ 1 заносится в сумматор 11, где происходит суммирование с первым младшим разрядом второго слагаемого. Сигналом ТИ2 с задержкой на полтакта триггер 8 возвращается в исходное состояние.

Возможен также другой вариант выравнивания порядка сигналов, поступающих с выхода схемы 9 «а вход сумматора И для суммирования с содержимым регистра 12, сущность которого состоит в том, что сигнал перехода по каждому разряду регистра 1 образуется только один раз, так как этот же сигнал инвертируется (на схеме не показано), поступая на вход схемы 4 и стирает -код «1 в данном разряде регистра i. Поэтому последующие сигналы перехода в этом разряде на выходе схемы 9 не образуются. На выход схемы 9 поступают только первые сигналы перехода по каждому разряду и складываются с содержимым регистра 12 в этом же разряде.

При втором варианте не происходит преобразования содержимого регистра 1 в число импульсов, а осуществляется передача самого числа в принятой системе счисления из регистра 1 в сумматор И. В этом случае на вход схемы 9 сигналы как с выхода сумматора 3, так и с выхода регистра 1 должны поступать младщими разрядами вперед. Сигналы с выхода схемы 9 подаются на вход сумматора 11 в обход цепей триггера 8 и схемы совпадения 10, поскольку они становятся лишними. Реализация схемы по второму варианту позволяет также существенно уменьшить время вычисления.

Время вычисления суммы двух чисел при первом варианте равно полному циклу работы счетчика переходов 2. При необходимости ускоренного выполнения операций следует применять второй вариант или вместо динамического счетчика 2 использовать электронный счетчик на статических элементах с общей выходной цепью для выделения сигналов перехода, поступающих от каждого разряда двоичного счетчика.

Прекращение поступления сигналов «стираиие 42, 43, 44 и «длительности цикла вычислений 40 приводит к стиранию содержимого регистров 1, 12, 15 и счетчика переходов 2.

Таким образом, если в регистр 1 занести число р, а в регистр 12 - число q, то за один полный цикл работы счетчика 2, создающего на выходе схемы 9 q импульсов, в регистре 12 образуется сумма этих чисел p-}-q.

Вычитание чисел. Для вычитания двух чисел в регистр 1 через схему 4 заносят вычитаемое. Уменьшаемое заносят через схему 13 в регистр 12. Потенциал кода операции подается на первый вход схемы совпадения 22. После занесения чисел и кода операции потенциалом длительности цикла вычислений разрещается счет импульсов ТИ1, поступающих в счетчик переходов 2 через схему совпадения 5, и начинается процесс вычисления, совершенно аналогичный описанному ранее

при сложении чисел. Только при вычитании чисел сигналы перехода после триггера 8 поступают на третий вход схемы 22, а затем через блок образования дополнительного кода 45 и через схему разделения 25 подаются на вход сумматора 11 и складываются с содержимым регистра 12. В результате, в нем образуется разность двух чисел.

Следовательно, если в регистр 1 завести вычитаемое р, а в регистр 12 уменьшаемое q, то за один полный цикл работы счетчика переходов 2 при поступлении на его вход импульсов ТИ1, на выходе схемы 9 образуется р импульсов, которые в блоке 45 преобразуются в дополнительный код и вычитаются из содержимого регистра 12. В результате этого в регистре 12 получается разность двух чисел q - p.

Если в регистр 1 заносить дополнение q-{-

числа q, то операция вычитания полностью заменяется схемой сложения и надобность в схеме 22 и блоке 45 отпадает, но при этом числа, над которыми совершается операция вычитания, лдолжны содержать одинаковое число

разрядов.

Умножение чисел. При умножении чисел в регистр 1 через схему совпадения 4 заносят один из сомножителей р. Второй сомножитель q в дополнительном коде заносят в

регистр 15. Для получения дополнительного кода может быть использован блок 45. Потенциал кода операции умножения подается на первые входы схем совпадения 19 и 21. В регистр 12 заносится число t, которое должно

быть прибавлено к произведению pq. После этого начинается процесс вычисления, который осуществляется так же, как и при выпол «ении операций сложения и вычитания.

Сигналы перехода с выхода триггера 8 через схему 21 поступают в сумматор 11 и накапливаются в регистре 12. За один цикл работы счетчика переходов 2 сумма сигналов перехода в регистре 12 равна сомножителю р. Сигналы переполнения счетчика переходов 2

после каждого цикла его работы заносятся через схему 19 по потенциалу Р„+1 (46) (служебный потенциал после последнего разряда) в сумматор 16 и вычитаются из содержимого регистра 15. Этот процесс вычисления продолжается до тех пор, пока содержимое регистра 15 не станет равным нулю, т. е. в течение q циклов работы счетчика переходов 2. После этого сигналом переполнения с выхода сумматора 16, поступающего через схему совпадения 17 по потенциалу РЯ+Ь происходит изменение состояния триггера 18, а его потенциалом закрывается схема 5, прекращается поступление тактирующих импульсов в счетчик переходов 2 и процесс умножения заканчивается. Триггер 18 устанавливается в исходное состояние сигналом 47 перед началом выполнения операций.

Таким образом, сомножитель р из регистра 1 заносится q раз в регистр 12, в результате

в нем образуется произведение сомножителей

pq. Если в регистр 12 предварительно занести число /, то после выполнения операции умножения в нем получится результат t-{-pq.

Деление чисел. При выполнении операции деления в регистр 1 через схему совпадения 4 заносят делитель р. Делимое q в дополнительном коде заносят в регистр 15.

Потенциал кода операции деления подается па первые входы схем совпадения 20, 23. После занесепия делителя и делимого потенциалом длительности цикла вычисления (вход 40) разрешается счет импульсов ТИ 1, поступающих в счетчик переходов 2 через схему совпадения 5. По сигналам перехода делитель в унитарном коде поступает в регистр 15 и складывается с дополнительным кодом делимого. За один цикл работы счетчика переходов 2 происходит одно вычитание делителя из делимого. Сигнал переполнения счетчика 2 после завершения цикла работы заносится через схему совпадения 23 по сигналу Р„+1 46 в регистр 12.

Описанный процесс вычисления продолжается до тех пор, пока содержимое регистра 15 не станет равным нулю. Очевидно, это произойдет тогда, когда в регистр 15 поступит число импульсов, равное q, а число вычитаний делителя из делимого будет равно их частному. После этого сигналом переполнения с выхода сумматора 16, поступающего через схему 17 по потенциалу Pn+, изменяется состояние триггера 18 и его потенциалом запрещается поступление тактирующих импульсов в счетчик переходов 2 и операция деления заканчивается.

В результате вычислений в регистре 12 фиксируются сигналы переполнения .после каждого цикла работы счетчика 2, число которых равно частному q/p. Время выполнения операции деления равно q/p циклов работы счетчика 2.

Извлечение .квадратного корня. При вычислении в регистр 15 заносят дополнительный код числа р; регистр 1, счетчик переходов 2 и регистр 12 срабатывают. Код операции извлечения корня подается на схемы 19, 20, 23, 24, 39.

Процесс вычисления начинается с поступления тактирующих импульсов 38 на вход счетчика переходов 2. Сигналы переполнения с выхода последнего поступают через схему 23 на вход сумматора 11 и фиксируются в регистре 12. Одновременно сигналы переполнения (числа циклов) заносятся через схему 19 и сумматор 16 в регистр 15. Сигналы перехода из «О в «1 с выхода схемы 10 через схему 20 и сумматор 16 также заносятся в регистр 15, но, начиная со второго разряда регистра, что равносильно умножению на 2; задержка на один разряд может быть выполнена на статическом триггере или лидии задержки на один такт. Эти импульсы складываются с содержимым регистра 15. Процесс вычисления продолжается до тех пор, пока

8

содержимое регистра 15 не станет равным пулю. Если счетчик 2 выполнит п циклов, то в регистре 1 зафиксируется число /г, а на вход регистра 15 поступит число

5„+2 0+1+2+ ... +(«+),

которое должно быть равно р, то есть

n + 2lO+l + 2 + ...+(n-l) п + р.

Откуда п Y р.

Сигнал переполнения с выхода регистра 15 проходит через схему 17 по сигналу Pn+i разряда и изменяет состояние триггера 18, потенциалом которого прекращается выполнение операции извлечения квадратного корня.

В качестве примера использования устройства на фиг. 2 приведена блок-схема цифрового аналога для рещения задачи

X t±pq/s.

В этой схеме введен дополнительный регистр 30, аналогичный регистр 1 (см. фиг. 1), и вторая схема выделения сигналов перехода. Операции умножения, деления и сложения (цо блок-схеме, приведенной па фиг. 2) выполняются одновременно. В регистр 30 заносят число р, в счетчик-регистр 34 - число /, в счетчик-регистр 36 - дополнение числа q и в регистр 31 -число s. Результат t- -pq/s образуется в счетчике-регистре 34. Вычисление

начинается при счете счетчи.ка-репистра 32 и продолжается до тех пор, пока содержимое счетчика-регистра 36 не будет равно нулю. При этом, если число циклов счетчика-регистра 32 принять за С, то C-s q, а ,

Pq

откуда Xi

Но так как перед началом вычислений в счетчик-регистр 34 было занесено число t, то окончательный результат получаем

x f±pq/s.

Предложенное СЦВУ позволяет создавать переменные программно-управляемые вычислйтельные структуры с различными алгоритмическими возможностями, изменяемыми разрядностью, быстродействием, системой счисления на базе однотипных элементов по простейшим алгоритмам. В качестве основного

вычислительного элемента приняты сдвигающий регистр с сумматором, который может быть выполнен как элемент однородной среды в виде большой интегральной схемы.

Предмет изобретения

Специализированное цифровое вычислительное устройство, содержащее регистры, счетчики и блок управления, соединенный 65 с регистрами и с выходами переполнения

счетчиков, схему тактирующих импульсов, соединенную со входом схемы получения потенциалов разрядов, выходы которой соединены со входами блока управления, сумматоры, триггеры, блок образования дополнительного кода, схемы совпадения и схемы разделения, отличающееся тем, что, с целью расширения функциональных возможностей, оно содержит схему выделения сигналов перехода, счетчик переходов, выход которого соединен с первым входом первого сумматора, выход которого соединен со входом счетчика переходов, нервый дополнительный регистр, выход которого соединен с его входом через первую схему совпадения, второй и третий регистры, выходы которых через вторую и третью схемы совпадения соединены с первыми входами второго и третьего сумматоров, выходы которых соединены со входами второго и третьего регистров соответственно, выход второго сумматора через четвертую схему совпадения соединен с первым входом первой схемы разделения, второй вход которой соединен с выходом первого регистра, а выход - с первым входом схемы выделения сигнала перехода, второй вход которой соединен с выходом счетчика переходов и через пятую и щестую схемы совпадения соединен с первыми входами второй -и третьей схем разделения, выходы которых соединены со вторыми входами второго и третьего сумматоров соответственно, выход

схемы выделения сигналов перехода через седьмую и восьмую схемы совпадения соединен со вторыми входами второй и третьей схем разделения соответственно, а через девятую схему совпадения соединен со входом

блока образования дополнительного кода, выход которого соединен с третьим входом второй схемы разделения, выход третьего регистра через десятую схему совпадения соединен с установочным входом триггера, выход которого через одиннадцатую схему совпадения соединен со вторым входом первого сумматора.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО для ВЫЧИТАНИЯ ДВУХ чист | 1970 |

|

SU278221A1 |

| ВЫЧИСЛИТЕЛЬНЫЙ ЭЛЕМЕНТ ДЛЯ ЦИФРОВЫХ ВЫЧИСЛИТЕЛЬНЫХ УСТРОЙСТВ | 1970 |

|

SU267188A1 |

| УСТРОЙСТВО для ПОСТРОЕНИЯ КОРНЕВЫХ ГОДОГРАФОВ СИСТЕМ АВТОМАТИЧЕСКОГО УПРАВЛЕНИЯ | 1973 |

|

SU397914A1 |

| ГЕНЕРАТОР ДУГ ОКРУЖНОСТЕЙ | 1973 |

|

SU397902A1 |

| ЭЛЕКТРОННАЯ ВЫЧИСЛИТЕЛЬНАЯ МАШИНА | 1961 |

|

SU135700A1 |

| ЛИНЕЙНЫЙ ИНТЕРПОЛЯТОР | 1973 |

|

SU363997A1 |

| Цифровой преобразователь координат | 1983 |

|

SU1163322A1 |

| Устройство для определения среднего арифметического значения | 1986 |

|

SU1310840A1 |

| Цифровой функциональный преобразователь | 1984 |

|

SU1242936A1 |

| Устройство для деления чисел в форме с плавающей запятой | 1988 |

|

SU1566340A1 |

3S, J

77

408304

Авторы

Даты

1973-01-01—Публикация