Изобретение относится к области дискретной автоматики и вычислительной техники.

Логические элементы «ДА и «НЕТ, содержащие насыщенные транзисторы, известны. Однако время срабатывания таких элементов недостаточно стабильно.

Предложенный логический элемент отличается от известных тем, что он содержит на входе эмиттерный повторитель, соединенный своим выходом с эмиттером одного насыщенного транзистора, базы насыщенных транзисторов объединены и соединены через резистор с источником постоянного напряжения, а эмиттер другого насыщенного транзистора подсоединен ко второму источнику постоянного напряжения.

Это увеличивает стабильность времени срабатывания логического элемента.

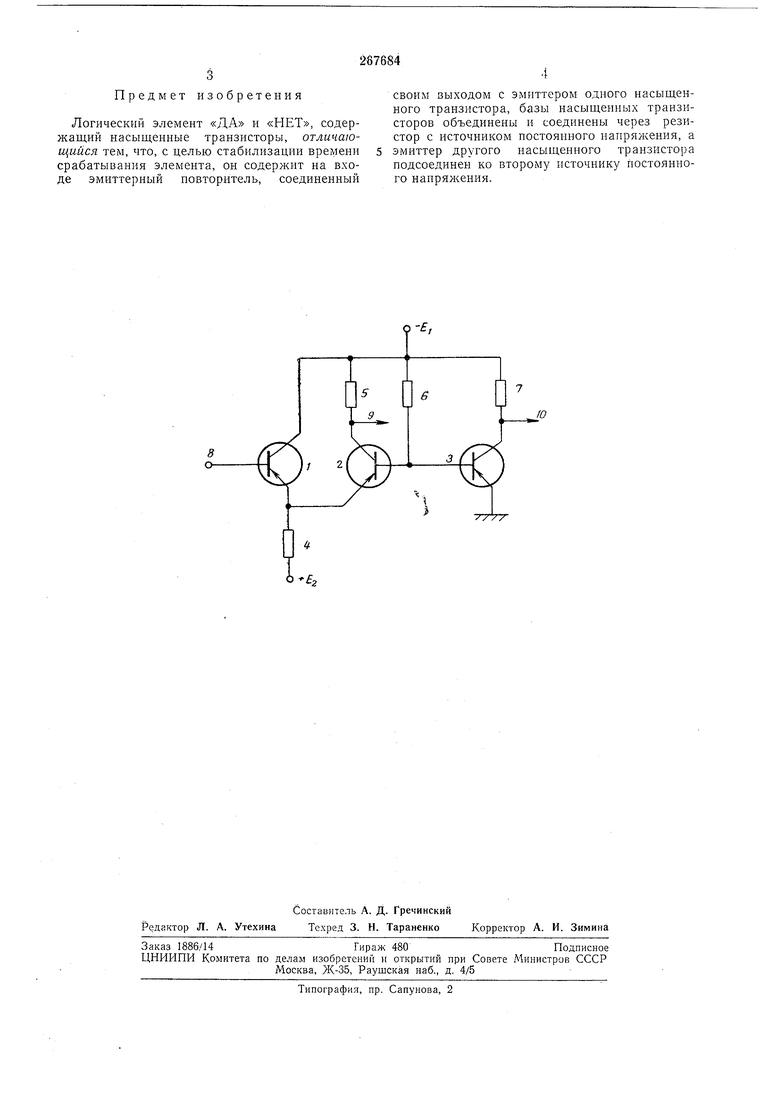

Принципиальная схема логического элемента «ДА и «НЕТ приведена на чертел е.

Элемент содержит транзистор /, включенный по схеме эмиттерного повторителя, транзисторы 2 и 5 и резисторы 4-7. Базовые токи транзисторов 2 и 5 задаются источником EI и резистором 6. Таким образом, стабильность базовых токов определяется лишь стабильностью источника i и резистора 6. При действии на вход 8 элемента низкого потенциала н транзистор 2 закрыт, транзистор 3 открыт; при действии на вход 8 высокого потенциала

Us транзистор 2 открыт, а транзистор 3 закрыт. В статическом состоянии логического элемента транзистор / всегда открыт, так как эмиттерный ток выбирается всегда больще коллекторного тока.

Транзистор 2 работает по схеме с общей базой и обладает высоким быстродействием. Транзистор 5 обладает также высоким быстродействием вследствие форсированного режима при открывании и закрывании. Ток базы открывающегося транзистора 3 выбирается в несколько раз больше тока, необходимого для граничного с насыщением линейного режима. Ток базы противоположного направления, закрывающий транзистор 3, также выбирается достаточно большим. Пока транзистор 3 еще не закрыт, а на входе 8 элемента действует высокий потенциал LB, транзистор 1

закрыт, и ток из базы транзистора 2 направляется в базу транзистора 3, закрывая его. Как только транзистор 3 закроется, потенциал на его базе, а следовательно, и на эмиттере транзистора / повышается, и транзистор

/ открывается. Нзбыток тока направляется в эмиттер транзистора /.

Предмет изобретения

Логический элемент «ДА и «НЕТ, содержащий насыщенные транзисторы, отличающийся тем, что, с целью стабилизации времени срабатывания элемента, он содержит на входе эмиттерный повторитель, соединенный

свонм выходом с эмиттером одного насыщенного транзистора, базы насыщенных транзисторовобъединены и соединены через резистор с источником ностоянного напряжения, а эмиттер другого насыщенного транзистора подсоединен ко второму источнику постоянного нанрял ения.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЛОГИЧЕСКИЙ ЭЛЕМЕНТ ЦИКЛИЧЕСКОЙ ИНВЕРСИИ ТРОИЧНОЙ ТРАНЗИСТОРНО-ТРАНЗИСТОРНОЙ ЛОГИКИ (ВАРИАНТЫ) | 2024 |

|

RU2835664C1 |

| ЛОГИЧЕСКИЙ ЭЛЕМЕНТ ТРОИЧНОЙ ТРАНЗИСТОРНО-ТРАНЗИСТОРНОЙ ЛОГИКИ | 2022 |

|

RU2782474C1 |

| ТРАНЗИСТОРНО-ТРАНЗИСТОРНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ | 1989 |

|

SU1679943A1 |

| Устройство для записи и считывания информации | 1972 |

|

SU499584A1 |

| Импульсный подмодулятор | 1976 |

|

SU681551A1 |

| Компаратор напряжений | 1978 |

|

SU902238A1 |

| Аналоговый N-канальный коммутатор широкополосных видеосигналов | 1988 |

|

SU1598153A1 |

| ФОРМАЛЬНЫЙ НЕЙРОН | 1973 |

|

SU375792A1 |

| Эмиттерный повторитель | 1983 |

|

SU1084967A1 |

| Формирователь радиоимпульсов | 1986 |

|

SU1437961A1 |

Даты

1970-01-01—Публикация