1

Изобретение относится к вычислительной технике, в частиости к устройствам для записи и считывания ииформации в электрических цифровых накопителях.

Известно устройство для записи и считывания информации, которое совмещает функции записи и считывания и имеет один выход на разрядггую линию накопителя. Оно содержит два транзистора заииси, база иервого из которых через резистор подключена к шине «Управляющий сигнал, эмиттер подключен к щине нулевого потенциала, а коллектор через резистор нодсоединен к коллектору второго транзистора, эмиттер которого подключен к первому источнику питания, и транзистор считывания, коллектор которого через резистор подключен ко второму источнику питания, а эмиттер через резистор подсоединен к шине нулевого потенциала и через другой резистор - к третьему источнику питания, и шину «Разрядная линия. Однако оно характеризуется малым быстродействием при записи «1, в результате того, что время записи «1 в накопитель зависит от амплитуды сигнала, заряжающей паразитную емкость разрядной линии. Разрядная линия является нагрузкой эмиттерного повторителя, который образует схему записи. Поэтому амплитуда сигнала на ней при записи «1 зависит только от амплитуды сигнала, поступающего на вход эмиттер2

ного повторителя от цифровых интегральных схем (при записи «1 подается высокий уровень). Имеющиеся интегральные схемы не могут обеспечить высокого быстродействия сопряженного с ними устройства для записи - считывания. Кроме того, такая зависимость работы устройства от сигнала интегральных схем приводит к нестабильности быстродействия за счет разброса выходных уровней интегральных схем, особенно при работе с импульсами малой длительности; малым быстродействием при записи «О, поскольку время записи «О зависит от разности выходного уровня интегральных схем (при записи «О подается низкий уровень) и уровня сигнала, поступающего из накопителя в разрядную линию. Эта разность должна достичь величины, достаточной для отпирания второго транзистора записи. Чей выще уровень выходного сигнала, который подается на базу транзистора записи, тем больший сигнал должен подаваться на эмиттер этого транзистора из накопителя через разрядную линию. Получение более высокой амплитуды на разрядной линии

снижает быстродействие. В результате при записи «О быстродействие оказывается невысоким и зависит от выходного уровня интегральных схем; малым быстродействием при считывании, поскольку время считывания для

накопителя с высоким выходным сопротивлением зависит от времени заряда паразитной емкости разрядной линии. Кроме того, необходимость обеспечения надежного срабатывания интегральной схемы, подключенной к выходу усилителя считывания, приводит также к уменьшению быстродействия при считывании, потому что сигнал на разрядной линии должен достичь амплитуды надежного отпирания транзистора считывания, при этом надо учесть еще амплитуду, которая падает на втором транзисторе записи. Таким образом, быстродействие известного устройства для записи - считывания далеко уступает быстродействию логических элементов ЦВМ и имеет ограниченное применение, поскольку его целесообразно использовать только в оперативном запоминающем устройстве (ОЗУ), имеющем небольшие паразитные емкости разрядных линий.

Целью изобретения является повышение быстродействия и надежности работы устройства записи и считывания информации. Это достигается тем, что в предлагаемое устройство введен третий транзистор записи, база которого через параллельную цепочку RC подключена к шине записи, эмиттер подсоединен к шине нулевого потенциала, а коллектор через резистор подключен к первому источнику питания, а через другой резистор - к базе второго транзистора записи, и второй транзистор считывания, база которого подключена к коллектору первого транзистора считывания, эмиттер - ко второму источнику питания, а коллектор через резистор подсоединен к шине нулевого потенциала и подсоединен к выходной шине считывания информации, база первого транзистора считывания через резистор подключена к коллектору второго транзистора записи, который соединен с шиной «Разрядная линия.

При записи «1 устраняется зависимость быстродействия от выходного уровня интегральных схем. Амплитуда на разрядной линии зависит только от напряжения на зажиме питапия. Это позволяет подавать на разрядную линию сигнал более высокий по амплитуде, сокращает время заряда паразитной емкости и тем самым повышает быстродействие при записи «1. Цри этом использование транзисторов различной проводимости устраняет потребление энергии в исходном состоянии, а включенная в цень базы согласующего транзистора RC цепочка уменьшает нагрузку интегральной схемы, не снижая быстродействия. При записи «О устраняется также зависимость быстродействия от выходного уровня интегральных схем. На разрядную линию от накопителя поступает импульс, который проходит по цепи, состоящей из резистора и открытого транзистора и представляющей для разрядной линии и выбранного элемента накопителя низкоомную нагрузку, что обеспечивает переключение данного элемента в «О. Мет необходимости повышать амплитуду сигнала на разрядной линии до величины, достаточной для отпирания транзистора записи, как это делается в схеме прототипа. За счет этого повышается быстродействие. При считывании быстродействие повышается за счет увеличения чувствительности усилителя считывания. Делитель напряжения подает такое отрицательное напряжение смещения на эмиттер транзистора считывания, которое приближает рабочую точку к порогу открывания транзпстора, но не открывает его. В этом случае на усилителя считывания может быть подан сигнал меньшей амплитуды (по сравнению с прототипом), что значительно повышает быстродействие. Для обеспечения надежного срабатывания интегра,яьной схемы, подключенной к выходу устройства, служит вторая ступень усиления сигнала считывания. Применение транзисторов различной проводимости в усилителе считывания приводит к тому, что усилитель не потребляет мошность от основного источника питания в исходном состоянии. Таким образом, предлагаемое устройство для записи - считывания позволяет более полно использовать возможности интегральных матриц на основе полевых транзисторов и приблизить быстродействие ОЗУ к быстродействию логических схем ЦВМ.

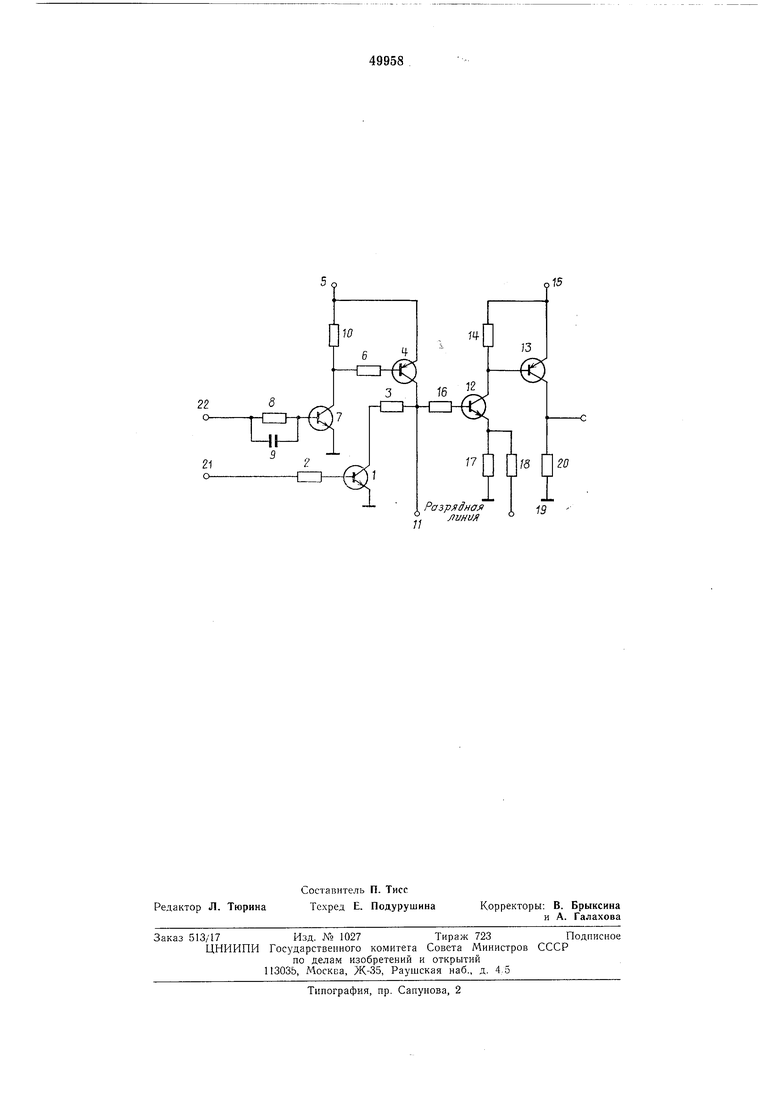

На чертеже приведена принципиальная схема предлагаемого устройства.

Транзистор 1 является транзистором записи (записи «О), его база подсоединяется к шине «Управляющий сигнал через резистор 2, а коллектор через резистор 3 - к коллектору транзистора 4 (транзистора записи «1).

Эмиттер транзистора 4 подключен к источнику питания 5, а его база через резистор 6 - к коллектору транзистора 7, база которого через параллельную цепочку резистор 8 - конденсатор 9, подсоединена к щине «записи,

а коллектор через резистор 10 - к источнику питания 5.

Резисторы 8 и 2 ограничивают базовые токи транзисторов 7 и 1; конденсатор 9 - ускоряющий. Резистор 6 ограничивает ток базы транзистора 4 и уровень помех. Резистор 3 служит для ограничения тока в коллекторной цепи транзистора 1.

Разрядная линия 11 подключена к точке

соединения транзисторов записи 1 и 4 и транзистора считывания 12. Транзистор 12 образует с транзистором 13 двухкаскадный усилитель с гальванической связью, с выхода которого сигнал подается на логическую интегральную схему. Резистор 14 служит коллекторной нагрузкой и подключается к источнику питания 15. Резистор 16 ограничивает ток базы транзистора 12. Резисторы 17 и 18 составляют делитель иапряжения, который подключается к эмиттеру транзистора 12 и служит для повышения его чувствительности. Резистор 18 соединен с третьим источником питания 19. Резистор 20 является коллекторной нагрузкой транзистора 13 и подключается к выходной щине считывания.

Схема предложенного устройства имеет исходное состояние в режиме хранения информации ОЗУ, когда на вход транзистора 7 нодается нулевой потенциал. Транзисторы 7 и 4 закрыты. Переход база - эмиттер транзистора 1 открыт при воздействии высокого положительного потенциала, поступающего с шины 21 «Управляющий сигнал. Транзисторы 12 и 13 закрыты, причем транзистор 12 под влиянием отрицательного потенциала смещения на эмиттере находится в состоянии, близком к пороговому. В данном состоянии на выходную шину считывания через резистор 20 поступает нулевой потенциал.

Схема работает в двух режимах: в режиме записи («1 и «О) и в режиме считывания.

В режиме записи «1 на шину 22 «Записи поступает импульс положительной полярности и открывает транзистор 7. Падение напряжения на резисторе нагрузки 10 снижает потенциал базы по отношению к эмиттеру транзистора 4 и открывает его. Открытый транзистор 4 подключает разрядную линию к источнику напряжепия питания, и до этой величины стремится зарядиться паразитная емкость разрядной линии. При достижении определенного уровня сигнала на разрядной линии в выбранном элементе накопителя происходит запись «i. Цепь, состоящая из открытого транзистора 1 и резистора 3, является активной составляющей нагрузки транзистора 4. Выходной сигнал схемы записи поступает и на вход усилителя считывания, но логическая схема, подключенная к его выходу, должна реализовать запрет дальнейшему прохождению сигнала. Мосле прекращения -подачи импульса схема возвращается в исходное состояние. Паразитная емкость разрядной линии разряжается но цепи резистора 3 - открытый транзистор 1.

В режиме записи «О на шине 22 «записи установлен нулевой уровень, а на базу транзистора 1 так же, как при записи «1, подается высокий положительный потенциал, и транзистор открыт. Па разрядную линию от накопителя поступает импульс положительной полярности, указывающий на то, что там была записана «1. Цепь, состоящая из резистора 3 и открытого транзистора 1, составляет для разрядной линии и выбранного элемента накопителя низкоомную нагрузку и способствует переключению данного элемента в состояние «О. Если в элементе накопителя уже был заиисан «О, то схема сохраняет исходное состояние и никаких изменений не происходит. Запрет дальнейшему прохождению сигнала реализует логическая схема, как при записи «1.

В режиме считывания транзистор 1 закрывается подачей на вход сигналов управления инверсного импульса положительной полярности. Если в выбранном элементе накопителя была записана «, то на разрядной линии появляется имнульс положительной полярности.

Он воздействует на базовую цепь транзистора 2 и при достижении амплитуды, превышающей разницу между пороговым напряжением транзистора и потенциалом смещения на эмиттере, транзистор 12 открывается. В режиме считывания без разрушения информации токи базы обычно составляют десятки микроампер, и резистор 16 (величиной в несколько сот ом) на быстродействие при считывании существенно не влияет. Но при больших входных амплитудах входного сигнала (например во время записи «1), он способствует ограничению базового тока транзистора 12. Такие же рассуждения снраведливы и в отношении резистора

делителя напряжения 17 в цепи эмиттера транзистора 12, имеющего величину всего несколько десятков ом. После предварительного усиления сигнала транзистором 12, сигнал через гальваническую связь поступает на базу

транзистора 13, где осуществляется дополнительное усиление. С коллектора транзистора 13 сигнал, полученный при считывании, непосредствен г:о может быть подан на логическую интегральную схему, подключенную к выходу

устройства. В том случае, если в выбранном элементе накопителя записан «О, то на разрядной линии сигнал отсутствует, и усилитель считывания остается в исходном состоянии.

Формула и 3 о б р е т е и и я

Устройство для записи и считывания информации, содержащее два транзистора записи, база первого из которых через резистор подключена к шине «Управляющий сигнал, эмиттер подключен к шине нулевого потенциала, а коллектор через резистор подсоединен к коллектору второго транзистора, эмиттер которого подключен к первому источнику питания, и транзистор считывания, коллектор

которого через резистор подключен ко второму источнику питания, а эмиттер через резистор подсоединен к шине нулевого потенциала и через другой резистор - к третьему источнику питания, и шину «Разрядная лнния.

отличающееся тем,, что, с целью повышения быстродействия и надежности работы устройства, в него введен третий транзистор записи, база которого через параллельную цепочку RC подключена к шине заниси, эмиттер

подсоединен к шине нулевого потенциала, а коллектор через резистор подключен к первому источнику питания, а через другой резистор - к базе второго транзистора записи, и второй транзистор считывания, база которого

нодкючека к коллектору нервого транзистора считывания, эмиттер - ко второму источнику питания, а коллектор через резистор нодсоедпнен к шине нулевого потенциала и нодсоедип&н к выходной шине считывания информации, база первого транзистора считывания через резистор подключена к коллектору второго транзистора записи, который соединен с шиной «Разрядная линия.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для записи и считывания с накопителя | 1972 |

|

SU486371A1 |

| Накопитель для запоминающего устройства | 1983 |

|

SU1137537A1 |

| Матричный накопитель | 1979 |

|

SU799007A1 |

| Усилитель записи и считывания для запоминающего устройства с произвольной выборкой | 1983 |

|

SU1091223A1 |

| Запоминающее устройство | 1976 |

|

SU690564A1 |

| Запоминающее устройство | 1976 |

|

SU597006A1 |

| Матричное запоминающее устройство | 1977 |

|

SU744724A1 |

| Постоянное запоминающее устройство | 1982 |

|

SU1112411A1 |

| Устройство для записи и считывания | 1973 |

|

SU469989A1 |

| ЯЧЕЙКА ПАМЯТИ ДИНАМИЧЕСКОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 2001 |

|

RU2216795C2 |

Авторы

Даты

1976-01-15—Публикация

1972-11-21—Подача