Данное изобретение относится к цифровым вычислительным машинам.

Известны запоминающие устройства команд, содержащие буферное и основное запоминающие устройства команд, счетчик команд, регистр команд и датчик управляющих импульсов.

Предлагаемое устройство отличается от известных тем, что оно содержит блок адресации буферного запоминающего устройства команд (БЗУ), состоящий из счетчика, дешифратора, схемы совпадения, схемы сборки и триггера. Вход счетчика соединен с выходом датчика управляющих импульсов, связанным со входом счетчика команд. Выходы младших разрядов счетчика соединены со входами дешифратора, пулевые выходы остальных разрядов - со входами схемы совпадения, а их единичные выходы- со входами схемы сборки. Выход схемы совпадения соединен с управляющим входом дешифратора, оба входа триггера - с датчиком управляюгцих импульсов, единичный выход триггера - со входами схемы совпадения н схемы сборки, а нулевой выход триггера и выход схемы сборки - с цепью установки в нуль счетчика н с выходом счетчика команд. Устройство, содержит также ряд блоков фиксации занятости каждой ячейки буферного запоминающего устройства команд, каждый из которых состоит нз триггера и двух

вентилей. Оба выхода триггера соединены со входами вентилей, другие входы вентилей соединены с выходами дешифратора блока адресации буферного запоминающего устройства

команд, выход одного из вентилей соединен с шиной считывания соответствующей ячейки БЗУ команд, а выход другого - с шиной записи в соответствуюшую ячейку БЗУ команд и со входом счетчика команд. Это позволяет новысить быстродействие цифровой вычислительной машины.

Предложенное устройство предназначено для решения следующих задач:

а)в процессе первого прохождения циклического участка программы команды должны

переписываться нз основного запомпиаюшего устройства в буферное, а при повторных обращениях к этому участку программы - выбираться из буфериого запомииающего устройства;

б)указанные функцнн должны выполняться и при вилтреиией структуре циклического участка, когда последннй содерл ит безусловные и условные переходы внутри цикла и

внутренние циклы;

каждом повторном обращении к циклу. Команды, входящие в цикл, но не помещающиеся Б буферное запоминающее устройство, естественно, должны выбираться из основного заноминающего устройства.

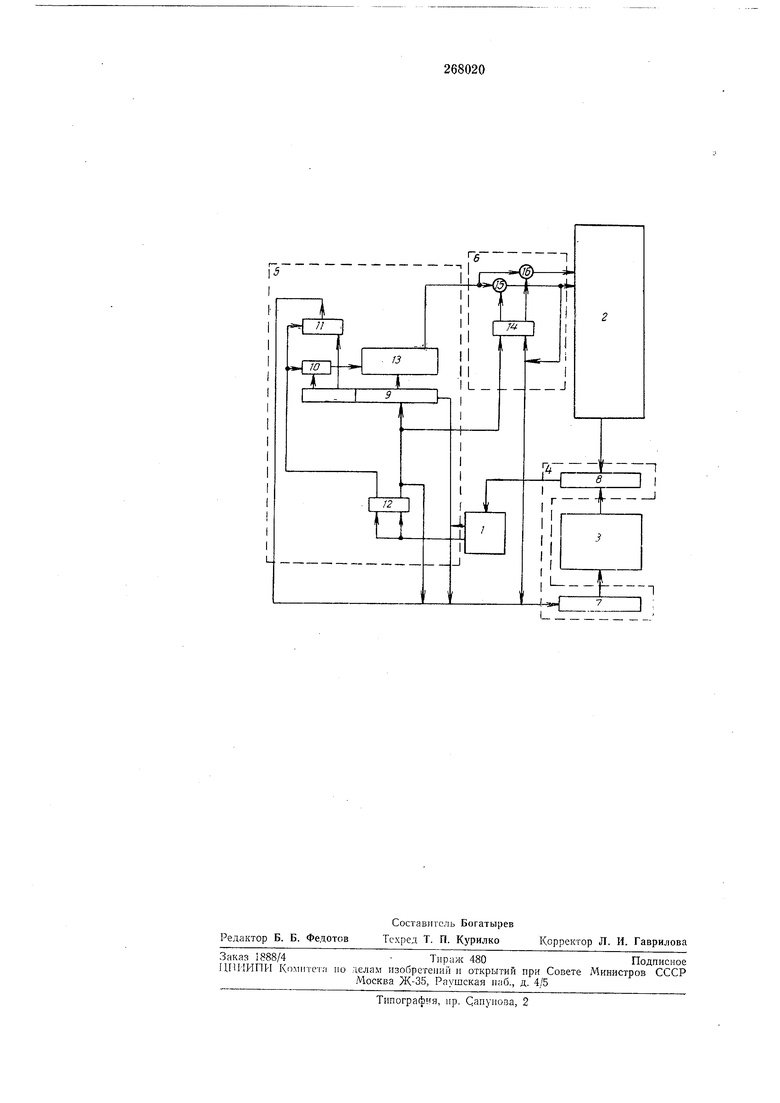

Предлагаемая структура заномпнающего устройства команд изображена на чертеже с некоторыми уцрощеииямн, т. е. некоторые унравляющие имнульсы во избежацие загромождения схемы не ноказаны.

Устройство содержит датчик / унравляющих импульсов, буферное запоминающее устройство команд 2, состоящее из 2 ячеек, основное запоминающее устройство команд :, блок 4 выборки команд нз основного запомннающего устройства, блок 5 адресации ячеек буферного запоминающего устройства и ряд блоков 6 фиксации занятости ячеек буферного запоминающего устройства, количество которых равно количеству его ячеек. Блок выборки команд из ОЗУ содержит счетчик 7 и регистр 8. Счетчик обычным образом связан с основным запоминающим устройством 3 и датчиком / управляющих импульсов, регистр команд также обычным образом связан с датчиком уиравляющнх импульсов и запоминающими устройствами.

Блок 5 адресации буферного заноминающего устройства содержит счетчик 9, схему совиадения 10, схему сборки //и триггер цикла 12. Счетчик буферного запоминающего устройства имеет п + т разрядов, где п--количество младших разрядов, необходимое для иеносредствеииой адресации буферного запоминающего устройства, а т - донолнительное количество старших разрядов, рассчитанных на максимальный размер выделяемых циклов, л младших разрядов связано с дешифратором 13, имеющим 2 выходов. Схема совнадения 10, связанная с нулевыми выходами т дополнительных разрядов счетчика 9, вырабатывает сигнал, если все дополнительные разряды имеют нулевое значение. Схема сборки П, связанная с единичными выходами т дополнительных разрядов, вырабатывает сигнал, если в каком-либо из доиолнительных разрядов находится хотя бы одна единица. Сигнал, вырабатываемый схемой сборки, представляет собой инверсию по отношению к сигналу, вырабатываемому схемой совпадения. Триггер цикла 12 устанавливается в единицу при входе ЦВМ в режим цикла. Единичиый выход триггера цикла связан со схемой сборки и со схемой совпадения, нулевой выход - с цепью установки на нуль счетчика 9 и триггеров в блоке 6 фиксации занятости ячеек БЗУ.

Блок 6 содержит триггер 14 с двумя вентилями на выходе. Вентиль 15 связан с нулевым выходом триггера, с дешифратором 13 блока 5 адресации БЗУ и с шиной записи в буферное запоминающее устройство 2, с датчиком управляющих импульсов, с цепью установки в единицу триггера 14 н с управляющим входом счетчика команд. Вентиль 16 связан с дешифратором 13, с единичным выходом триггера 14 и с шиной считывания из буферного запоминающего устройства 2.

Структура комаид предлагаемого устройства имеет следующие особенности:

а) циклическая часть программы отмечена специальными командами, записываемыми в программу перед первой командой цикла н после его завершающей команды;

б) все переходы, не являющиеся обращением к подпрограмме,- относительны, т. е. в командах указывается не абсолютный адрес комаиды, а нрнращение адреса.

В момент входа в циклический участок нрограммы командой «Начало цикла счетчик 9 и все триггеры М в блоках фиксации занятости ячеек БЗУ устанавливаются в нуль, а трнггер цнкла для перехода на спецнальный режим работы ЦВМ - режим цикла - в единицу. При

переходе внутри цикла от одной команды к другой к счетчику 7 команд и счетчику 9 добавляется либо единица либо, при исиолненпи команд условного и безусловного перехода,- одна и та же константа, для чего оба счетчика

выполнены как сумматоры. В цикле обращение за очередной командой происходит по счетчику 9 - импульсом с шины дешифратора 13 с номощью вентилей 15 и 16 оиращивается состоянне выбранной согласно коду на

счетчике 9 ячейки устройства 2. В результате нроверки вырабатывается один нз других сигналов:

а)ячейка БЗУ содержит команду, триггер 14 установлен в единицу. В этом случае команда

считывается через вентиль 16, соединенный с шиной считывання из ячейки БЗУ на регистр S команд;

б)ячейка БЗУ не содержит команды, триггер 14 установлен в нуль. Этот случай встречается при первом прохождении по циклическому участку программы. В момент проверки запись в БЗУ стандартным образом блокируется. Команда выбирается из ОЗУ но счетчику 7

команд, записывается на регистр 8, а затем вновь нроисходит обращение к этой ячейке БЗУ. Команда с регистра команд переписывается в ячейку БЗУ, для чего импульсом с дешифратора через вентиль 15 возбуждается соответствующая шина заииси в БЗУ, а триггер 14 устанавливается в единицу. Если циклическая часть программы имеет сложную внутреннюю структуру, т. е. содержит условные и безусловные переходы и внутренние

циклы, она необязательно переписывается в БЗУ при нервом же обращении к этому участку. Цосле первого исполнения циклической части программы в БЗУ могут остаться незаполпепными отдельные участки, соответствующне пекоторым ветвям программы. Эти участки заполняются нрн первом же обращении к дайной ветви. Для эффективного использования БЗУ в случае, когда циклическая часть программы не уменьшается в БЗУ, к счетчи5аа количество команд в цикле ие превы;т размера БЗУ, выявляется схемой 10 совения нулей всех дополнительных разрядов, защение БЗУ в этом случае происходит ио 1ДШИМ разрядам счетчика с иомощью де-5 |)ратора 13, управляемого импульсом с выа схемы совиадения. При выходе за разI БЗУ (при этом появляется единица хотя в одном из дополнительных разрядов счета) запись команд в БЗУ и считывание изю 0 блокируются. Этот случай выявляется мой сборки 11, связанной с единичными вы,ами т дополнительных разрядов счетчи9. Импульсом с выхода этой схемы управ:тся выборка команды из ОЗУ. После воз-is .щения к началу цикла для повторного ис1нения нули в дополнительных разрядах тчика восстанавливаются, и команды наibHoro участка программы, равного по своей 1не объему БЗУ, выбираются из БЗУ. При20 {Оде из цикла режим цикла сбрасывается, :ггер 12 устанавливается в нуль. .-. Предмет изобретения Запоминающее устройство команд, содержа-25 е буферное и основное запоминающие уст1ства команд, счетчик команд, регистр лайд и датчик управляющих импульсов, отшющееся тем, что, с целью повышения быОдействия цифровой вычислительной маши-30 , оио содержит блок адресации буферного запоминающего устройства (БЗУ), состоящий из счетчнка, дещифратора, схемы совиадения, схемы сборки и триггера, причем вход счетчика соединен с выходом датчика управляющих импульсов, связанным со входом счетчика команд, выходы младщих разрядов счетчика соединены со входами дешифратора, нулевые выходы остальных разрядов соединены со входами схемы совпадения, а их единичные выходы соедииепы со входами схемы сборки, выход схемы совпадеиия соединен с управляющим входом дешифратора, оба входа триггера соединены с датчиком управляющих импульсов, едииичпый выход триггера соединен со входами схемы совпадения и схемы сборки, а нулевой выход триггера и выход схемы сборки соединены с цепью установки в нуль счетчнка и с выходом счетчнка команд, ряд блоков фиксации занятости каждой ячейки буферного запоминающего устройства команд, каждый из которых состоит из триггера и двух вентилей, причем оба выхода триггера соединены со входами вентилей, другие входы вентилей соединены с выходами дешифратора блока адресации буферного запоминающего устройства команд, выход одного из вентилей соединей с шиной считывания соответствующей ячейки БЗУ команд, а выход другого вентиля соединен с шиной записи в соответствующую ячейку БЗУ команд и со входом счетчика команд. 6

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для ввода информации | 1987 |

|

SU1432544A1 |

| УСТРОЙСТВО для АВТОМАТИЧЕСКОГО КОДИРОВАНИЯ | 1972 |

|

SU354409A1 |

| БУФЕРНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С АССОЦИАТИВНОЙ АДРЕСАЦИЕЙ | 1973 |

|

SU397970A1 |

| Буферное запоминающее устройство | 1988 |

|

SU1583938A1 |

| МНОГОКАНАЛЬНАЯ СИСТЕМА ДЛЯ РЕГИСТРАЦИИ ФИЗИЧЕСКИХ ВЕЛИЧИН | 1991 |

|

RU2037190C1 |

| Устройство для сопряжения вычислительнойМАшиНы C ТЕРМиНАлАМи | 1979 |

|

SU798786A1 |

| Многоканальная система измерения и регистрации | 1988 |

|

SU1707546A1 |

| ЦИФРОВАЯ МАШИНА ДЛЯ ПОИСКА ИНФОРМАЦИИ | 1966 |

|

SU214201A1 |

| ПРОЦЕССОР ДЛЯ ЦИФРОВОЙ СИСТЕМЫ ОБРАБОТКИ ДАННЫХ | 1971 |

|

SU305477A1 |

| Микропроцессор | 1985 |

|

SU1330634A1 |

Даты

1970-01-01—Публикация