Изобретение относится к цифровой вычислительной технике и может быть использовано в устройствах передачи данных.

Целью изобретения является расширение области применения за счет возможности адресации слов сообщения и модификации адресов повторяющихся слов сообщения.

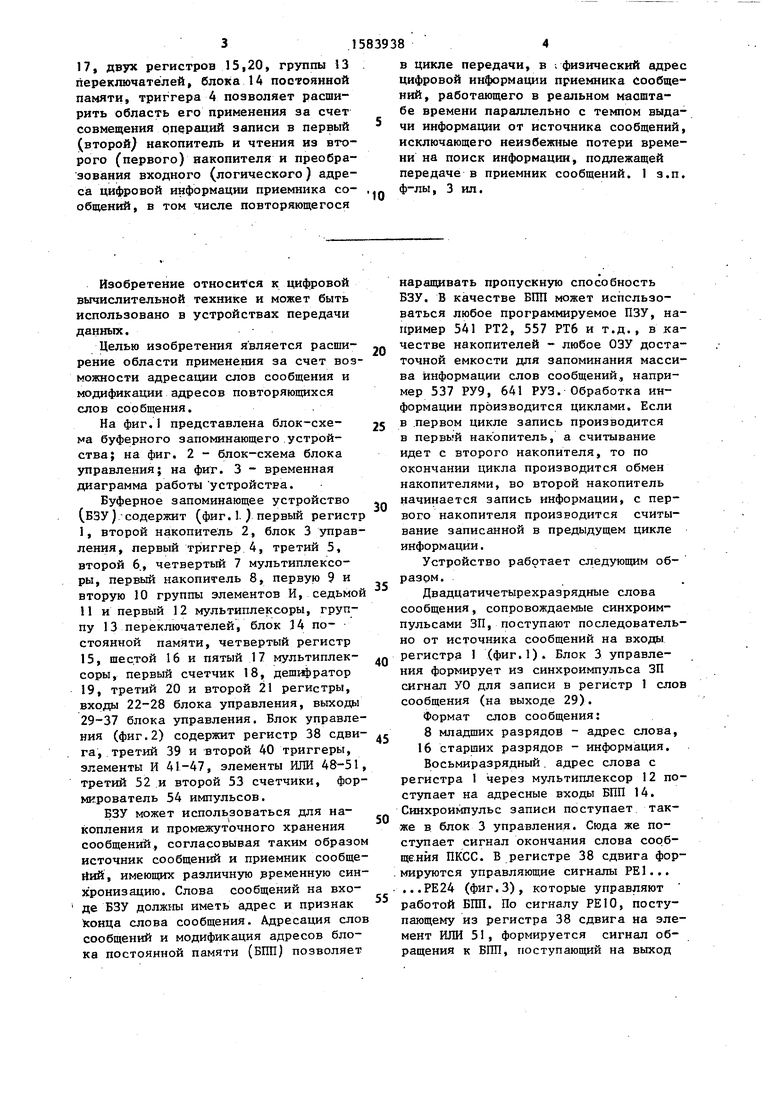

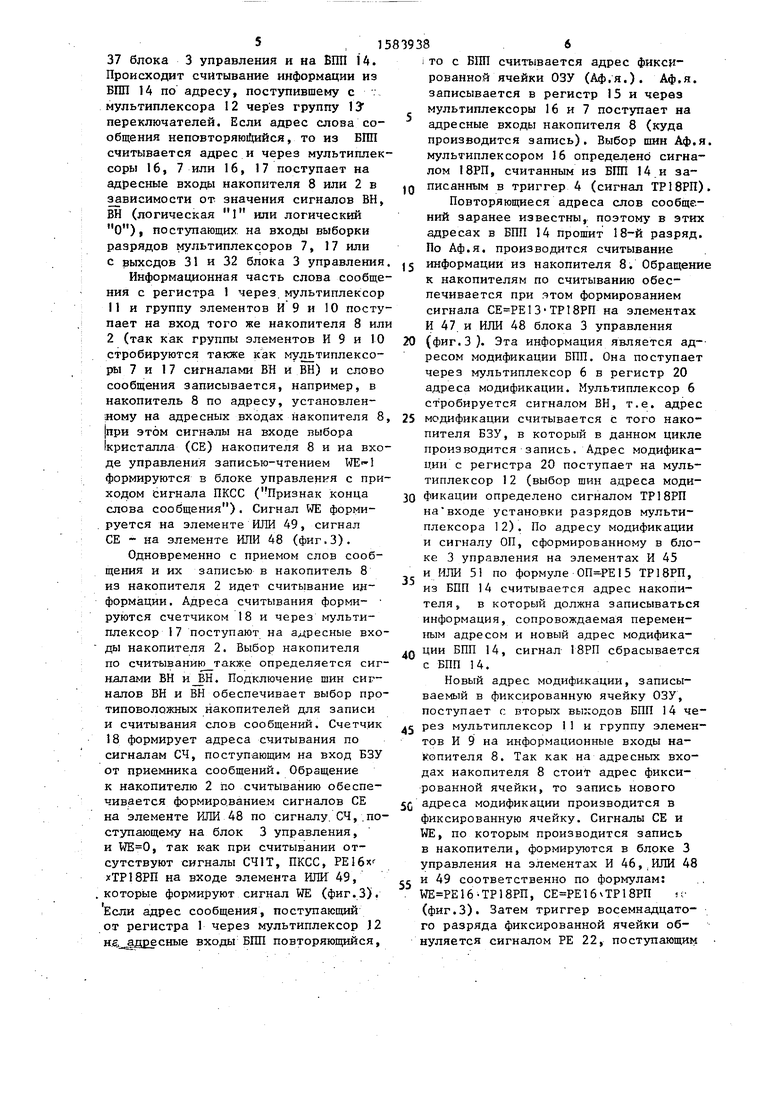

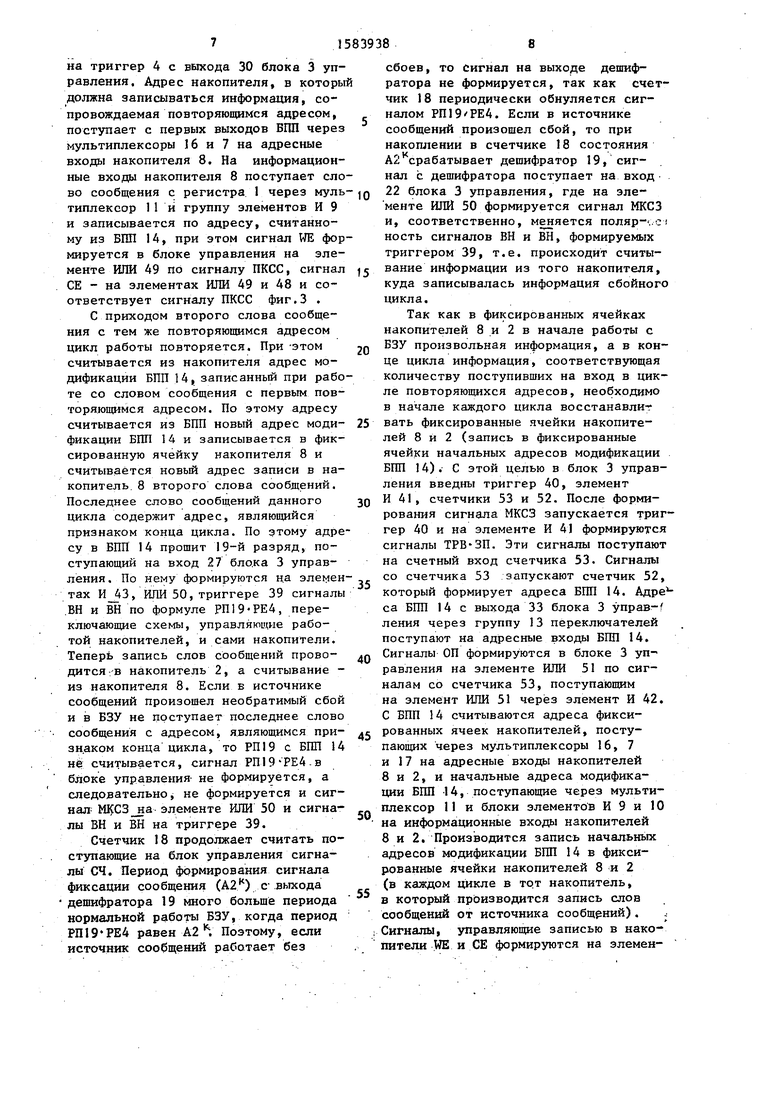

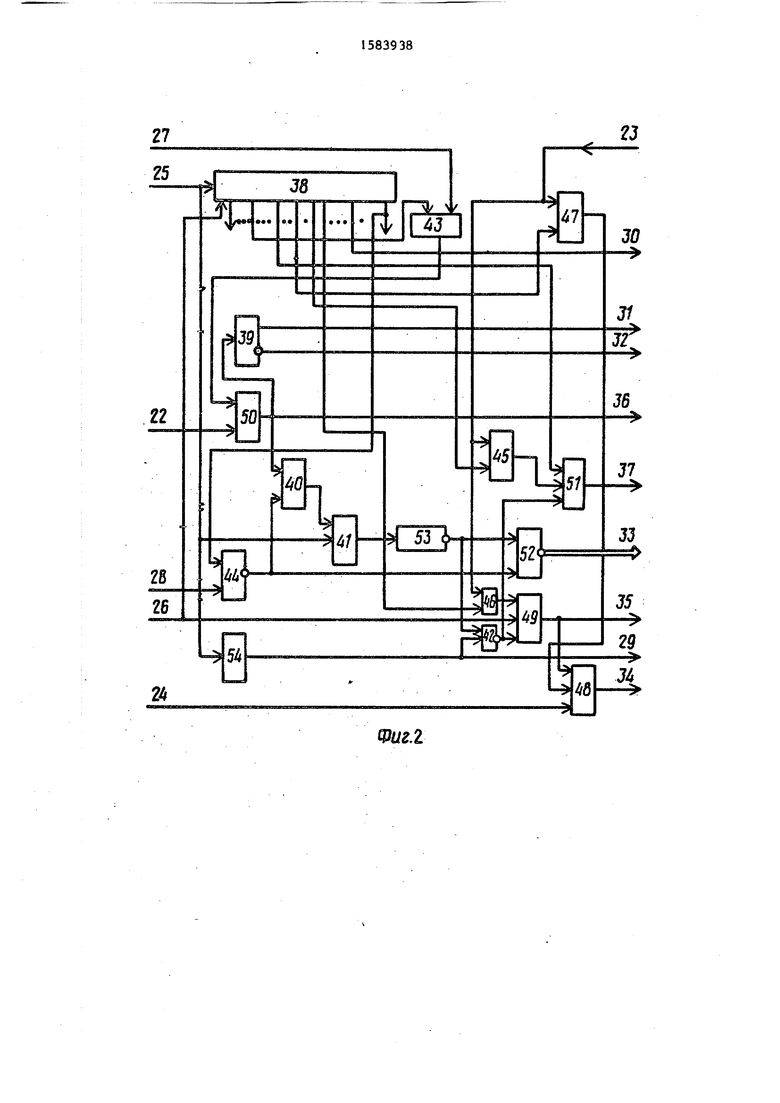

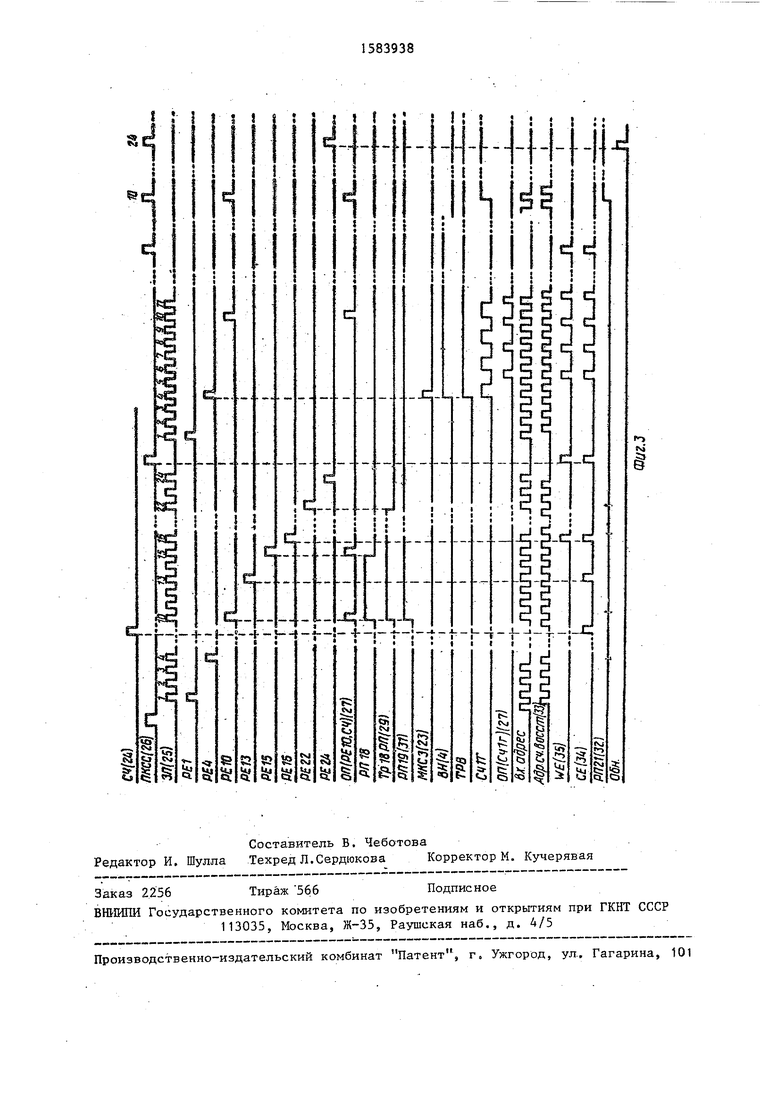

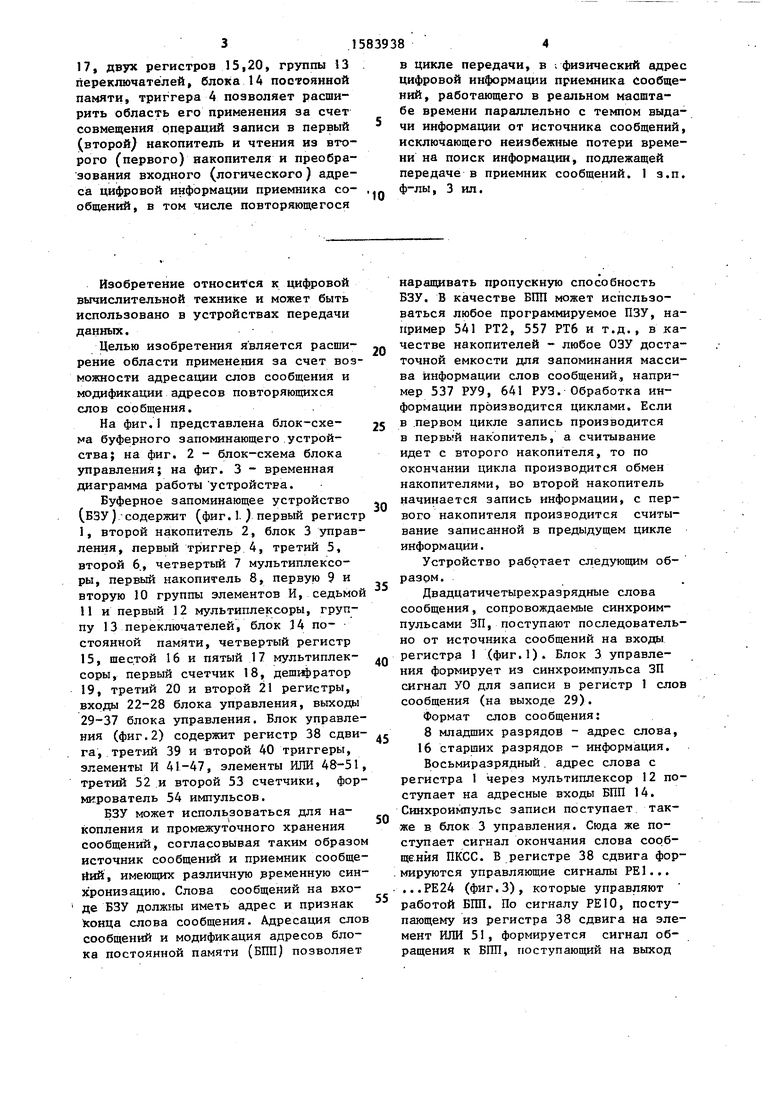

На фиг,1 представлена блок-схема буферного запоминающего устройства; на фиг. 2 - блок-схема блока управления; на фиг. 3 - временная диаграмма работы устройства.

Буферное запоминающее устройство (БЗУ) содержит (фиг. 1. ) первый регистр 1, второй накопитель 2, блок 3 управления, первый триггер 4, третий 5, второй 6, четвертый 7 мультиплексоры, первый накопитель 8, первую 9 и вторую 10 группы элементов И, седьмой 11 и первый 12 мультиплексоры, группу 13 переключателей, блок 34 постоянной памяти, четвертый регистр 15, шестой 16 и пятый 17 мультиплексоры, первый счетчик 18, дешифратор 19, третий 20 и второй 21 регистры, входы 22-28 блока управления, выходы 29-37 блока управления. Блок управления (фиг.2) содержит регистр 38 сдвига, третий 39 и второй 40 триггеры, элементы И 41-47, элементы ИЛИ 48-51, третий 52 и второй 53 счетчики, формирователь 54 импульсов.

БЗУ может использоваться для накопления и промежуточного хранения сообщений, согласовывая таким образом источник сообщений и приемник сообщений, имеющих различную временную синхронизацию. Слова сообщений на входе БЗУ должны иметь адрес и признак конца слова сообщения. Адресация слов сообщений и модификация адресов блока постоянной памяти (БПП) позволяет

0

5

0

5

0

5

0

5

наращивать пропускную способность БЗУ. В качестве БПП может использоваться любое программируемое ПЗУ, например 541 РТ2, 557 РТ6 и т.д., в качестве накопителей - любое ОЗУ достаточной емкости для запоминания массива информации слов сообщений, например 537 РУ9, 641 РУЗ. Обработка информации производится циклами. Если в первом цикле запись производится в первый накопитель, а считывание идет с второго накопителя, то по окончании цикла производится обмен накопителями, во второй накопитель начинается запись информации, с первого накопителя производится считывание записанной в предыдущем цикле информации.

Устройство работает следующим образом.

Двадцатичетырехразрядные слова сообщения, сопровождаемые синхроимпульсами ЗП, поступают последовательно от источника сообщений на входы регистра 1 (фиг.1). Блок 3 управления формирует из синхроимпульса ЗП сигнал УО для записи в регистр 1 слов сообщения (на выходе 29).

Формат слов сообщения:

8 младших разрядов - адрес слова, 16 старших разрядов - информация.

Восьмиразрядный адрес слова с регистра 1 через мультиплексор 12 поступает на адресные входы БПП 14. Синхроимпульс записи поступает также в блок 3 управления. Сюда же поступает сигнал окончания слова сообщения ПКСС. В регистре 38 сдвига формируются управляющие сигналы РЕ1... ...РЕ24 (фиг.З), которые управляют работой БПП. По сигналу РЕЮ, поступающему из регистра 38 сдвига на элемент ИЛИ 51, формируется сигнал обращения к БПП, поступающий на выход

37 блока 3 управления и на БПП 14. Происходит считывание информации из БПП 14 по адресу, поступившему с мультиплексора 12 через группу 13 переключателей. Если адрес слова сообщения неповторяющийся, то из БПП считывается адрес и через мультиплексоры 16, 7 или 16, 17 поступает на адресные входы накопителя 8 или 2 в зависимости от значения сигналов ВН, ВН (логическая 1 или логический О), поступающих на входы выборки разрядов мультиплексоров 7, 17 или с выходов 31 и 32 блока 3 управления.

Информационная часть слова сообщения с регистра 1 через мультиплексор II и группу элементов И 9 и 10 поступает на вход того же накопителя 8 или 2 (так как группы элементов И 9 и 10 стробируются также как мультиплексоры 7 и 17 сигналами ВН и ВН) и слово сообщения записывается, например, в накопитель 8 по адресу, установленному на адресных входах накопителя 8, |при этом сигналы на входе выбора (кристалла (СЕ) накопителя 8 и на входе управления записью-чтением WE-1 формируются в блоке управления с приходом сигнала ПКСС (Признак конца слова сообщения). Сигнал WE формируется на элементе ИЛИ 49, сигнал СЕ - на элементе ИЛИ 48 (фиг.З).

Одновременно с приемом слов сообщения и их записью в накопитель 8 из накопителя 2 идет считывание информации. Адреса считывания формируются счетчиком 18 и через мультиплексор 17 поступают на адресные входы накопителя 2. Выбор накопителя по считыванию также определяется сигналами ВН . Подключение шин сигналов ВН и ВН обеспечивает выбор про- типоволожных накопителей для записи и считывания слов сообщений. Счетчик 18 формирует адреса считывания по сигналам СЧ, поступающим на вход БЗУ от приемника сообщений. Обращение к накопителю 2 по считыванию обеспечивается формированием сигналов СЕ на элементе ИЛИ 48 по сигналу СЧ, поступающему на блок 3 управления, и , так как при считывании отсутствуют сигналы СЧ1Т, ПКСС, хТР18РП на входе элемента ИЛИ 49, которые формируют сигнал WE (фиг.З). ЕСЛИ адрес сообщения, поступающий от регистра 1 через мультиплексор 12 на адресные входы БПП повторяющийся,

0

то с БПП считывается адрес фикси рованной ячейки ОЗУ (Аф.я.). Аф.я. записывается в регистр 15 и через мультиплексоры 16 и 7 поступает на адресные входы накопителя 8 (куда производится запись). Выбор шин Аф.я. мультиплексором 16 определено сигналом 18РП, считанным из БПП 14 и записанным в триггер 4 (сигнал ТР18РП). Повторяющиеся адреса слов сообщений заранее известны, поэтому в этих адресах в БПП 14 прошит 18-й разряд. По Аф.я. производится считывание

5 информации из накопителя 8. Обращение к накопителям по считыванию обеспечивается при этом формированием сигнала СЕ РЕ13-ТР18РП на элементах И 47 и ИЛИ 48 блока 3 управления

0 (фиг.З). Эта информация является адресом модификации БПП. Она поступает через мультиплексор 6 в регистр 20 адреса модификации. Мультиплексор 6 стробируется сигналом ВН, т.е. адрес

5 модификации считывается с того накопителя БЗУ, в который в данном цикле производится запись. Адрес модификации с регистра 20 поступает на мультиплексор 12 (выбор шин адреса моди0 фикации определено сигналом ТР18РП на входе установки разрядов мультиплексора 12). По адресу модификации и сигналу ОП, сформированному в блоке 3 управления на элементах И 45 и ИЛИ 51 по формуле ТР18РП, из БПП 14 считывается адрес накопителя, в который должна записываться информация, сопровождаемая переменным адресом и новый адрес модификаQ ции БПП 14, сигнал 18РП сбрасывается с БПП 14.

Новый адрес модификации, записываемый в фиксированную ячейку ОЗУ, поступает г вторых выходов БПП 14 че5 рез мультиплексор 11 и группу элементов И 9 на информационные входы накопителя 8. Так как на адресных входах накопителя 8 стоит адрес фиксированной ячейки, то запись нового

(j адреса модификации производится в фиксированную ячейку. Сигналы СЕ и WE, по которым производится запись в накопители, формируются в блоке 3 управления на элементах И 46, ИЛИ 48 и 49 соответственно по формулам: WE PE16-TP18Pn, CE PE16vTP18Pn (фиг.З). Затем триггер восемнадцатого разряда фиксированной ячейки обнуляется сигналом РЕ 22, поступающим

5

5

на триггер 4 с выхода 30 блока 3 управления. Адрес накопителя, в которы должна записываться информация, сопровождаемая повторяющимся адресом, поступает с первых выходов БГО1 через мультиплексоры 16 и 7 на адресные входы накопителя 8, На информационные входы накопителя 8 поступает слово сообщения с регистра 1 через муль типлексор 11 и группу элементов И 9 и записывается по адресу, считанному из БПП 14, при этом сигнал WE формируется в блоке управления на элементе ИЛИ 49 по сигналу ПКСС, сигнал СЕ - на элементах ИЛИ 49 и 48 и соответствует сигналу ПКСС фиг.З .

С приходом второго слова сообщения с тем же повторяющимся адресом цикл работы повторяется. При -этом считывается из накопителя адрес модификации БПП 14, записанный при работе со словом сообщения с первым повторяющимся адресом. По этому адресу считывается из БПП новый адрес моди- фикации БПП 14 и записывается в фиксированную ячейку накопителя 8 и считывается новьй адрес записи в накопитель 8 второго слова сообщений. Последнее слово сообщений данного цикла содержит адрес, являющийся признаком конца цикла. По этому адресу в БПП 14 прошит 19-й разряд, поступающий на вход 27 блока 3 управления. По нему формируются на элементах , ИЛИ 50, триггере 39 сигналы ВН и ВН по формуле РШ9-РЕ4, переключающие схемы, управляющие работой накопителей, и сами накопители. Теперь запись слов сообщений прово- дится в накопитель 2, а считывание - из накопителя 8. Если в источнике сообщений произошел необратимый сбой и в БЗУ не поступает последнее слово сообщения с адресом, являющимся при- знаком конца цикла, то РП19 с БПП 14 не считывается, сигнал РП19 РЕ4 в блоке управления не формируется, а следовательно, не формируется и сигнал элементе ИЛИ 50 и сигна- лы ВН и ВН на триггере 39.

Счетчик 18 продолжает считать поступающие на блок управления сигналы СЧ. Период формирования сигнала фиксации сообщения (А2К) с выхода дешифратора 19 много больше периода нормальной работы БЗУ, когда период РШ9 РЕ4 равен А2 к. Поэтому, если источник сообщений работает без

Q

0 5 0 о .

5

сбоев, то Сигнал на выходе дешифратора не формируется, так как счетчик 18 периодически обнуляется сигналом РП19 РЕ4. Если в источнике сообщений произошел сбой, то при накоплении в счетчике 18 состояния А2ксрабатывает дешифратор 19, сигнал с дешифратора поступает на вход 22 блока 3 управления, где на элементе ИЛИ 50 формируется сигнал МКСЗ и, соответственно, меняется поляр- с ность сигналов ВН и ВН, формируемых триггером 39, т.е. происходит считывание информации из того накопителя, куда записывалась информация сбойного цикла.

Так как в фиксированных ячейках накопителей 8 и 2 в начале работы с БЗУ произвольная информация, а в конце цикла информация, соответствующая количеству поступивших на вход в цикле повторяющихся адресов, необходимо в начале каждого цикла восстанавливать фиксированные ячейки накопителей 8 и 2 (запись в фиксированные ячейки начальных адресов модификации БПП 14). С этой целью в блок 3 управления введны триггер 40, элемент И 41, счетчики 53 и 52. После формирования сигнала МКСЗ запускается триггер 40 и на элементе И 41 формируются сигналы ТРВ ЗП. Эти сигналы поступают на счетный вход счетчика 53. Сигналы со счетчика 53 запускают счетчик 52, который формирует адреса БПП 14. Адре1- са БПП 14 с выхода 33 блока 3 управ- ления через группу 13 переключателей поступают на адресные входы БПП 14. Сигналы ОП формируются в блоке 3 управления на элементе ИЛИ 51 по сигналам со счетчика 53, поступающим на элемент ИЛИ 51 через элемент И 42. С БПП 14 считываются адреса фиксированных ячеек накопителей, поступающих через мультиплексоры 16, 7 и 17 на адресные входы накопителей 8 и 2, и начальные адреса модификации БПП 14, поступающие через мультиплексор 11 и блоки элементов И 9 и 10 на информационные входы накопителей 8 и 2. Производится запись начальных адресов модификации БПП 14 в фиксированные ячейки накопителей 8 и 2 (в каждом цикле в тот накопитель, в который производится запись слов сообщений от источника сообщений). . Сигналы, управляющие записью в накопители WE и СЕ формируются на элемену15839

так И 42, ИЛИ 48 к 49 и равны (фиг,3). После восстановления всех фиксированных ячеек накопителей триггер 40 и счетчик 52 обнуляются. Для этого в БПП 14 по окончанию восстановления прошивается 21-й разряд (конец восстановления), который поступает на вход 28 блока 3 управления, а после умножения на элементе И 44 с JQ сигналом регистра 38 (сигнал зависит от количества повторяющихся адресов на входе БЭУ) - на обнуляющие входы счетчика 53 и триггера 40.

Формула изобретения i

1. Буферное запоминающее устройство, содержащее первый и второй регистры, первую и вторую группы элементов И, два накопителя, первый счетчик, дешифратор, блок управления первый, второй и третий выходы которого соединены соответственно с входом записи первого регистра, с вто- рыми входами элементов И первой группы и вторыми входами элементов И второй группы, выходы элементов И первой и второй групп соединены соответственно с информационными входами первого и второго накопителей, вход разрешения записи блока управления является одноименным входом устройства, вход разрешения чтения блока управления соединен с выходом дешифратора, входы которого соединены с выходами первого счетчика, вход считывания которого соединен с входом задания режима блока управления и является одноименным входом устройства, счетный вход первого счетчика соединен с четвертым выходом блока управления, информационный вход первого регистра является информацион

динены с выходами младших разрядов первого регистра, информационные в ды второй группы первого мультипле сора соединены с выходами третьего регистра, входы которого соединены выходами второго мультиплексора, информационные входы первой груп которого соединены с информационны входами первой группы третьего мул типлексора и информационными выход ми второго .накопителя, информацион ные входы второй группы второго мупьтиплексора соединены с информа ционными входами второй группы тре тьего мультиплексора и информацион ными выходами первого накопителя, адресные входы которого соединены с выходами четвертого мультиплексора, информационные входы первой гру пы которого соединены с вторыми ин формационными выходами счетчика и и формационными входами первой группы пятого мультиплексора, информацион ные входы второй группы которого с динены с информационными входами второй группы четвертого мультипле сора и выходами шестого мультиплек сора, информационные входы первой группы которого соединены с первым информационными выходами блока постоянной памяти и входами четверто регистра, выходы которого соединен с информационными входами второй группы шестого мультиплексора, упр ляющий вход которого.соединен с вы дом первого триггера, с управляющи входами первого и седьмого мультиплексоров, с входом признака обращ ния блока управления, выходы старши разрядов первого регистра соединен с информационными входами первой группы седьмого мультиплексора, информационные входы второй груп

ным входом устройства, информационный 45 пы которого соединены с вторыми

выход второго регистра является информационным выходом устройства, о т- яичающееся тем, что, с целью расширения области применения за счет возможности адресации слов сообщения и модификации адресов повторяющихся слов сообщения, в него введены семь мультиплексоров, третий и четвертый регистры, первый триггер, блок постоянной памяти, группа переключателей , первые информационные входы которых соединены с выходами первого мультиплексора, информационные входы первой группы которого сое50

55

информационными выходами блока постоянной памяти, вход выборки котор го соединен с седьмым выходом блок управления, вход синхронизации конц слов которого является одноименным входом устройства, выходы седьмого мультиплексора соединены с первыми входами элементов И первой и второй групп, вход записи первого регистра соединен с управляющим входом групп переключателей, вторые информационные входы которых соединены с выходами группы блока управления, трети выход которого соединен с управляющ

101

0

5

5

0

5

0

динены с выходами младших разрядов первого регистра, информационные входы второй группы первого мультиплексора соединены с выходами третьего регистра, входы которого соединены с выходами второго мультиплексора, информационные входы первой группы которого соединены с информационными входами первой группы третьего мультиплексора и информационными выходами второго .накопителя, информационные входы второй группы второго мупьтиплексора соединены с информационными входами второй группы третьего мультиплексора и информационными выходами первого накопителя, адресные входы которого соединены с выходами четвертого мультиплексора, информационные входы первой группы которого соединены с вторыми информационными выходами счетчика и информационными входами первой группы пятого мультиплексора, информационные входы второй группы которого соединены с информационными входами второй группы четвертого мультиплексора и выходами шестого мультиплексора, информационные входы первой группы которого соединены с первыми информационными выходами блока постоянной памяти и входами четвертого регистра, выходы которого соединены с информационными входами второй группы шестого мультиплексора, управляющий вход которого.соединен с выходом первого триггера, с управляющими входами первого и седьмого мультит плексоров, с входом признака обращения блока управления, выходы старших разрядов первого регистра соединены с информационными входами первой группы седьмого мультиплексора, информационные входы второй груп5 пы которого соединены с вторыми

0

5

информационными выходами блока постоянной памяти, вход выборки которого соединен с седьмым выходом блока управления, вход синхронизации конца слов которого является одноименным входом устройства, выходы седьмого мультиплексора соединены с первыми входами элементов И первой и второй групп, вход записи первого регистра соединен с управляющим входом группы переключателей, вторые информационные входы которых соединены с выходами группы блока управления, третий выход которого соединен с управляющим

входом пятого мультиплексора, выходы которого соединены с адресными входами второго накопителя, вход выборки которого соединен с одноименным входом первого накопителя и восьмым выходом блока управления, девятый выход которого соединен с входами задания режима работы первого и второго накопителей, управляющие входы второго, третьего и четвертого мультиплексоров объединены и соединены с вторым выходом блока управления, выходы группы переключателей соединены с адресными входами блока постоянной памяти, Первый управляющий выход которого соединен с входом установки в 1 первого триггера, вход установки в О которого соединен с пятым выходом блока управления, вход признака конца цикла которого соединен с вторым управляющим выходом блока постоянной памяти, третий управляющий выход которого соединен с входом признака восстановления фиксированной ячейки блока управления, выходы третьего мультиплексора соединены с входами второго регистра.

2. Устройство по п.отличающееся тем, что блок управления содержит регистр сдвига, вход записи которого соединен с входом формирователя импульсов, первым входом первого элемента И и является входом разрешения записи блока управления, второй вход первого элемента И соединен с выходом второго триггера, вход установки в 1 которого соединен со счетным входом третьего триггера, с выходом первого элемента ИЛИ и является четвертым выходом блока управления, первый вход первого элемента ИЛИ является входом разрешения чтения блока управления, второй вход первого элемента ИЛИ соединен с выходом второго элемента .И, первый вход которого соединен с выходом четвертого разряда регистра сдвига, вход установки нуля которого соединен с третьим входом четвертого элемента ИЛИ и является входом син хронизации конца слов блока управления, второй вход второго элемента И является входом признака конца цикла блока управления, выход двадцать чет

JQ20

25

30

35

40

45

50

55

вертого разряда регистра сдвига соединен с первым входом третьего элемента И, второй вход которого является входом признака восстановления фиксированной ячейки блока управления, выход третьего элемента И соединен с входами установки в О второго триггера и второго счетчика, выходы которого являются выходами группы блока управления, счетный вход второго счетчика соединен с выходом третьего счетчика и первым входом седьмого элемента И, второй вход которого соединен с выходом формирователя импульсов и является первым- выходом блока управления, выход первого элемента И соединен со счетным входом третьего счетчика, выход двадцать второго разряда регистра сдвига является пятым выходом блока управления, прямой и инверсный выходы третьего триггера являются соответственно вторым и третьим выходами блока управления, выход десятого разряда регистра сдвига соединен с первым входом второго элемента ИЛИ, третий вход которого соединен с выходом четвертого элемента И, первый вход которого соединен с первыми входами пятого и шестого элементов И и является входом признака обращения блока управления, выход седьмого элемента И соединен с вторыми входами второго и четвертого элементов ИЛИ, выход второго элемента ИЛИ является седьмым выходом блока управления, второй вход пятого элемента И соединен с выходом шестнадцатого разряда регистра сдвига, выход тринадцатого разряда которого оединен с вторым входом шестого элемента И, выход которого соединен с первым входом третьего элемента ИЛИ, второй вход которого соединен, с выходом четвертого элемента ИЛИ и является восьмым выходом блока управления, третий вход третьего элемента ИЛИ Является входом задания режима блока управления, выход третьего элемента ИЛИ является девятым выходом блока управления, выход пятого элемента И соединен с первым входом четвертого элемента ИЛИ, второй вход четвертого элемента И соединен с выходом пятнадцатого разряда ре- гистра сдвига.

| название | год | авторы | номер документа |

|---|---|---|---|

| Буферное запоминающее устройство | 1983 |

|

SU1096692A1 |

| Буферное запоминающее устройство | 1990 |

|

SU1783581A1 |

| Буферное запоминающее устройство | 1991 |

|

SU1824651A1 |

| Буферное запоминающее устройство | 1990 |

|

SU1711233A1 |

| Процессор для мультипроцессорной системы | 1985 |

|

SU1295410A1 |

| Устройство для считывания и отображения видеоинформации | 1988 |

|

SU1817116A1 |

| Устройство для сопряжения источника и приемника информации | 1988 |

|

SU1522220A1 |

| Буферное запоминающее устройство | 1987 |

|

SU1439681A1 |

| Устройство для отладки многопроцессорных систем | 1988 |

|

SU1644145A1 |

| Устройство для вывода информации | 1983 |

|

SU1094040A1 |

Изобретение относится к области цифровой вычислительной техники и может быть использовано в устройствах передачи данных. Целью изобретения является расширение области применения за счет адресации слов сообщения и модификации адресов слов сообщения. Буферное запоминающее устройство содержит первый регистр 1, блок 3 управления, первый накопитель 8, первую и вторую группы элементов И 9, 10, первый счетчик 18, дешифратор 19, второй накопитель 2, регистр 21. Введение в устройство семи мультиплексоров 5,6,7,11,12,16,17, двух регистров 15,20, группы 13 переключателей, блока 14 постоянной памяти, триггера 4 позволяет расширить область его применения за счет совмещения операций записи в первый (второй) накопитель и чтения из второго (первого) накопителя и преобразования входного (логического) адреса цифровой информации приемника сообщений, в том числе повторяющегося в цикле передачи, в физический адрес цифровой информации приемника сообщений, работающего в реальном масштабе времени параллельно с темпом выдачи информации от источника сообщений, исключающего неизбежные потери времени на поиск информации, подлежащей передаче в приемник сообщений. 1 з.п.ф-лы, 3 ил.

Фиг.2

«sii

« I

: ;

d -L.I.l

S

t

| Буферное запоминающее устройство | 1980 |

|

SU942139A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Буферное запоминающее устройство | 1983 |

|

SU1096692A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1990-08-07—Публикация

1988-10-24—Подача