1 1

Изобретение относится к вычислительной и цифровой измерительной технике и может быть использовано для преобразования аналоговых величин в цифровые.

Цель изобретения - повышение быстродействия аналого-цифрового преобразователя.

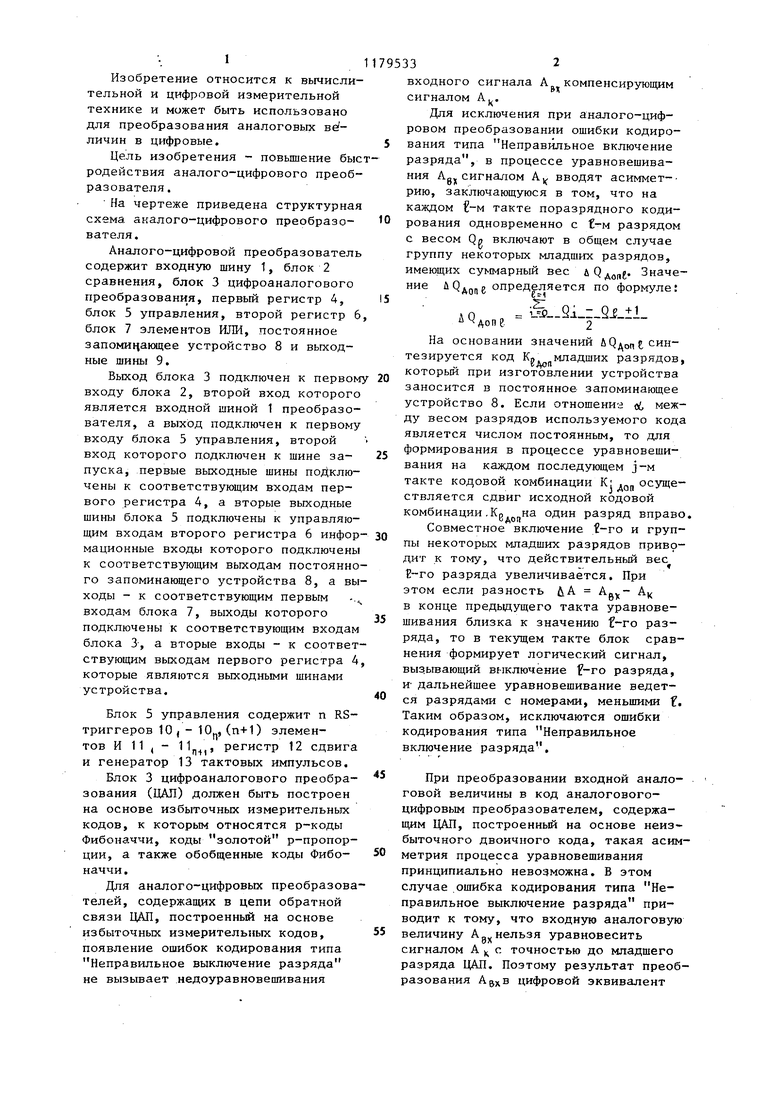

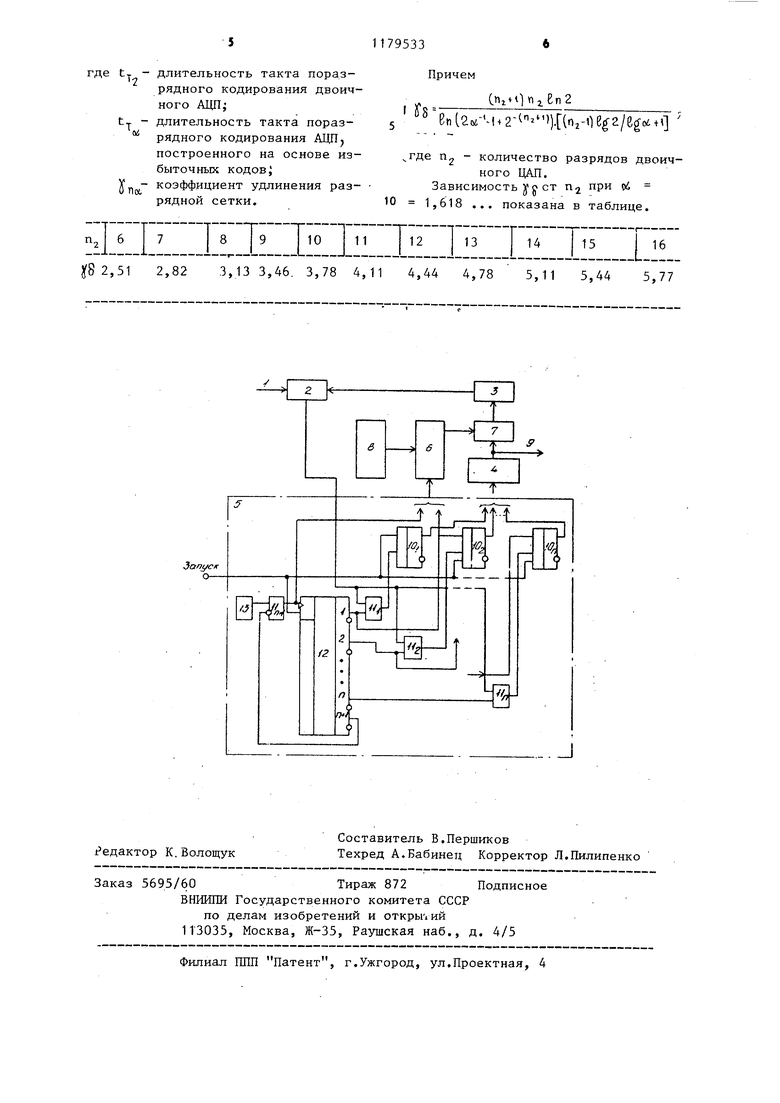

На чертеже приведена структурная схема аналого-цифрового преобразователя.

Аналого-цифровой преобразователь содержит входную шину 1, блок 2 сравнения, блок 3 цифроаналогового преобразовани я, первый регистр 4, блок 5 управления, второй регистр 6, блок 7 элементов ИЛИ, постоянное запоминающее устройство 8 и выходные шины 9.

Выход блока 3 подключен к первому входу блока 2, второй вход которого является входной шиной 1 преобразователя, а выход подключен к первому входу блока 5 управления, второй вход которого подключен к шине запуска, первые выходные шины подключены к соответствующим входам первого регистра 4, а вторые выходные шины блока 5 подключены к управляющим входам второго регистра 6 информационные входы которого подключены к соответствующим выходам постоянного запоминающего устройства 8, а выходы - к соответствующим первым -., входам блока 7, выходы которого подключены к соответствующим входам блока 3, а вторые входы - к соответствующим выходам первого регистра 4 которые являются выходными шинами устройства.

Блок 5 управления содержит п RSтриггеров 10, - 10|, (п+1) элементов И 11 , - 11p,j регистр 12 сдвига и генератор 13 тактовых импульсов.

Блок 3 цифроаналогового преобразования (ДАЛ) должен быть построен на основе избыточных измерительных кодов, к которым относятся р-коды Фибоначчи, коды золотой р-пропорции, а также обобщенные коды Фибоначчи,

Для аналого-цифровых преобразователей, содержащих в цепи обратной связи ЦАП, построенный на основе избыточных измерительных кодов, появление ошибок кодирования типа Неправильное выключение разряда не вызывает недоуравновешивания

95332

входного сигнала А компенсирующим сигналом А|.

Для исключения при аналого-цифровом преобразовании ошибки кодиро5 вания типа Неправильное включение разряда, в процессе уравновешивания Agji сигналом А вводят асиммет-рию, заключающуюся в том, что на каждом -м такте поразрядного кодирования одновременно с t-м разрядом с весом Qn включают в общем случае группу некоторых младших разрядов, имеющих суммарный вес йРдо,,. Значение лрдд определяется по формуле:

AQ.

допе 2 На основании значений AQ.Q синтезируется код К, младших разрядов, который при изготовлении устройства заносится в постоянное запоминающее устройство 8. Если отношение об между весом разрядов используемого кода является числом постоянным, то для

, формирования в процессе уравновешивания на каждом последующем j-м такте кодовой комбинации К;дд„ осуществляется сдвиг исходной кодовой комбинации,Kg на один разряд вправо. Совместное включение f-ro и группы некоторых младших разрядов приводит к тому, что действительный вес Б-го разряда увеличивается. При этом если разность uA Ац в конце предьщущего такта уравновешивания близка к значению f-ro разряда, то в текущем такте блок сравнения формирует логический сигнал, вызывающий выключение -го разряда, и- дальнейшее уравновешивание ведется разрядами с номерами, меньшими f. Таким образом, исключаются ошибки кодирования типа Неправильное включение разряда,

5 При преобразовании входной аналоговой величины в код аналоговогоцифровым преобразователем, содержащим ЦАП, построенный на основе неизбыточного двоичного кода, такая асимметрия процесса уравновешивания принципиально невозможна, В этом случае ошибка кодирования типа Неправильное выключение разряда приводит к тому, что входную аналоговую

5 величину А„ нельзя уравновесить

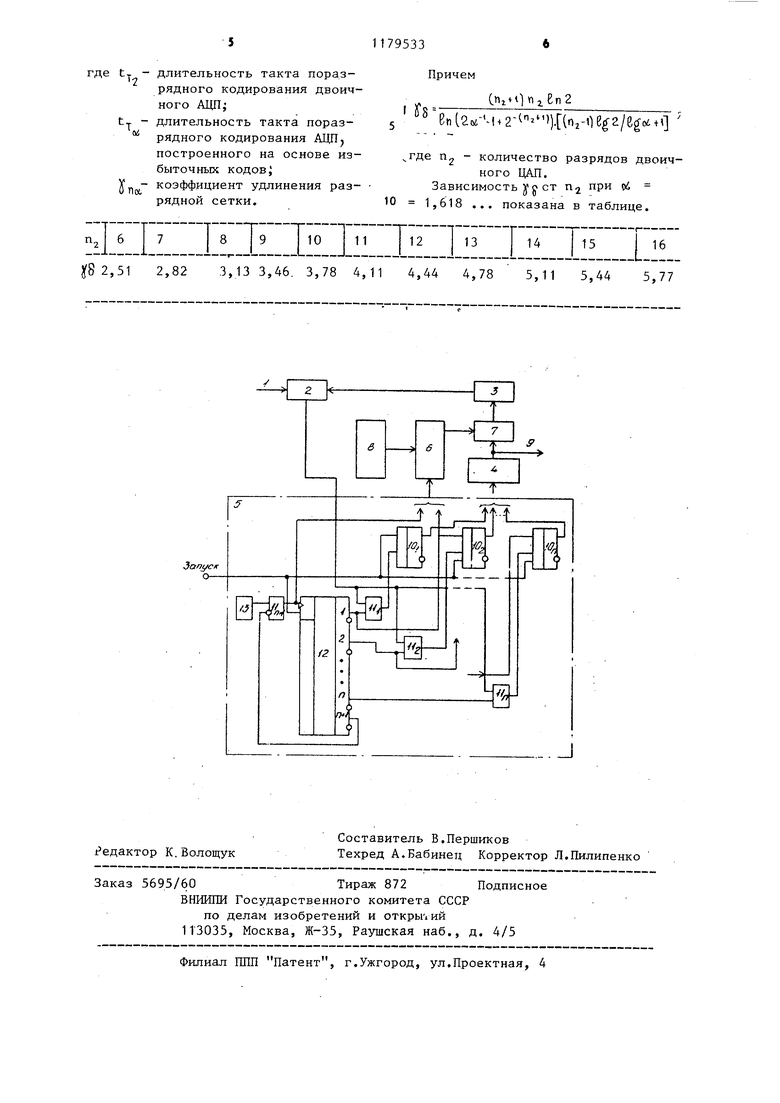

сигналом А ц с точностью до младшего разряда ЦАП. Поэтому результат преобразования цифровой эквивалент К„ неверен. Если ЦАП аналого-цифрового преобразователя реализовать на основе избыточного измерительного кода, появляется возможность осущес вить правильное аналого-цифровое преобразование при ошибках кодирования типа Неправильное выключение разрядов. Введение асимметрии в процесс уравновешивания позволяет исключить ошибки кодирования типа Неправильное включение разряда. Данные обстоятельства позволяют значительно уменьшить время каждого j-ro такта поразрядного кодирования При этом на каждом такте уравновешивания нет необходимости осуществлять точное, например до половины младшего разряда, сравнение входного Ару и компенсируюш;его А| аналоговых сигналов 4 Достаточно на один такт поразрядного уравновешивания отводить время, необходимое для установления переходных процессов в ЦАП и блоке сравнения с погрешнос тью SQ. Значение SQ зависит от избыточности кода, на основании которого построен ЦАП, и определяется по формуле: 8Q 2о: - 1, где М. - отношение между соседними членами кода на основании которого построен ЦАП. Для числа Фибоначчи при р 1, например, ( 0,61803, о.) погреш ность So равна 0 23,6%. Устройство р ботает следующим образом. На первом такте преобразования входной аналоговой величины А в код К по сигналу блока 15 управле ния устанавливается в единичное со тояние старший разряд первого регистра 4, а во второй регистр 6 из постоянного запоминающего устройства 8 записывается кодовая комбинация Кдоп,- Через блок 7 элементов ИЛ кодовые комбинации K и с выходов первого и второго регистров соответственно поступают на вход блока 3, на выходе которого появляет компенсирующий аналоговый сигнал Ak, (Qn-, - Рдсг,,). где Q h вес старшего разряда блока 3. Сравнение компенсирующего сигнала А|, и входного аналогового сигнала Agjj производится при помощи блока 2 сравнения, причем выходной сиг нал Y: этого блока подчиняется следующему соотношению: fo. если А р А j если А „ А , М KJ При этом если на первом такте уравновешивания Y О, то старший разряд первого регистра А устанавливается в нулевое состояние, если Y 1,то он остается в единичном состоянии. На втором такте аналого-цифрового преобразования по сигналу блока 5 управления содержимое второго регистра 6 сдвигается на один разряд вправо, в результате чего на выходе регистра 6 появляется кодовая комбинация Кдовз Одновременно устанавливается в единичное состояние следующий за старшим разряд в первом регистре 4. При этом на выходе блока 3 ЦАП появляется компенсирующий сигнал А. В результате сравнения входного Aj и компенсирукнцего А, аналоговых сигналов данный разряд либо устанавливается в нулевое состояние (Yj 0), либо остается в едийичном состоянии (Y 1). Устройство на любом j-м такте работает аналогично Работа устройства заканчивается на (п+1)-м такте поразрядного кодирования. При этом входной аналоговьй сигнал А gj( уравновешен компенсиРУЮЩ1™ сигналом блока 3 ЦАП А. с точностью до единицы младшего (нулевого) разряда блока 3 ЦАП и на выходной шине 9 появляется код , являющийся цифровым эквивалентом входного аналогового сигнала Agj. При реализации ЦАП на основе избыточных измерительных кодов появляется возможность увеличить быстродействие аналого-цифрового преобразователя несмотря на увеличение количества тактов преобразования, вызванного увеличением количества разрядов для избыточного измерительного кода по сравнению с двоичным кодом. Коэффициент увеличения быстродействия Yf в общем случае определяется по формуле: т.Х где t - длительность такта поразрядного кодирования двоичного АЩЦ t- - длительность такта поразрядного кодирования АЦП

построенного на основе избыточных кодов;

У - коэффициент удлинения разрядной сетки. пЛ 6 I 7 I I 9 Ъ 1 Т 82,51 2,82 3,133,46. 3,78 4,11

где п количество разрядов двоичного ЦАП. Зависимость у у ст п при о4

О 1,618 ... показана в таблице.

16 Причем (Пг «2 En 2 I If 8 en 2oi--l42- №2-1 2/e oitq 5 1 I 4,44 4,78 5,11 5,44 5,77

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь | 1984 |

|

SU1223368A1 |

| Аналого-цифровой преобразователь | 1984 |

|

SU1226664A1 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1288913A1 |

| Аналого-цифровой преобразователь | 1984 |

|

SU1221750A1 |

| Аналого-цифровой преобразователь | 1984 |

|

SU1216827A1 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1279064A1 |

| Аналого-цифровой преобразователь | 1984 |

|

SU1231609A1 |

| Способ аналого-цифрового преобразования | 1985 |

|

SU1304172A1 |

| Устройство цифроаналогового преобразования | 1984 |

|

SU1221754A1 |

| Устройство для цифроаналогового преобразования | 1984 |

|

SU1248072A1 |

1. АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ, содержащий блок сравнения, блок управления, первый регистр, блок цифроаналогового преобразования, выход которого подключен к первому входу блока сравнения, второй вход которого является входной шиной устройства, а выход подключен к первому входу блока управления, второй вход которого подключен к шине запуска, а первые выходные шины подключены к соответствующим входам первого регистра, выходы которого являются выходными шинами устройства, отличающийся тем, что, с целью повьшения быстродействия, в него введены блок элементов ИЛИ, второй регистр, постоянное запоминающее устройство, выходы которого подключены к соответствующим информационным входам второго .регистра, управляющие входы которого подключены к соответствующим вторым выходным шинам блока управления. а выходы - к соответствующим первым входам блока элементов ИЛИ, выходы которого подключены к соответствующим входам блока цифроаналогового преобразователя, а другие входы к соответствующим выходам первого . регистра. 2. Преобразователь по п. 1, о тл и ч а ю щ и и с я тем, что блок управления выполнен на генераторе тактовых импульсов, п RS-триггерах, регистре сдвига,(п+1) элементах И, первые входы п из которых объединены и являются первым входом блока управления, вторые входы подключены к соответствующим И выходам регистра (Л сдвига, вькод первого элемента И подключен к R-входу первого RS-триггера, а выходы (п-1) элементов И - к соответствующим первым R-входам соответствующих (п-1) RS-триггеров, вторые R-входы которых,первый вход регистра сдвига и S-вход первого триггера объединены и являются вторым входом блока управления, S-BXO ды (п-1) RS-триггеров подключены к ;о СП соответствующим выходам регистра сдвига, выходы п RS-триггеров являют-со ся первыми выходными шинами блока 00 управления, при этом (п+1) вькод регистра сдвига подключен к инверсному входу элемента И, прямой вход которого подключен к выходу генератора тактовых импульсов, а выход к второму входу регистра сдвига, первый выход которого и выход (п+1) элемента И являются вторыми выходными шинами блока управления.

| Балакай В.Г | |||

| и др | |||

| Интегральные схемы аналого-цифровьгх и цифроаналоговых преобразователей | |||

| М., Энергия, 1978, рис | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Железобетонный фасонный камень для кладки стен | 1920 |

|

SU45A1 |

| Гитис Э.Ио Преобразователи информации для электронных цифровых вычислительных устройств | |||

| М., Энергия, 1975, рис | |||

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

| РАССЕИВАЮЩИЙ ТОПЛИВО МЕХАНИЗМ | 1920 |

|

SU298A1 |

Авторы

Даты

1985-09-15—Публикация

1984-01-04—Подача