изобретение относится к области электроизмерительной техники.

Известны лреобразователи напряжение - код с цифровой автоматической коррекцией дрейфа нуля, содержащие входной коммутатор, нуль-орган, преобразователь имлульсов, блок синхронизации, вентили, дополнительный регистр и сумматор.

Недостатками известных устройств является сложность, обусловленная наличием дополнительного регистра для хранения кода нуля, и пониженное быстродействие, являющееся следствием дополнительных затрат времени на перенос кода нуля в дополнительный регистр и выполнение операции сложения инверсного кода нуля и прямого кода параметра.

Цель изобретения - упрощение устройства за счет исключения дополнительного регистра и повышение быстродействия за счет исключения дополнительных затрат времени на перенос кода и выполнение операции сложения кодов.

Предлагаемое устройство отличается от известных тем, что в нем запись инверсного кода нуля и прямого кода измеряемого напряжения и л и операция сложения кодов происходит одновременно с процессом преобразования нулевого напряжения и t/, для чего используются прямой и инверсный выходы

нуль-органа, которые, через логические схемы «И, «ИЛИ, «НЕ соединены со схемами «И сумматора, на вторые входы которых поступают сигналы от распределителя импульсов. Сумматор выполняется в виде м-входового однонаправленного двоичного счетчика, где п - число разрядов преобразователя.

Это позволяет сократить число элементов в схеме за счет исключения дополнительного

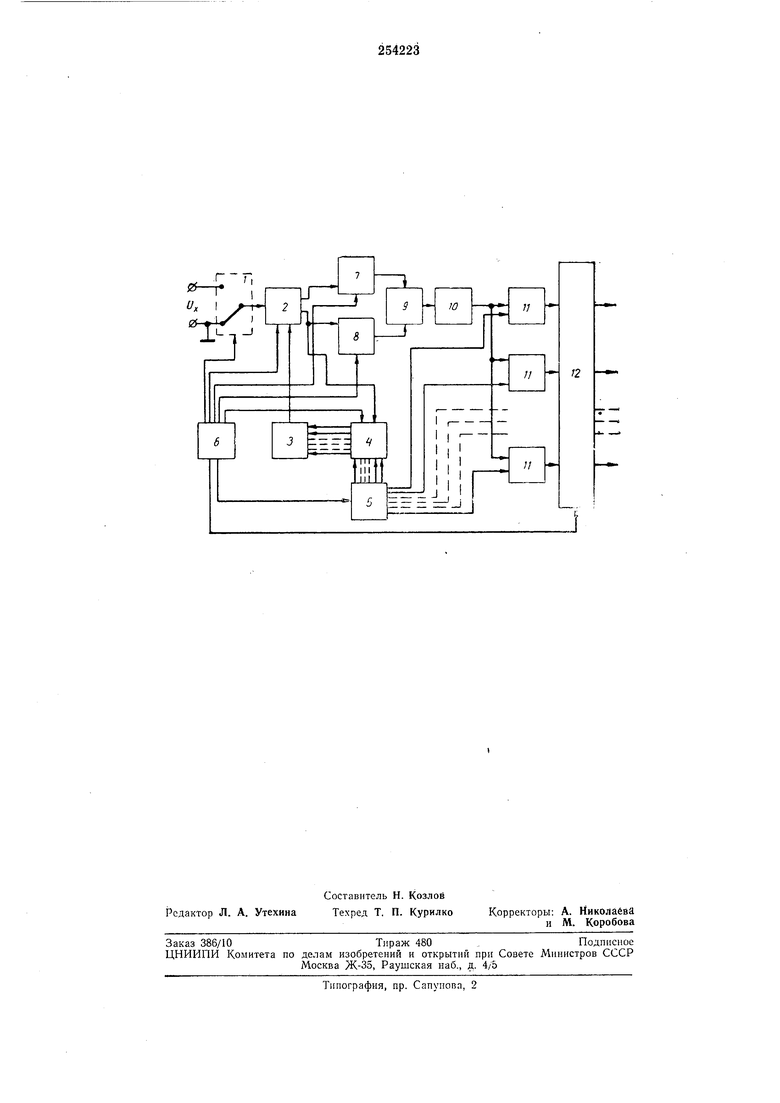

регистра кода нуля и повысить быстродействие за счет исключения затрат времени на перенос кода нуля и выполнение операции сложения кодов. Блок-схема предлагаемого устройства изображена на чертеже.

Устройство содержит входной коммутатор 1, входы которого соединены с измеряемым напряжением и нулевым потенциалом, а выход соединен с нуль-органом 2, второй вход

которого соединен с преобразователем код- напряжение 3, который п шинами соединен с регистром кода 4. Регистр кода 4 п шинами соединен с распределителем импульсов 5, одной шиной с нуль-органом 2 и одной шиной

с блоком синхронизации 6. Блок синхронизации соединен одной шиной с распределителем импульсов 5, одной шиной с входным коммутатором, одной шиной с нуль-органом 2 и двумя шинами с логическими схемами «И

нуль-органом 2. Выходы схем «И 7 и 5 присоединены к схеме «ИЛИ 9, выход которой через схему «НЕ 10 соединен с п схемами «И, //, вторые входы которых соединены /г шинами с расиределителем импульсов -5. Выходы схем «И 11 соединены с п входами сумматора 12, который одной шиной соединен с блоком синхронизации 6.

Преобразование входного напряжения 1/ в код происходит в два такта.

В нервом такте через коммутатор 1 на нуль-орган 2 поступает нулевое напряжение. При этом входным нанряжением t/вх, подлежащим преобразованию в код, является сумма напряжений смещения порога срабатывания и дрейфа нуля нуль-органа. Процесс преобразования напряжения t/вх в код осуществляется поразрядным методом, при котором распределитель импульсов-5 поочередно, начиная со старшего, включает разряды регистра кода 4. При. этом преобразователь код- напряжение вырабатывает эталонные уровнинапряжения /эт. которые сравниваются с напряжением и вх нуль-органом 2. Состояние нуль-органа 2 опрашивается импульсами бло-; ка синхронизации 6 и ири нульорган 2 выдает сигнал на сброс включенной ступени эталонного напряжения.

Запись инверсного кода нуля осуществляется следующим образом. Блок синхронизации в первом такте выдает разрешающий сигнал на схему «И 8, которая через схемы «ИЛИ 9 и «ИЕ 10 подает на схемы «И 11 сумматора 12 инверсный выход нуль-органа 2, т. е. выход, на котором есть разрешаЕОЩий потенциал, или импульс при вх- При наличии импульса на инверсном выходе нуль-органа в разряде сумматора, который s данный момент выбран тактовым имнульсом распределителя, будет записана «1. В случае потенциального выхода нуль-органа запись «1 в разряд сумматора производится импульсом, соответствующим концу тактового интервала. По окончании такта кодирования в сумматоре записан инверсным кодом числовой эквивалент, соответствующий напряжению смещения характеристики преобразователя напряжение - код.

Во втором такте через коммутатор / на вход нуль-органа 2 поступает нанряжение

Ujf , блок синхронизации 6 выдает разрешающий сигиал на схему «И 7, которая через схемы «ИЛИ 9 и «НЕ 10 подает на схемы «И 11 сум;матора 12 прямой выход нуль-органа, т. е. выход, на котором появляется разрешающий потенциал или импульс при f/8T ; При этом одновременно происходит поразрядная запись кода U.,, в сумматор и сложение кода Ujf с инверсным кодом нуля в сумматоре.

По окончании второго такта преобразования на выходе сумматора устанавливается скорректированный код, соответствующий напрялсепию иjf.

Систематическая ощибка в один квант, которая должна была бы образс1 ваться в результате замены операции вычитания операцией сложения прямого кода уменьшаемого с инверсным кодом вычитаемого, устраняется начальной установкой младшего разряда сумматора в «1.

При использовании описанного устройства для многоточечных измерений с числом выходных заноминающих регистров, равным числу точек, в качестве запоминающего регистра используется описанный многовходозой счетчик с заменой двухвходовых схем «И на трехвходовые, причем на третий вход схемы «И подается импульс выбранного капала. При этом наличие цифровой коррекции нуля практически не увеличивает объем преобразователя без коррекции.

Предмет изобретения

Преобразователь напрял ение - код с цифровой автоматической коррекцией дрейфа нуля, содержащий входной коммутатор, нульорган, преобразователь код - напряжение, регистр кода, распределитель импульсов, блок синхронизации, логические схемы «И, «ИЛИ, «НЕ и сумматор, отличающийся тем, что, с целью повышения быстродействия и унрощения устройства, в нем прямой и инверсный выходы нуль-органа через схемы «И, вторые входы которых соединены с блоком синхронизации, подключены к схеме выход последней через схему «ПЕ и схемы «И, вторые входы которых подключены к распределителю импульсов, соединен со входом сумматора.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПРЕОБРАЗОВАТЕЛЬ НАПРЯЖЕНИЕ — КОД С ЦИФРОВОЙ АВТОКОРРЕКЦИЕЙ НУЛЯ | 1967 |

|

SU196452A1 |

| Устройство для вычисления показателя экспоненциальной функции | 1983 |

|

SU1129611A1 |

| Аналого-цифровой преобразователь интегральных характеристик электрических величин | 1981 |

|

SU1035790A1 |

| Устройство для вычисления показателя экспоненциальной функции | 1982 |

|

SU1043677A1 |

| Функциональный преобразователь | 1983 |

|

SU1108442A1 |

| Электропривод | 1987 |

|

SU1476584A1 |

| Преобразователь кодов | 1978 |

|

SU744548A1 |

| Устройство для вычисления элементарных функций | 1984 |

|

SU1168930A1 |

| Инкрементный умножитель аналоговых сигналов | 1983 |

|

SU1113820A1 |

| Устройство для вычисления полиномиальной функции от аналогового аргумента | 1990 |

|

SU1737444A1 |

Даты

1969-01-01—Публикация