1

Изобретение относится к вычислительной технике.

Известен накапливающий сумматор параллельного действия, содержащий триггеры, вентили, дифференцирующие цепочки, элементы задержки и схемы «ИЛИ.

Предложенный сумматор отличается тем, что в нем межразрядные цепи переносов выполнены в виде двух параллельно соединенных и подключенных к схеме «ИЛИ цепочек, одна из которых содержит последовательно соединенные вентиль и элемент задержки, а вторая- вентиль, причем управляющие входы вентилей подключены к шинам управляющих импульсов. Это позволяет повысить быстродейСтвие сумматора.

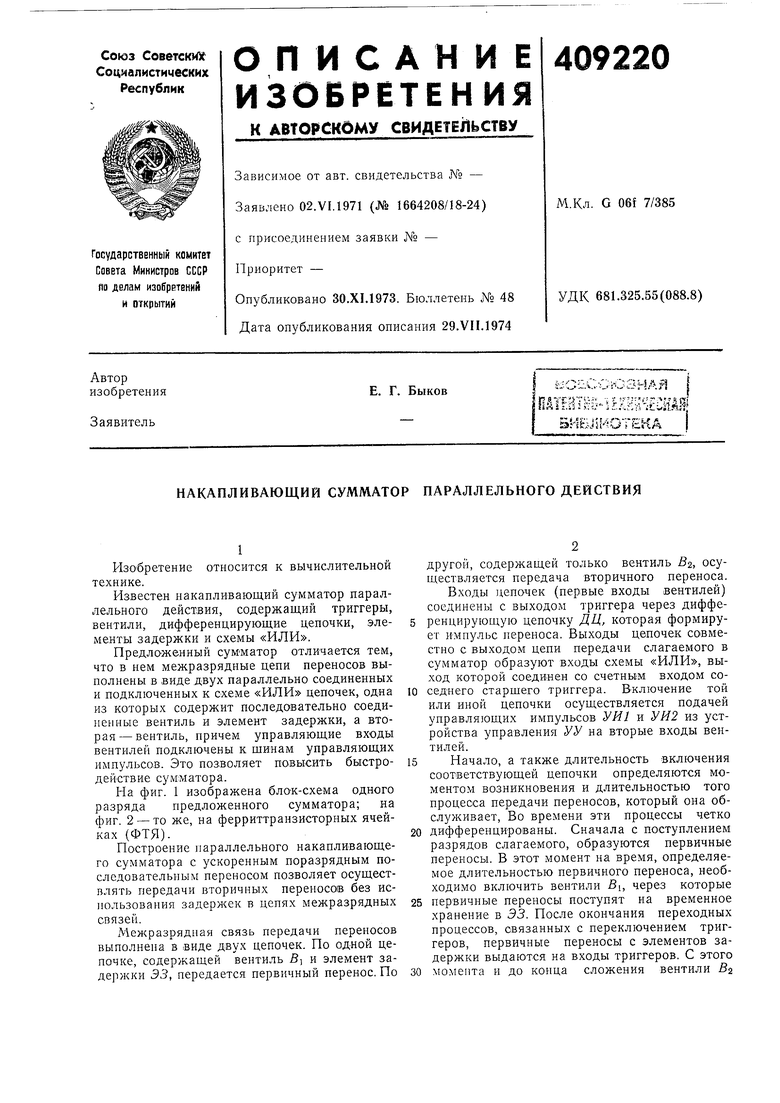

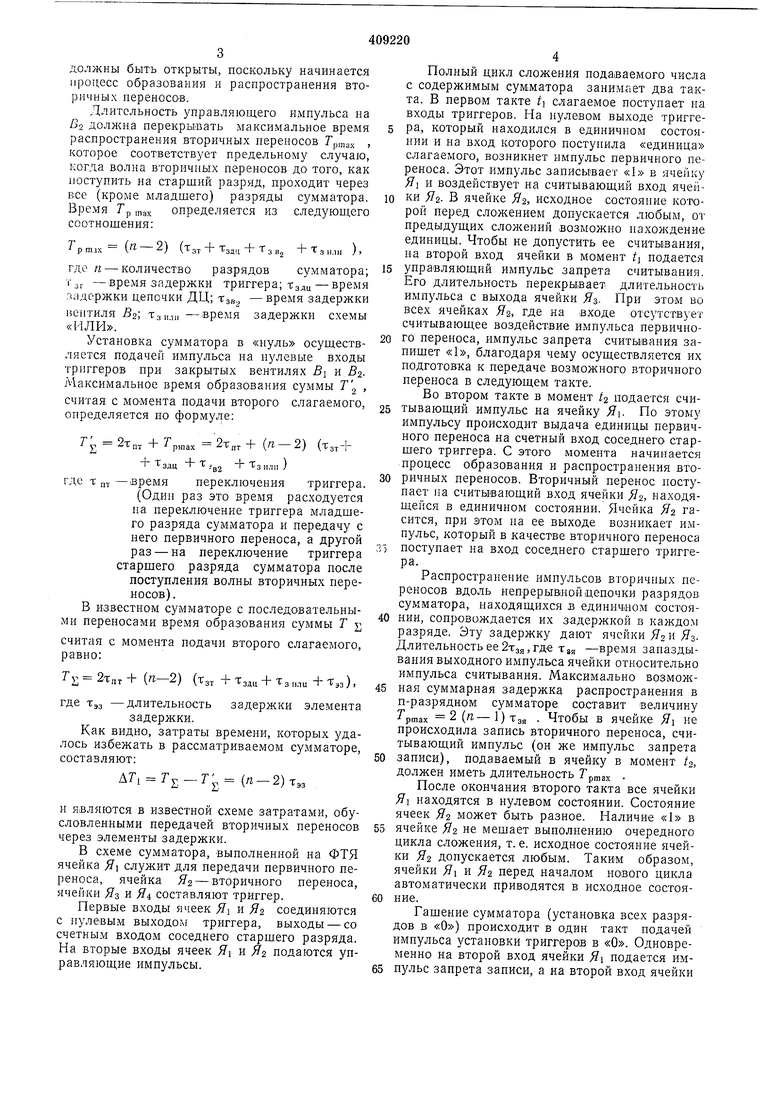

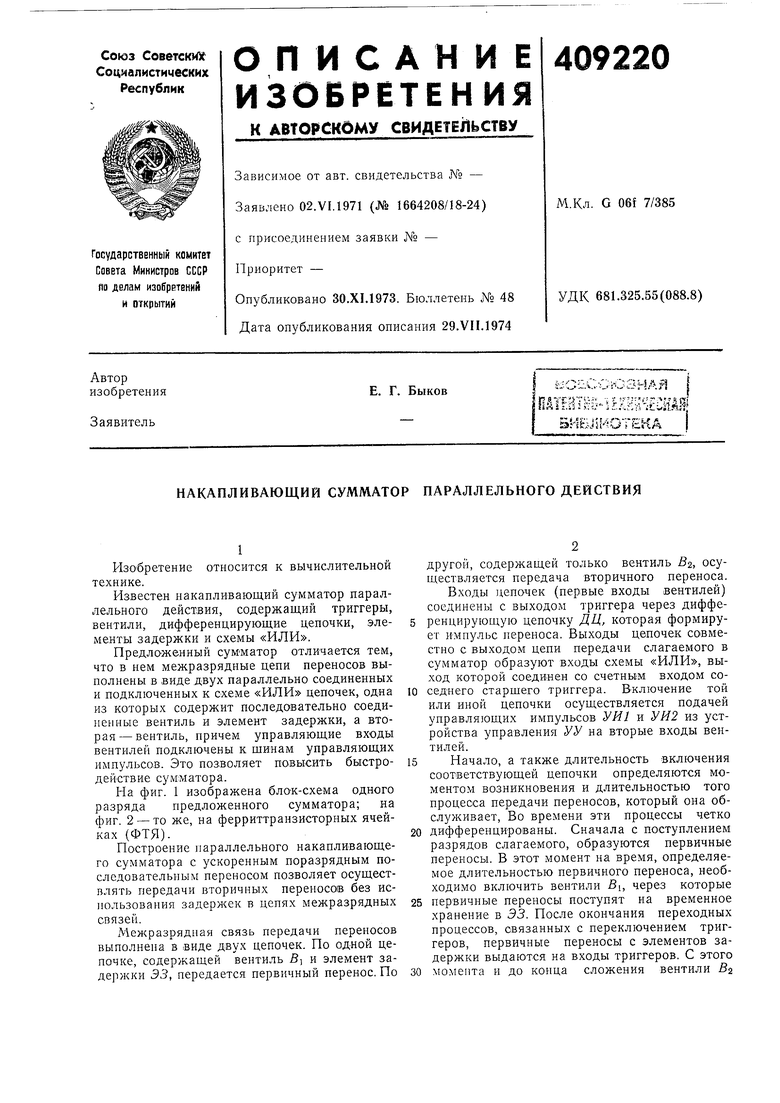

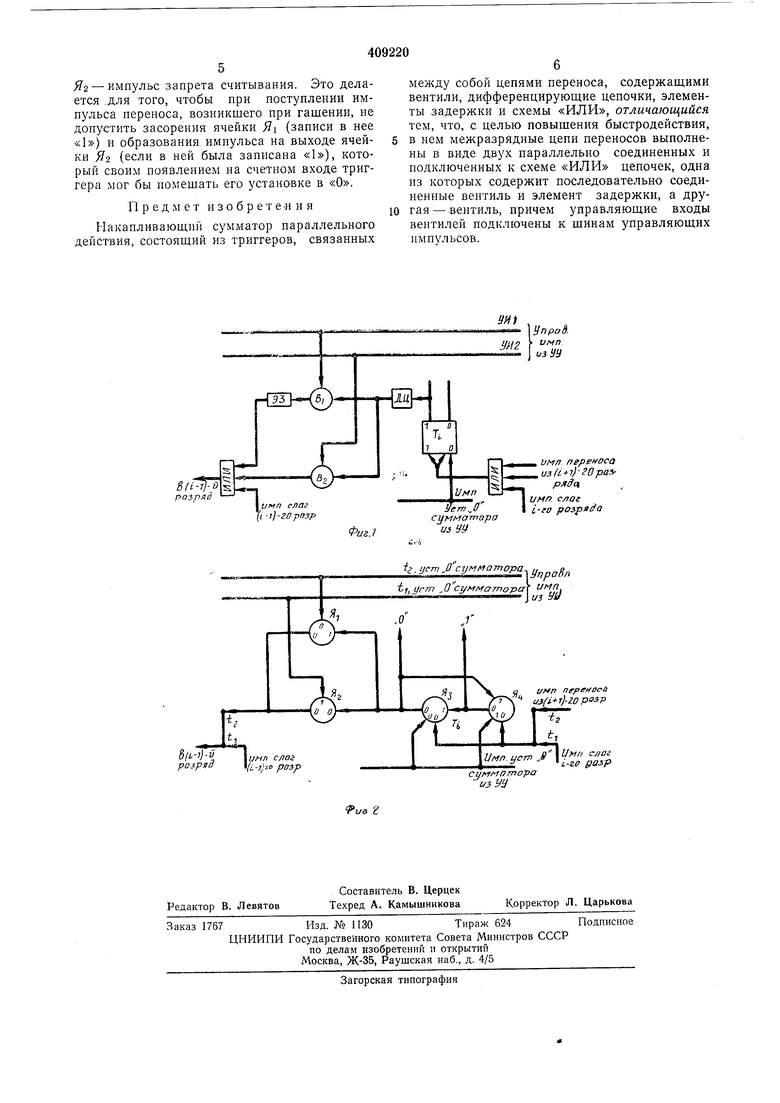

Па фиг. 1 изображена блок-схема одного разряда предложенного сумматора; на фиг. 2 -то же, на ферриттранзисторных ячейках (ФТЯ).

Построение параллельного накапливающего сумматора с ускоренным поразрядным последовательным переносом позволяет осуществлять передачи вторичных переносов без использования задержек в цепях межразрядных связей.

Межразрядная связь передачи переносов выполнена в виде двух цепочек. По одной цепочке, содержащей вентиль В) и элемент задержки 33, передается первичный перенос. По

другой, содержащей только вентиль В, осуществляется передача вторичного переноса. Входы цепочек (первые входы вентилей) соединены с выходом триггера через дифференцирующую цепочку ЦЦ, которая формирует импульс переноса. Выходы цепочек совместно с выходом цепи передачи слагаемого в сумматор образуют входы схемы «ИЛИ, выход которой соединен со счетным входом соседнего старшего триггера. Включение той или иной цепочки осуществляется подачей управляющих импульсов УИ1 и УИ2 из устройства управления УУ на вторые входы вентилей.

Пачало, а также длительность включения соответствующей цепочки определяются моментом возникновения и длительностью того процесса передачи переносов, который она обслуживает. Во времени эти процессы четко

дифференцированы. Сначала с поступлением разрядов слагаемого, образуются первичные переносы. В этот момент на время, определяемое длительностью первичного переноса, необходимо включить вентили BI, через которые

первичные переносы поступят на временное хранение в ЭЗ. После окончания переходных процессов, связанных с переключением триггеров, первичные переносы с элементов задержки выдаются на входы триггеров. С этого

момента и до конца сложения вентили В

должны быть открыты, поскольку начинается процесс образования и распространения вторичных переносов.

Длительность управляющего импульса на Да должна перекрывать максимальное время распространения вторичных переносов Гршах которое соответствует предельному случаю, когда волна вторичных переносов до того, как поступить на старший разряд, проходит через все (кроме младшего) разряды сумматора. Вре.мя Ту шах определяется из следуюш,его соотношения:

р mix - ( ) ( Г

3 или /

Здц Г Т 3 1

где п - количество разрядов сумматора; Тзг -время задержки триггера; Тздц - время (держки цепочки ДЦ; TSB.J -время задержки ентиля BS; Тзтл -время задержки схемы «ИДИ.

Установка сумматора в «нуль осуществляется подачей импульса на нулевые входы триггеров при закрытых вентилях 5; и 2. Максимальное время образования суммы Tg , считая с момента подачи второго слагаемого, определяется по формуле:

Т 2т п, + 2т„, + (я-2) (тзт-1 1 ЗДЦ 1 -в2 ЗИЛП j

где Т пт-время переключения триггера. (Один раз это время расходуется па переключение триггера младшего разряда сумматора и передачу с него первичного переноса, а другой раз - на переключение триггера старшего разряда сумматора после поступления волны вторичных переносов).

В известном сумматоре с последовательными переносами время образования суммы Г

считая с момента подачи второго слагаемого, равно:

ТЕ 2Тлт + («-2) (Тзт + Тздц + Тзмли + Тэз),

где Тэз -длительность задержки элемента

задержки.

Как видно, затраты времени, которых удалось избежать в рассматриваемом сумматоре, составляют:

АГ1 Г,;,-7 (я-2)тэз

и являются в известной схеме затратами, обусловленными передачей вторичных переносов через элементы задержки.

В схеме сумматора, выполненной на ФТЯ ячейка Я служит для передачи первичного переноса, ячейка 2 - вторичного переноса, ячейки Яз и Я4 составляют триггер.

Первые входы ячеек Я и Яг соединяются с пулевым ВЫХОДОМ триггера, выходы - со счетным входом соседнего старшего разряда. На вторые входы ячеек Яг и Яг подаются управляющие импульсы.

Полный цикл сложения подаваемого числа с содержимым сумматора занимает два такта. В первом такте ti слагаемое поступает на входы триггеров. На нулевом выходе триггера, который находился в единичном состоянии и на вход которого поступила «единица слагаемого, возникнет импульс первичного переноса. Этот импульс записывает «1 в ячейку Я и воздействует на считывающий вход ячейки Я2. В ячейке Я2, исходное состояние которой перед сложением допускается любым, от предыдущих сложений возможно нахождение единицы. Чтобы не допустить ее считывания, на второй вход ячейки в момент ti подается

управляющий импульс запрета считывания. Его длительность перекрывает длительность импульса с выхода ячейки Яз. При этом во всех ячейках Яз, где на входе отсутствует считывающее воздействие импульса первичного переноса, импульс запрета считывания запишет «Ь, благодаря чему осуществляется их подготовка к передаче возможного вторичного переноса в следующем такте.

Во втором такте в момент /г подается считывающий импульс на ячейку Яь По этому импульсу происходит выдача единицы первичного переноса на счетный вход соседнего старшего триггера. С этого момента начинается процесс образования и распространения вторичных переносов. Вторичный перенос поступает на считывающий вход ячейки Яг, находящейся в единичном состоянии. Ячейка Я2 гасится, при этом на ее выходе возникает импульс, который в качестве вторичного переноса

поступает на вход соседнего старшего триггера.

Распространение импульсов вторичных переносов вдоль непрерывной цепочки разрядов сумматора, находящихся в единичном состояНИИ, сопровождается их задержкой в каждом разряде. Эту задержку дают ячейки Яа и ЯзДлительностьее2тзя,гд€ Тая -время запаздывания выходного импульса ячейки относительно импульса считывания. Максимально возможная суммарная задержка распространения в п-разрядном сумматоре составит величину ршах 2(п-1)тзя Чтобы В ячбйке Я1 не происходила запись вторичного переноса, считывающий импульс (он же импульс запрета

записи), подаваемый в ячейку в момент /а, должен иметь длительность

После окончания второго такта все ячейки Я) находятся в нулевом состоянии. Состояние ячеек Я2 может быть разное. Наличие «1 в

ячейке Я2 не мешает выполнению очередного цикла сложения, т. е. исходное состояние ячейки Я2 допускается любым. Таким образом, ячейки Я: и Яг перед началом нового цикла автоматически приводятся в исходное состояние.

Гащение сумматора (установка всех разрядов в «О) происходит в один такт подачей импульса установки триггеров в «О. Одновременно на второй вход ячейки Я1 подается импульс запрета записи, а на второй вход ячейки

Яч - импульс запрета считывания. Это делается .для того, чтобы при поступлении импульса переноса, возникшего при гашении, не допустить засорения ячейки Я (записи в нее «1) и образования импульса на выходе ячейки Я2 (если в ней была записана «1), который своим появлением на счетном входе триггера мог бы помешать его установке в «О.

Предмет изобретения

Ыакапливаюшн сумматор параллельного действия, состояший из триггеров, связанных

между собой цепями переноса, содержаш,ими вентили, дифференцирующие цепочки, элементы задержки и схемы «ИЛИ, отличающийся тем, что, с целью повышения быстродействия, в нем межразрядные цепи переносов выполнены в внде двух параллельно соединенных и подключенных к схеме «ИЛИ цепочек, одна из которых содержит последовательно соединенные вентиль и элемент задержки, а другая- вентиль, причем управляющие входы вентилей подключены к шинам управляющих импульсов.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПАРАЛЛЕЛЬНЫЙ НАКАПЛИВАЮЩИЙ СУММАТОР СО СКВОЗНЫМ ПЕРЕНОСОМ НА ФЕРРИТ-ТРАНЗИСТОРНЫХЯЧЕЙКАХ | 1967 |

|

SU203320A1 |

| К-значный фазоимпульсный сумматор | 1971 |

|

SU450163A1 |

| Параллельный сумматор | 1981 |

|

SU1018114A1 |

| СУММАТОР В КОДЕ ГРЕЯ | 1965 |

|

SU172131A1 |

| НАКАПЛИВАЮЩИЙ СУММАТОР С ФИКСАЦИЕЙ ОШИБКИПЕРЕНОСА | 1968 |

|

SU208338A1 |

| КОМБИНИРОВАННАЯ ЦИФРОВАЯ ВЫЧИСЛИТЕЛЬНАЯ МАШИНА | 1966 |

|

SU224910A1 |

| Анализатор спектра Фурье | 1985 |

|

SU1302293A1 |

| КОМБИНАЦИОННО-НАКАПЛИВАЮЩИЙ СУММАТОР | 2005 |

|

RU2292073C1 |

| НАКАПЛИВАЮЩИЙ ДЕСЯТИЧНЫЙ СУММАТОР | 1966 |

|

SU224164A1 |

| Цифровое вычислительное устройство | 1979 |

|

SU826359A1 |

р

м-v

озрао

ynpaS.

т -UMf переноса vз(i-) OpaЛ ряЗс

VMn слог

Уетп.О pospxcfa симиогпора

UiW

Фаг.

г.цсп, /сумматора ,

,уст .,0 cyMf fO7nopa

ySa

I из

a имп переноса yiu.. .1

iJi()-20 розР

г

t,

г/л...у..

тлора изУУ

Даты

1973-01-01—Публикация