Устройство относится к области вычислительной техники и предназначено для суммирования и вычитания двоичных чисел, а также для суммирования и вычитания последовательностей импульсов (реверсивный счет).

Известны накапливающие сумматоры, в которых для вычитания двоичных чисел требуется предварительное преобразование поступающего на сумматор кода числа в дополнительный код, а операция реверсивного счета выполняется как обычное сложение и вычитание, т. е. является двухтактной.

Предложенное устройство отличается тем, что выходы триггеров каждого разряда регистра соединены через элементы «И со входами элемента «ИЛИ, причем другой вход каждого из этих элементов «И соединен с шиной сложения пли вычитания схемы управления; выход элемента «ИЛИ соединен с выходными элементами «И, один из которых соединен входу с цепью переноса предыдущего разряда сумматора, а по выходу - с выходным элементом другой из выходных элементов «И соединен по входу также со входом данного разряда сумматора, а по выходу соединен через элемент задержки с тем же выходным элементом «ИЛИ, выход которого соединен через входной элемент «ИЛИ со счетным входом триггера последующего разряда регистра И служит выходом цепи переноса данного

разряда; вход сумматора по цепи реверсивного счета соединен с выходным элементом «И и входным элементом «ИЛИ младщего разряда.

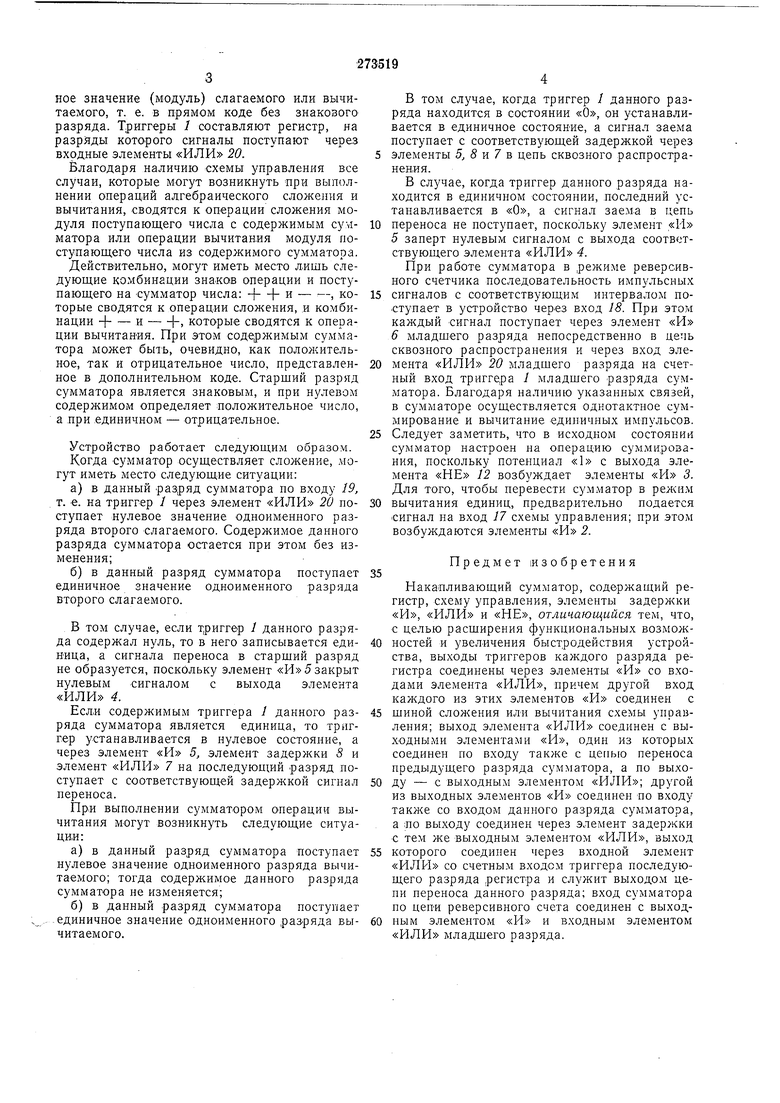

Это позволяет расширить функциональные возможности устройства за счет выполнения алгебраического сложения и вычитания двоичных чисел без предварительного преобразования кода поступающего числа в дополнительный код и выполнения операции реверсивного счета, а также повысить быстродействие благодаря тому, что реверсивный счет выполняется как однотактная операция. Схема описываемого сумматора изображена

на чертеже.

Каждый разряд сумматора, кроме старшего, содержит триггер /, элементы «И 2 и 3, элемент «ИЛИ 4, выходные элементы «И 5 и 6, выходной элемент «ИЛИ 7, линию задержки

S; устройство содержит также схему управления на элементах «И 9, 10, «ИЛИ 11, «НЕ 12, а также входы для подачи сигналов: 13- при поступлении на сумматор отрицательного числа; 14 - при поступлении на сумматор положительного числа; 15 - операции сложения; 16 - операции вычитания; 17 - режим вычитания при счете; через вход 18 на сумматор поступает последовательность импульсов при работе в режиме реверсивного счета; ченое значение (модуль) слагаемого или вычитаемого, т. е. в прямом коде без знакового разряда. Триггеры / составляют регистр, на разряды которого сигналы поступают через входные элементы «ИЛИ 20.

Благодаря наличию схемы управления все случаи, которые могут возникнуть при выполнении операций алгебраического сложения и вычитания, сводятся к операции сложения модуля поступающего числа с содержимым сумматора или операции вычитания модуля поступающего числа из содержимого сумматора.

Действительно, могут иметь место лишь следующие комбинации зна-кав операции и поступающего на сумматор числа: -|-h и - -, которые сводятся к операции сложения, ,и комбинации -|и1-, которые сводятся к операции вычитания. При этом содержимым сумматора может быть, очевидно, как положительное, так и отрицательное число, представленное в дополнительном коде. Старший разряд сумматора является знаковым, и при нулевом содержимом определяет положительное число, а при единичном - отрицательное.

Устройство работает следующим образом. Когда сумматор осуществляет сложение, могут иметь место следующие ситуации:

а)в данный разряд сумматора по входу 19, , т. е. на триггер / через элемент «ИЛИ 20 поступает нулевое значение одноименного разряда второго слагаемого. Содержимое данного разряда сумматора остается при этом без изменения;

б)в данный разряд сумматора поступает единичное значение одноименного разряда второго слагаемого.

В том случае, если триггер 1 данного разряда содержал нуль, то в него записывается единица, а сигнала переноса в старший разряд не образуется, поскольку элемент «И 5 закрыт нулевым сигналом с выхода элемента «ИЛИ 4.

Если содержимым триггера / данного разряда сумматора является единица, то триггер устанавливается в нулевое состояние, а через элемент «И 5, элемент задержки S и элемент «ИЛИ 7 на последующий разряд поступает с соответствующей задержкой сигнал переноса.

Прп выполнении сумматором операции вычитания МОгут возникнуть следующие ситуации:

а)в данный разряд сумматора поступает нулевое значение одноименного разряда вычитаемого; тогда содержимое данного разряда сумматора не изменяется;

б)в данный разряд сумматора поступает -единичное значение одноименного разряда вычитаемого.

В том случае, когда триггер / данного разряда находится в состоянии «О, он устанавливается в единичное состояние, а сигнал заема поступает с соответствующей задержкой через элементы 5, S и 7 в цепь сквозного распространения.

В случае, когда триггер данного разряда находится в единичном состоянии, последний устанавливается в «О, а сигнал заема в цепь переноса не поступает, поскольку элемент И

5заперт нулевым сигналом с выхода соответствующего элемента «ИЛИ 4.

Ири работе сумматора в режиме реверсивного счетчика последовательность импульсных сигналов с соответствующим интервалом поступает в устройство через вход 18. При этом сигнал поступает через элемент «И

6младшего разряда непосредственно в цепь сквозного распространения и через вход элемента «ИЛИ 20 младшего разряда на счетный вход триггера 1 младшего разряда сумматора. Благодаря наличию указанных связей, в сумматоре осуществляется однотактное суммирование и вычитание единичных импульсов.

Следует заметить, что в исходном состояния сумматор настроен на операцию суммирования, поскольку потенциал «1 с выхода элемента «НЕ 12 возбуждает элементы «И 3. Для того, чтобы перевести сум матор в режим

вычитания единиц, предварительно подается сигнал на вход 17 схемы управления; при этом возбуждаются элементы «И 2.

Предмет (изобретения

Иакацливающий сумматор, содержащий регистр, схему управления, элементы задержки «И, «ИЛИ и «НЕ, отличающийся тем, что, с целью расширения функциональных возможностей и увеличения быстродействия устройства, выходы триггеров каждого разряда регистра соединены через элементы «И со входами элемента «ИЛИ, причем другой вход каждого из этих элементов «И соединен с

шиной сложения ИЛИ вычитания схемы управления; выход элемента «ИЛИ соединен с выходны.ми элементами «И, один из которых соединен по входу также с цепью переноса предыдущего разряда сумматора, а по выходу - с выходным элементом другой из выходных элементов «И соединен по входу также со входом данного разряда сумматора, а по выходу соединен через элемент задержки с тем же выходным элементом «ИЛИ, выход

которого соединен через входной элемент «ИЛИ со счетным входом триггера последующего разряда регистра и служит выходом цепи переноса данного разряда; вход сумматора по цепи реверсивного счета соединен с выходным элементом «И и входным элементом «ИЛИ младшего разряда.

7 5

гЯР-От

770

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой синтезатор функций | 1980 |

|

SU879609A2 |

| Арифметическое устройство | 1989 |

|

SU1656525A1 |

| Вероятностное устройство для сложения двух чисел | 1973 |

|

SU485446A1 |

| ДВОИЧНОЕ АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО | 1968 |

|

SU210491A1 |

| ДВОИЧНО-ДЕСЯТИЧНОЕ СУММИРУЮЩЕЕ УСТРОЙСТВО | 1968 |

|

SU220631A1 |

| Устройство для преобразования кодов | 1977 |

|

SU744544A1 |

| Функциональный генератор напряжения | 1976 |

|

SU734746A2 |

| СУММАТОР В КОДЕ ГРЕЯ | 1965 |

|

SU172131A1 |

| ГЕНЕРАТОР ДУГ ОКРУЖНОСТЕЙ | 1973 |

|

SU397902A1 |

| Преобразователь активной мощностиВ КОличЕСТВО иМпульСОВ | 1979 |

|

SU845109A1 |

Даты

1970-01-01—Публикация