Изобретение относится к области цифровой вычислительной техники и может быть использовано в арифметических устройствах ЦВМ. Известны накапливающие сумматоры, фор мирование сигнала переноса в которых зависит от времени перюключения триггеров накапливающего регистра, что существенно снижает быстродействие сумматора 1 , 2 Известны также накапливающие сумматоры со сквозным переносом. Для формирования поразрядного и сквозного переносов в каждом двоичном разряде таких сумматоров требуется два логических элемента И и один элемент ИЛИ. Кроме того, такие накапливающие сумматоры должны иметь в каждом разряде на входе триггера накапливающего регистра элемент задержки, что снижает быстродействие сумматора и увеличивает количество оборудования 3, 4 5J. Наиболее близким аналогом данного изоб ретения является двухтактный сумматор параллельного действия, содержащий триггер- ный накапливающий регистр, триггерный приемный регистр, элементы И и ИЛИ, причем в каждом разряде ед1шичный выход триггера приемного регистра подключен к первым входам первого и второго элементов И, ко второму входу второго элемента И, подключена Щ1ша разрещения выдачи кода из приемного регистра, а выход его соединен с первым входом первого элемента ИЛИ , второй вход которого соединен с выходом третьего элемента И, первый вход которого подключен к выходу переноса из младшего разряда, а второй - к щине разрещения сложения. Выход первого элемента ИЛИ подключен к счетному входу триггера накапливающего регистра 6 . В этом сумматоре для его правильной работы принципиально необходимо наличие элемента задержки на входе триггера накапливающего регистра, что увеличивает количество оборудования сумматора и снижает его быстродействие. Целью изобретения является сокращение количества оборудования и повыщение быстродействия. Кроме того, целью изобретения является расщирение функциональных возможностей устройства, т, &, выполнение операций логического сложекия и логического умножения.

Эта цель достигается тем, что единичный выход триггера накапливающего регистра подключен к первому входу четвертого элемента И, ко второму входу которого подключена шина разрешения приема кода в приег шый регистр из накапливающего регистра, а выход его подключен к единичному входу триггера приемного регистра, нулевой выход триггера накапливающего регистра подкгаочен к первому входу второго элемента ИЛИ, ко второму входу которог подключен выход переноса из младшего разряда, а выход соединен со вторым входом первого элемента И, выход которого является выходом переноса из данного разряда,

Ка чертеже приведена схема двух разрядов сумматора параллельного действия.

Он содержит элементы И элементы ИЛИ 5; 6; накапливающий регистр образовшшый триггерами 7 всех разрядов, и прие1ушый регистр, образоватшый триггерами 8; шш1у 9 разрешения выдачи кода из приемного регистра; Ю разрешени сложения и шину i 1 разрешения приема кода в приемный регистр из накапливающег регистра

Кулевой выход триггера 7 подключен к первому входу элемента ИЛИ 5, ко второму входу которого подключен выход элемента И 1 младшего разряда. Выход элемента ИЛИ о подключен к входу элемента И 1, второй вход которо1 о связан с единичным вь ходом. триггера 8, Единичный выход триггера 7 соединен с выходом элe ieнтa И 4, второй вход которого подключен к шине llu Выход элемента И 4 связан с едршичным входом триггера 8, единичный выход которого подключен к первому входу элемента И 2, ко входу которого подключена шина 9 разрешения выдачи кода из приемного регистра. Выход элемента И 2 соединен с первым входом элемента ИЛИ 6, со вторым входом которого соединен элемента И 3, Выход элемента ИЛИ 6 подключен к счетному входу триггера 7, Выход элемента И 1 предыдущего разряда подключен к первому входу элемента И 3, ко второму входу которого подключена шина 10,

При выполнении операции сложения сумматор работает следующим образом.

Пусть в накапливающем регистре хранится код первого слагаемого, а в приемный регистр занесено второе слагаемое ( оба числа положительные).

По первому временному такту (f , ) осуществляется операция сложения по M.O

дулю два. Для этого на Ш1шу 9 подается исполнительный импульс. Если в триггере 8 любого разряда хранится код единицы, то элемент И 2. этого разряда открыт и на счетный вход триггера 7 поступает импульс, который производит инвертировани этого триггера.

(i)

По второму временному такту выполняется операция логического сложени первого и второго слагаемых. Для этого на шину 11 подается импульс, за счет чего код, хранящийся в накапливающем регистре, накладывается на код второго слагаемого. При этом второй такт формируется путем инвертирования импульсов первого и третьего тактов с последующим подключением этих сигналов к логическому элементу И. Длительность второго такта равна времени, измеряемому от заднего фронта первого такта до переднего фронта третьего такта, т, е, время, необходимое для выполнения операции логического сложения не влияет на быстродействие работы сумматора.

По третьему временному такту ( t.,. ) выполняется формирование результата суммирования кодов. В сумматоре отсутствует элемент временной задержки ла входах триггеров, поэтому формирование потенциала переноса начинается после переключения в нулевое состояние триггера 7 в любом разряде, Е этом случае потенциал переноса формируется с помощью элег-лентрв ИЛИ 5, И 1, согласно соотношенш . получаемому с выхода элеманта

, Если в старшем разряде прие.чного регистра хрш-штся код единицы, то перенос по цепи элемента ИЛИ 5 и И 1 проходит в следующий старший разряд. Однако если в триггере 7 старшего разряда хра нится единица, а в триггере 8 - нуль, то потенциал переноса распространяется в следуюБшй разряд только после БыпoлJieния операции логического сложения, т, е, при расчете времени максимальной задержки сигнала в цепях переноса необходимо брать отсчеты времени от заднего фронта импульса первого такта.

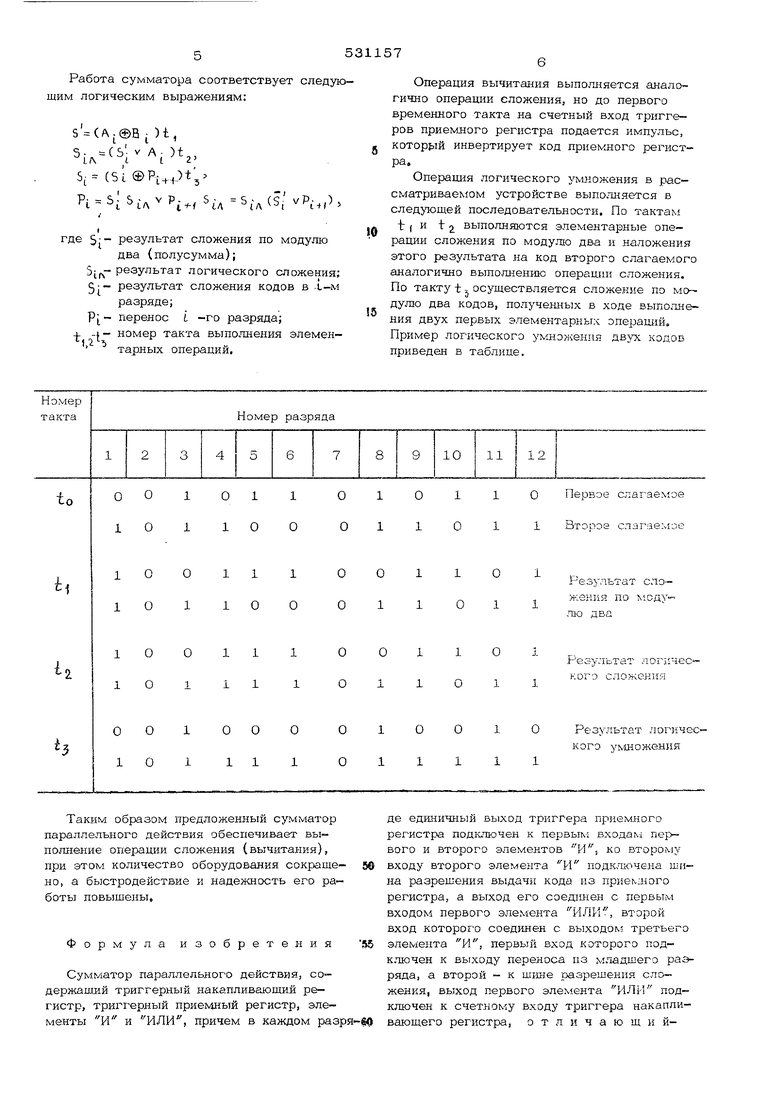

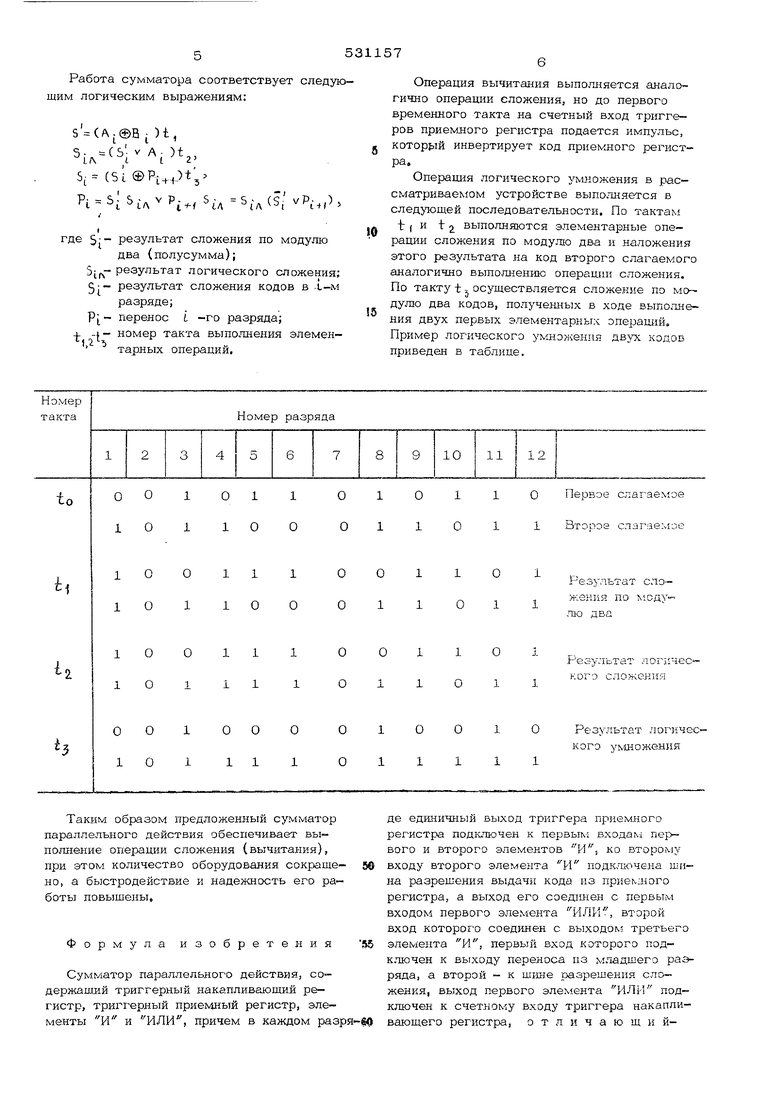

После распространения потенциала переноса на щину 10 подается импульс сложения, В тех разрядах, куда поступил потенциал переноса, элемент И 3 открыт и сигнал поступает на счетный вход триггера 7 и ycтшiaвливaeт его в единичное или нулевое состош1ие. Если импульс сложения установит триггер 7 в нулевое состояние, то из этого разряда дополнительно вырабатывается перенос в старший разряд, чта повышает надежность работы устройства. Работа сумматора соответствует следу щим логическим выражениям: 5(Л.®В )t, csi Ti .,(s; /р,,) где 5;- результат сложения по модулю два (по л ус ум ма); irT результат логического сложения результат сложения кодов в .1-м разряде; Pj - перенос 1 -го разряда; t „-t номер такта выполнения элемен тарных операций Т Л ОТТОГЛЙ TTT/tli Операция вычитания выполняется аналогично операции сложения, но до первого временного такта на счетный вход триггеров приемного регистра подается импульс, котор1:,1й инвертирует код приемного регистра. Операция логического умножения в рассматриваемом устройстве выполн:яется в следующей последовательности. По тактам i выполняются элементарные операции сложения по модулю два и наложения этого результата на код второго слагаемого аналогично выполнению операции сложения. По такту tj ос тдествляется сложение по модулю два кодов, полученных в ходе выполнения двух первых элементарных операций. Пример логического умножения двух кодов приведен в таблице. TTv-4Tri-,i-4i-i -.TTr.-r,-т.,,,,,

| название | год | авторы | номер документа |

|---|---|---|---|

| Параллельный накапливающий сумматор | 1979 |

|

SU911517A1 |

| Накапливающий сумматор | 1982 |

|

SU1043638A1 |

| Арифметическое устройство параллельного действия | 1977 |

|

SU643870A1 |

| Накапливающий сумматор | 1985 |

|

SU1264165A1 |

| Двоичный накапливающий сумматор | 1983 |

|

SU1112363A1 |

| СУММАТОР ПАРАЛЛЕЛЬНОГО ДЕЙСТВИЯ | 1972 |

|

SU351214A1 |

| Накапливающий сумматор | 1987 |

|

SU1418701A1 |

| Двухтактный п-разрядный сумматор накапливающего типа | 1974 |

|

SU538365A1 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО ПАРАЛЛЕЛЬНОГО | 1973 |

|

SU362295A1 |

| Накапливающий сумматор | 1987 |

|

SU1418705A1 |

1 О О 1 1 001 011 10110 001 011 1 о о 1 1 111 1 о о 1 о 001 000 011 101111

Таким образом предочоженный сумматор параллельного действия обеспечивает выполнение операции сложения (вычитания), при этом количество оборудования сокраще- но, а быстродействие и надежность его работы повышены.

Формула изобретения 55

Сумматор параллельного действия, содержащий триггерный накапливающий регистр, триггерный приемный регистр, элементы И и ИЛИ, причем в каждом разря-§0

Результат сложения по модулю два

Результат логического укшожения

де единичный выход триггера приех-шого регистра под1слючен к первым входа NZ перко второму

вого и второго элементов

входу второго элемента И подключена шина разрешения выдачи кода из приемного регистра, а выход его соедгшен с первым входом первого элемента ИЛИ, второй вход которого соединен с выходом третьего элемента И, первый вход которого подключен к выходу переноса пз младшего рааряда, а второй - к Ш1ше разрешения сложения, выход первого элемента ИЛИ подключен к счетному входу триггера накапливающего регистра, отличающий101011 101 о 1 1 о 1 о 111

Авторы

Даты

1976-10-05—Публикация

1974-09-13—Подача