Изобретение относится к области импульсной техники и может быть использовано в различных устройствах вычислительной техники, автоматики и телемеханики.

Известные схемы триггеров не имеют цепи регенерации, следовательно, при считывании информация не восстанавливается. Кроме этого, при объединении триггеров в регистры нельзя осуществить параллельный опрос регистра в силу того, что выходной сигнал предыдущего триггера может воздействовать на счетный вход последующего.

Предложенный триггер отличается от известных тем, что он содержит элемент запрета с двумя выходами, выполненный на основе схем совпадения, причем выходы триггера через элементы согласования соединены соответственно с шиной записи «1» и шиной установки в «0».

Сущность изобретения заключается в том, что предлагаемый триггер имеет два единичных выхода и цель регенерации, в результате чего один из выходов можно использовать при работе триггера в режиме деления частоты, другой - в режиме считывания информации с последующей регенерацией, следовательно, функциональные возможности триггера расширяются.

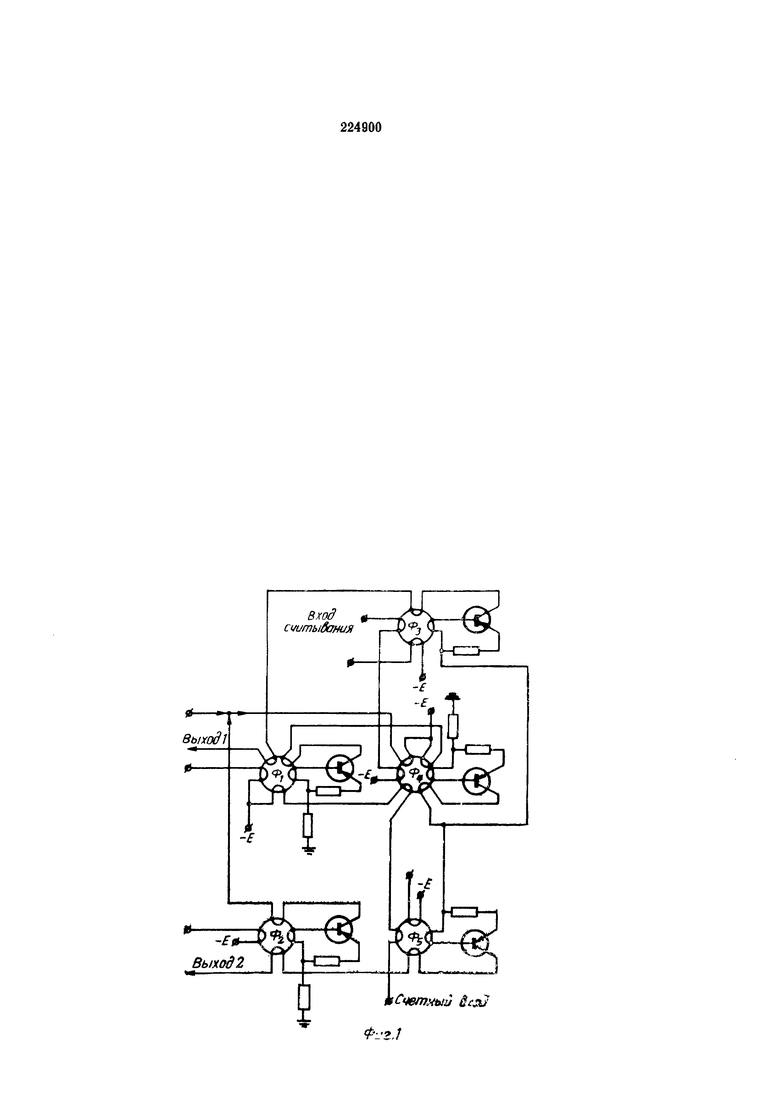

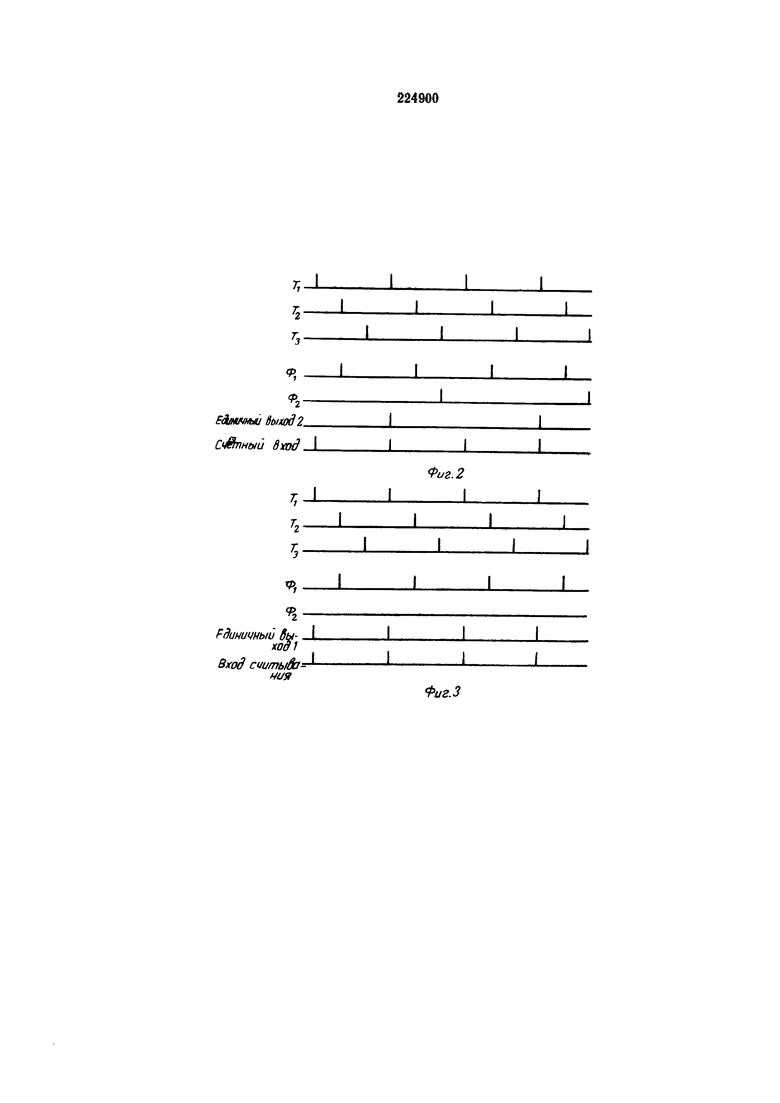

На фиг. 1 изображена схема триггера; на фиг. 2 - осциллограмма работы триггера в режиме деления частоты и на фиг. 3 - то же, в режиме считывания хранимой информации.

Предлагаемый статический триггер содержит пять ферриттранзисторных модулей. Модули Ф1 и Ф2 являются согласующими.; на модулях Ф3, Ф4 и Ф5 выполнен элемент запрета с двумя выходами, в состав которого входят две логические схемы «И», имеющие общий феррит-транзисторный модуль (ФТМ) Ф4 с обмоткой запрета.

Рассмотрим работу предлагаемого триггера в режиме деления частоты и в режиме считывания информации. Синхронизация работы триггера осуществляется тремя последовательностями тактов Т1, Т2 и Т3, причем такт Т2 постоянно заведен на считывание с Ф1 и на запись «1» в Ф4 и Ф5. Такт Т3 постоянно опрашивает Ф2. Таким образом, внутреннее состояние триггера определяется внутренним состоянием Ф4.

На счетный вход и на вход считывания (фиг. 1) сигналы поступают, согласно программе, синхронно с тактом Т1 (фиг. 2 и фиг. 3).

Допустим, что триггер находится в нулевом состоянии (в Ф4 записан «0»). Подадим на счетный вход триггера серию импульсов такта Т1. Первый импульс из этой серии опрашивает схему «И» (модули Ф4 и Ф5) и записывает «1» в согласующий модуль Ф1. На выходе 2 триггера сигнал не появится, триод Ф5 останется запертым (он открывается только по базе), так как цепь для его коллекторного тока разомкнута (Ф4 находится в нулевом состояния). Тактом Т2, следующим за Т1, единица из Ф1 перезапишется в Ф4, в результате триггер перейдет в состояние «1». С приходом очередного импульса из серии такта Т1 на выходе 2 триггера появится сигнал, который запишет «1» в Ф2. Далее следует такт Т2, и «1» из Ф1 перезапишется в Ф4.

Так как в Ф2 была записана «1», то тактом Т3, который следует за Т2 и опрашивает Ф2, сигнал с выхода модуля Ф2 переведет Ф4 в нулевое состояние, т.е. внутреннее состояние триггера станет нулевым. При последующем воздействии серии импульсов такта T1 на счетный вход триггера последний работает аналогично, и на выходе 2 появляется каждый второй импульс такта Т1 (фиг. 2).

Рассмотрим работу триггера в режиме считывания информации. Пусть триггер находится в состоянии «1». Подадим на вход считывания (фиг. 1) серию импульсов такта T1. На выходе 1 триггера появится сигнал, который запишет «1» в Ф1, и очередным тактом Т2 «1» перезапишется в Ф4, т.е. внутреннее состояние триггера не изменится. С приходом каждого импульса на вход считывания на выходе 1 триггера будет появляться сигнал (фиг. 3).

Предлагаемый триггер производит деление частоты на два, способен восстанавливать хранимую информацию после считывания; при этом сигналы в режиме деления появляются на одном из выходов (выход 2), в режиме считывания - на другом (выход 1).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления | 1990 |

|

SU1746378A1 |

| Устройство для деления | 1990 |

|

SU1728860A1 |

| ПАРАЛЛЕЛЬНЫЙ СУММАТОР НА ФЕРРИТ-ТРАНЗИСТОРНЫХ МОДУЛЯХ | 1970 |

|

SU277409A1 |

| СПОСОБ ИЗМЕРЕНИЯ ЧАСТОТЫ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2005 |

|

RU2300112C2 |

| Устройство для связи микропроцессора с внешними устройствами | 1986 |

|

SU1372330A1 |

| Устройство для сопряжения с микропроцессором | 1983 |

|

SU1109730A1 |

| Устройство для измерения угла опережения впрыска топлива в двигатель внутреннего сгорания | 1985 |

|

SU1355748A2 |

| Устройство для числового программного управления | 1985 |

|

SU1352459A1 |

| Система распределения электрической нагрузки электростанции | 1982 |

|

SU1065958A1 |

| Способ оценки микроциркуляторных нарушений в коже у пациентов с нарушениями углеводного обмена и устройство для его осуществления | 2019 |

|

RU2737714C1 |

Статический триггер на основе феррит-транзисторного модуля, отличающийся тем, что, с целью расширения функциональных возможностей, он содержит элемент запрета с двумя выходами, выполненный на основе схем совпадения, причем выходы триггера через элементы согласования соединены соответственно с шиной записи «1» и шиной установки в «0».

Авторы

Даты

1968-12-03—Публикация

1967-06-12—Подача