(5) ПАРАЛЛЕЛЬНЫЙ НАКАПЛИВАЮЩИЙ СУММАТОР

| название | год | авторы | номер документа |

|---|---|---|---|

| Двоичный накапливающий сумматор | 1983 |

|

SU1112363A1 |

| Накапливающий сумматор | 1982 |

|

SU1043638A1 |

| Сумматор параллельного действия | 1974 |

|

SU531157A1 |

| Накапливающий сумматор | 1985 |

|

SU1264165A1 |

| Арифметическое устройство | 1979 |

|

SU842794A1 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО ПАРАЛЛЕЛЬНОГО | 1973 |

|

SU362295A1 |

| Двухтактный п-разрядный сумматор накапливающего типа | 1974 |

|

SU538365A1 |

| СУММАТОР ПАРАЛЛЕЛЬНОГО ДЕЙСТВИЯ | 1972 |

|

SU351214A1 |

| Накапливающий сумматор | 1987 |

|

SU1418701A1 |

| Арифметическое устройство параллельного действия | 1977 |

|

SU643870A1 |

I

Изобретение относится к цифровой йычислительной технике и предназначается для использования в составе цифровых вычислительных машин и устройств.

Известны сумматоры параллельного действия накапливающего типа, содержащее триггерные регистры, выполненные на основе однотактных триггеров со счетными входами, схемы сквозного переноса, схемы группового ускорения переноса, логические элементы И, ИЛИ и шины управления работой сумматора 3.

Наиболее близким к предлагаемому устройству является сумматор параллельного действия, содержащий триггерный накапливающий регистр, триггерный приемный регистр, элементы -И, ИЛИ, причем в каждом разряде единичный выход триггера приемного региctpa подключен к первым входам первого и второго элементов И, ко второму входу второго элемента И

подключена шина разрешения выдачи кода из приемного регистра, а выход его соединен с первым входом первого элемента ИЛИ, второй вход которого соединен с выходом третьего элемента И, первый вход которого подключен к ВЫХОДУ переноса из г ладшего разряда, а второй - к шине разрешения сложения, выход первого элемента ИЛИ подключен к счетному входу триггера накапливающего регистра, а единичный выход триггера накапливающего регистра подключен к первому входу четвертого элемента И, ко второму входу которого подключена шина разрешения приема кода в приемный регистр из накапливающего регистра, выход этого элемента И подключен к единичному входу триггера приемного регистра, нулевой выход триггера накапливающего регистра подключен к первому сходу второго элемента ИЛИ, второй вход которого связан с шиной переноса из младшего разряда, а выход соединен

391

со вторым входом первого элемента И, выход которого является выходом переноса из данного разряда 2.

Этот сумматор лишен недостатков широко применяемых сумматоров параллельного действия накапливающегр типа, вызванных необходимостью включения на вход счетного триггера элементов временной задержки сигналов, что снижает быстродействие работы Сумматоров, усложняет его. схему и увеличивает объем оборудования. В известном сумматоре исключены, элементы задержки и повышено быстродействие работы. Однако выполнение пересылки кода из накапливающего регистра в приемный регистр, необходимое для разрешения распространения сигнала переноса, снижает его быстродействие.

Цель изобретения - повьшение быстродействия.

Указанная .цель достигается тем, что параллельный накапливающий сумматор, содержащий в каждом разряде триггер, счетный триггер, четыре элемента И и два элемента ИЛИ,причем выход триггера соединен с первым входом первого элемента И, выход которого подключен к первому входу первого элемента , второй вход которого соединен с выходом второго элемента И, а выход подключен ко входу счетного триггера, нулевой выход которого соединен с первым входом второго элемента ИЛИ, 9 единичный выход - с первым входом третьего элемента И, выход которого соединен со входом триггера, второй вход второго элемента ИЛИ соединен с первым входом второго элемента И и входом переноса в данный разряд сумматора, выход второго элемента ИЛИ соединен с первым входом четвертого элемента И, выход которого является выходом переноса из данного разряда, вторые входы первого, второго и третьего элементов И соединены с соответствующими управляющими шинами сумматора, он содержит узлы группового переноса и элементы ИЛИ, входы каждого из которых соединены с выходЬм соответствующего узла группового переноса и выходом переноса старшего разряда соответствующей группы разрядов сумматора, а выход соединен с первым входом последующего узла группового переноса, остальные входы каж174

дого узла группового переноса соединены с выходами триггеров разрядов соответствующей группы, выход каж-. дого узла группового переноса соедит

нен с третьим входом второго элемента ИЛИ старшего разряда соответствующей группы,и, кроме того, в каждый разряд сумматора введен третий элемент ИЛИ, входы которого соединены со входом и выходом триггера

соответствующего разряда, а выход подключен ко второму входу четвертого элемента И.

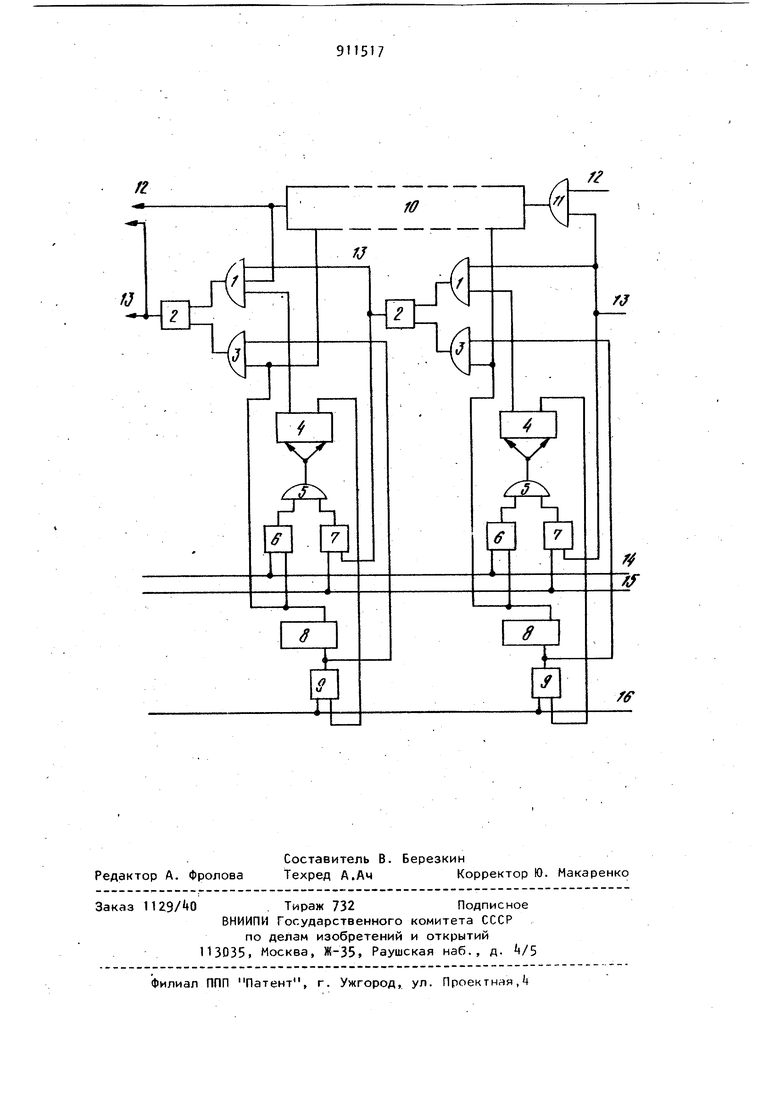

На чертеже представлена функциональная схема двух разрядов сумматора.

Каждый разряд сумматора содержит элементы ИЛИ 1, И 2, ИЛИ 3, счетный

0 триггер 4, элементы ИЛИ 5 И 6, И 7. триггер 8, элемент И 9Каждая группа разрядов сумматора содержит узел 10 группового переноса и элемент ИЛИ 1). Выход узла

5 10 является выходом 12 группового переноса, который вместе с выходом 13 переноса старшего разряда группы разрядов сумматора поступает в последующую группу разрядов сумматора.

Управляющие шины 1А и 16 управляют работой сумматора.

Нулевой выход триггера t подключен к входу элемента ИЛИ 1. Единичный выход триггера k соединен с первым входом .элемента И 9. Второй вход элемента И 9 подключен к шине 16,а выход элемента И 9 соединен с единичным входом триггера 8 и первым входом элемента ИЛИ 3. Единичный выход триггера 8 соединен с выходами И 6, ИЛИ 3 и с входом узла 10 группового переноса. Выход элемента ИЛИ 3 подключен к первому входу элемента И 2. Второй вход элемента И 2 соединен с выходом элемента ИЛИ 1, ко второ{му входу которого подключен выход 13 переноса предыдущего разряда сумматора, третий вход элемента ИЛИ 1 старшего разр/4да группы разрядов сумматора соединен с выходом узла

Авторы

Даты

1982-03-07—Публикация

1979-09-27—Подача