Изобретение касается вопросов повышений помехоустойчивости и точности выделения сигналов синхронизации и может быть использовано в радиолиниях передачи дискретной информации, реализующих прием в целом указанных сигналов с помощью согласованного фильтра.

Известны устройства синхронизации, содержащие анализирующий блок, генератор тактовых импульсов, распределительный узел, схемы совпадения и запрета. В известных устройствах меняющаяся от сеанса к сеансу связи мощность сигнала сильно влияет на помехоустойчивость приема сигнала синхронизации.

С целью повышения помехоустойчивости выделения сигнала синхронизации, в предлагаемом устройстве автоматически устанавливается величина порогового напряжения в определенный момент времени по величине сигнала в предыдущий момент времени, чем обеспечивается достоверное выделение синхроимпульса на фоне помех, не превышающих уровень полезного сигнала.

Для устранения появляющегося при этом влияния ложных синхроимпульсов на прием истинного синхроимпульса введена задержка выходного сигнала с блока анализа.

на помехоустойчивость боковых выбросов корреляционной функции.

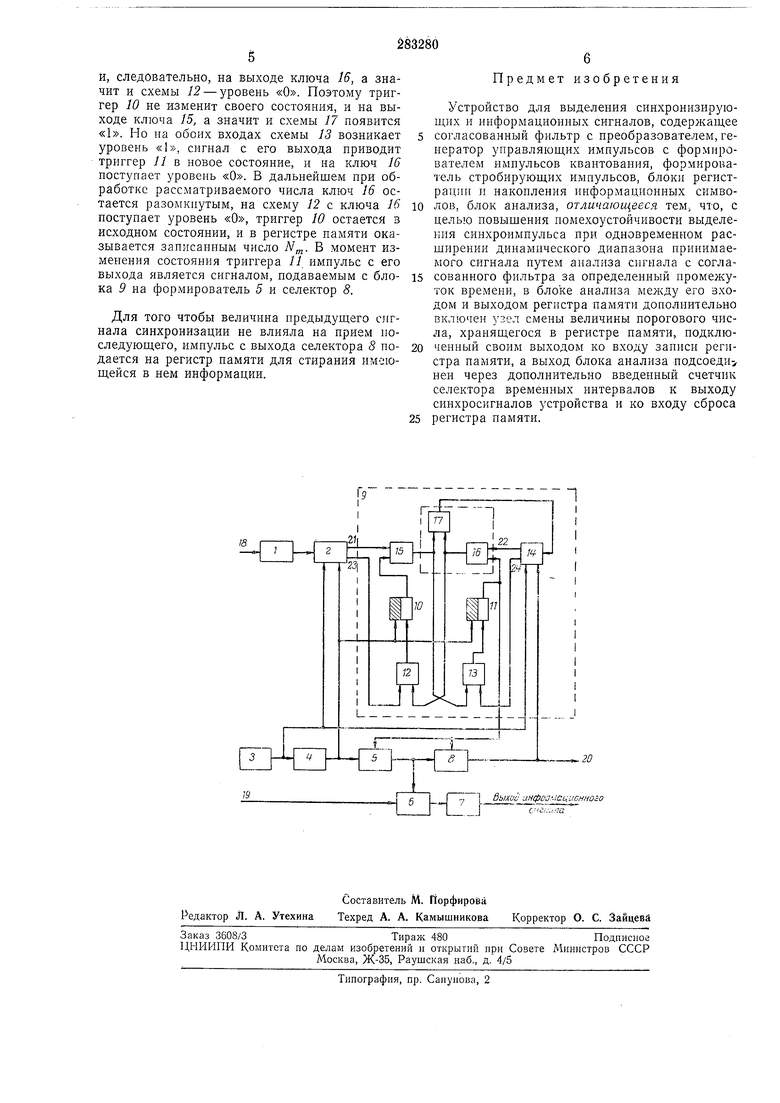

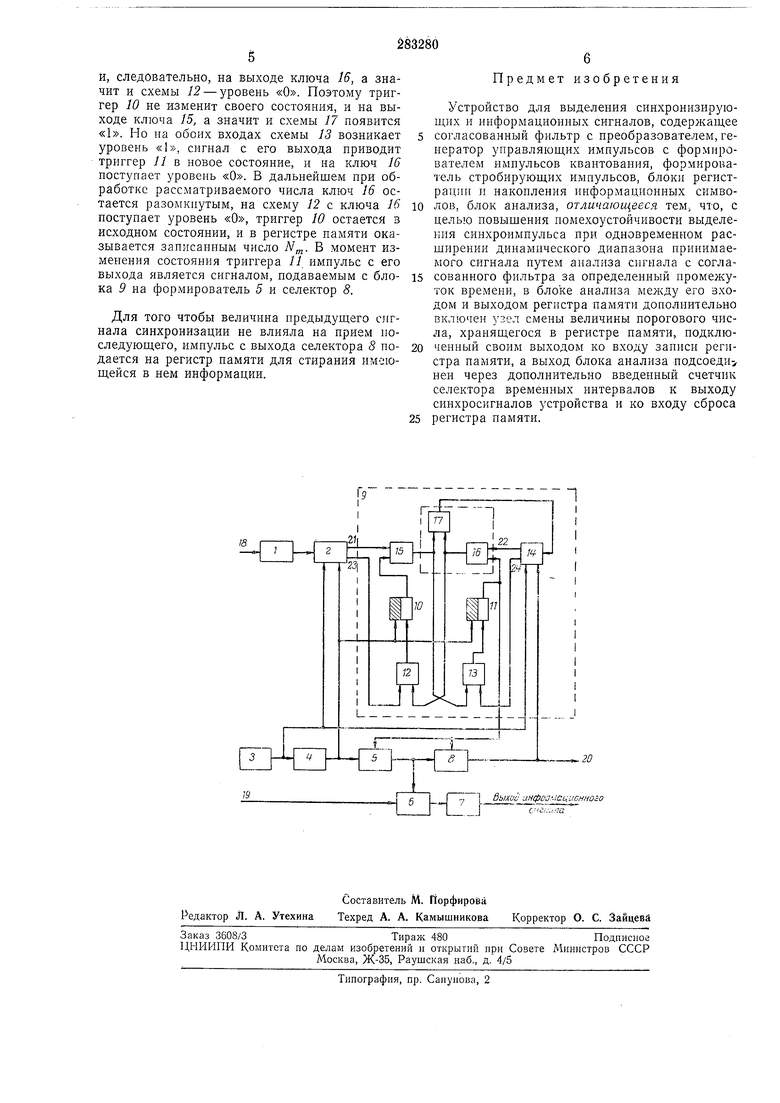

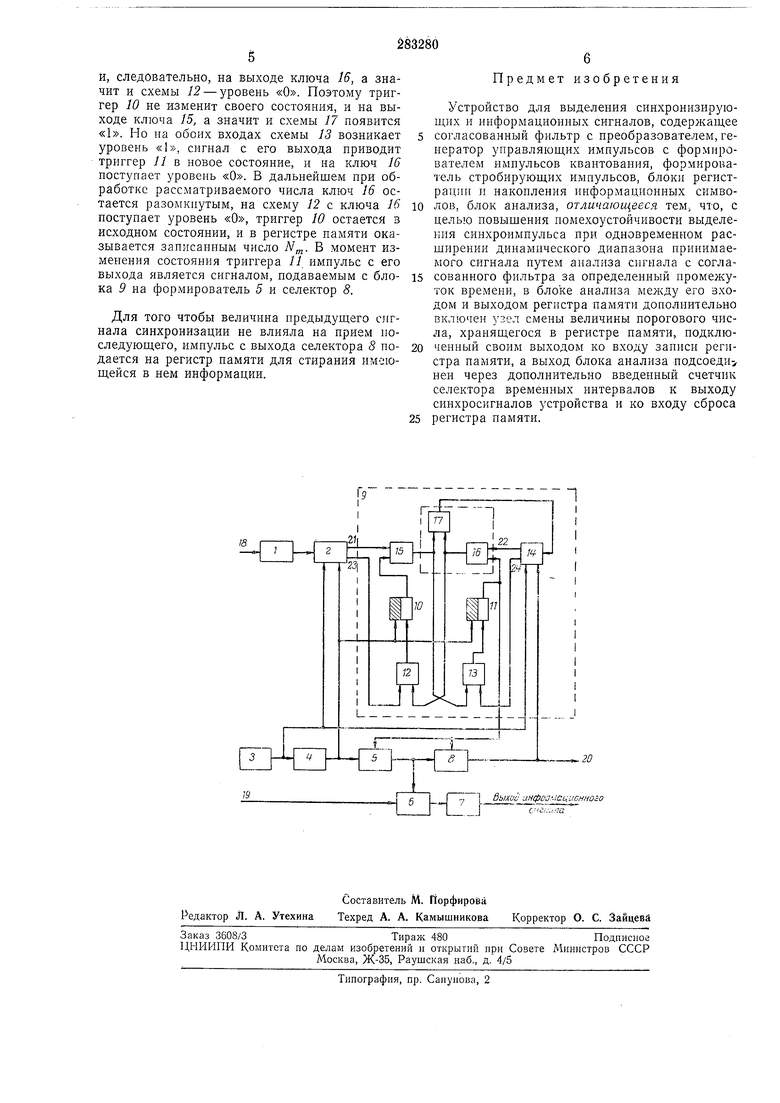

Па чертеже показано предложенное устройство.

Устройство содержит согласованный фильтр 1 с преобразователем 2 аналогового сигнала в цифровую форму, генератор 3 управляющих импульсов с формирователем 4 импульсов квантования, формирователь 5 стробирующих импульсов, блок 6 регистрации информационных импульсов, блок 7 накопления информационных импульсов, селектор 8 временных интервалов, блок анализа 9 (блок помехоустойчивости выделения синхроимиульса). В блок анализа 9 входят управляющие триггеры 10 и 11, схемы совпадения 12 и 13, регистр памяти 14, ключи 15 и 16 и схема объединения 17.

Устройство имеет ввод 18 для сигнала синхронизации и ввод 19 для информационного сигнала. Ввод 18 подключен к фильтру /, на выходе которого образуется корреляционная функция сигнала синхронизации.

Выход блока подключен к преобразователю 2, в котором величина входного сигнала в текущий момент квантования иреобразуется в двоичное число Nm. Моменты квантования задаются последовательностью импульсов, подарователя 4 импульсов квантования с периодом повторения TK . Величина Тк определяется условием- K - Vi где Ти -длительность элементарного символа информационного сигнала; Т -допустимая ошибка синхронизации в долях от THКроме того, с целью упрощения аппаратуры М --целое число. Для обеспечения ошибки квантования по амплитуде порядка 3% и динамического диапазона по величине принимаемого сигнала порядка 30 раз двоичное число на выходе преобразователя 2 состоит из 10 элементарных двоичных посылок, каждая длительностью Тп - Необходимая для формирования указаииых двоичных чисел опорная импульсная последовательность с периодом т„ подается на преобразователь 2 с выхода генератора 5 управляющих имнульсов. Сигнал с генератора 3 поступает также на формирователь 4, представляющий собой счетчик на 10. В блоке анализа 9 двоичное число N с выхода преобразователя 2 сравнивается с числом Л/„ находящимся в ретистре 14. Если ,то число хранящееся в памяти, не меняется, а на выходе блока 9 сигнал отсутствует. Если N Л/„ , то в память регистра 14 вместо Л/„ записывается число jV и на выходе блока 9 появляется импульс, который проходит на формирователь 5 стробирующих импульсов и селекторов 8 временных интервалов для установки их в нулевое состояние. Формирователь 5 и селектор 8 последовательно подключены к выходу формирователя и представляют собой двоичные счетчики на М и N раз соответственно, где Л - число символов в информационном сигнале. Пусть в некоторый момент to двоичное число Лт„ на выходе преобразователя 2 превысило число, хранящееся в памяти блока анализа. Тогда на выходе блока 9 появляется импульс, который сбрасывает на нуль формирователь 5 и селектор 8. Пусть носле момента о в течение времени Т величина Nma. Тогда в этот итнервал времени импульс на выходе блока 9 не появляется, а потому в момент t + T на выходе селектора 8 возникает сигнал, который подается на оконечную аппаратуру 20 в качестве синхронизирующей метки и стирает число N, хранящееся в памяти блока анализа. Одновременно на блок 6 регистрации информационных символов поступают сигнал с ввода 19 устройства и стробирующие импульсы с формирователя 5. При приеме символа на выходе блока 6 появляется импульс, а при приеме символа «О импульс отсутствует. Сигналы с блока 6 поступают на блок 7, на который одновременно подаются стробирующие кость блока иакоиления не менее числа Л, а сигналы с его выхода поступают на оконечную аппаратуру для дальнейшей обработки. Память блока анализа представляет собой регистр 14 на 10 разрядов. Сравнение выполняется последовательно, начиная с высшего разряда. Преобразователь 2 (и регистр 14) имеет выход 21 (22) прямого 23 (24) обратного кода. Для продвижения информации в регистре 14 на него подаются управляющие импульсы с геиератора 5. Выход 21 (22) подан на вход ключа 15 (16), а выход 23 (24) - на схему совпадения 12 (13). Ключи 15, 16 и схемы совпадения 12, 13 представляют собой схемы совпадения на два входа (схема «П). Выход узла 12 (13) подключен ко входу триггера управления 10 (11) так, что появление на нем «1 устанавливает триггер в состояние, при котором на его выходе, поданном на ключ 15 (16), появляется «О. Выходы ключей 15 и М через схему объединения /7 (схему «ИЛИ) подсоединены ко входу регистра 14. Перед началом сравнения импульс с формиропателя 5 устанавливает триггеры 10 и 11 ъ исходное состояние, когда на их выходах появляется «1. Блок анализа работает в трех режимах. 1. Сравниваемые символы (а также все предыдущие, соответствующие более высоким разрядам) чисел Л/„ и М„ одинаковы. При этом на схему совпадения 12 (13) поступает «О с преобразователя (регистра памяти) или с выхода ключа 16 (15). поэтому триггеры 10 (11) остаются в исходном состоянии и на вход регистра 14 записывается символ, снимаемый с его выхода. Блок 9 находится в первом режиме перед началом сравнения чисел и может перейти из него во второй или третий режим. 2. Число . Тогда имеется один такой /-Й разряд, на котором в числе Л„ находится символ «1, а в числе Л -символ «О, а все более высокие 1, ..., /-1 разряды этих чисел одинаковы (в частности, может быть, что ). Тогда при сравнении /-х разрядов на выходе 21 (22) появится «О («1), следовательно, на выходе ключа 15, а значит и схемы 13 - «О. Поэтому триггер 11 не изменяют своего состояния, и на выходе ключа 16, а значит и схемы 17 появляется «1. По на обоих входах схемы 12 возникнет «1, а сигнал с его выхода переводит триггер 10 в новое состояние, и на ключ 15 поступает уровень «О, В дальнейшем при обработке рассматриваемого числа первый ключ остается разомкнут 1М, на схему 13 с ключа 15 поступает уровень «О, и триггер 11 остается в исходном состоянии, а в регистре памяти оказывается переписанным число М„. 3. Число . Тогда имеется один такой /-Й разряд, на котором в числе Л находится символ «1, а в числе N - символ «О, а все более высокие 1, ..., /-1 разряды этих чисел одинаковы. Тогда при сравнении /-х рази, следовательно, на выходе ключа 16, а значит и схемы 12 - уровень «О. Поэтому триггер 10 не изменит своего состояния, и на выходе ключа 15, а значит и схемы 17 появится «1. Но на обоих входах схемы 13 возникает уровень «, сигнал с его выхода приводит триггер 11 в новое состояиие, и на ключ 16 поступает уровень «О. В дальнейшем нри обработке рассматриваемого числа ключ 16 остается разомкнутым, на схему 12 с ключа 16 поступает уровень «О, триггер 10 остается в исходном состоянии, и в регистре памяти оказывается записанным число N. В момент изменения состояния триггера /) импульс с его выхода является сигналом, подаваемым с блока 9 на формирователь 5 и селектор 8. Для того чтобы величина предыдущего сигнала синхронизации не влияла на прием последующего, импульс с выхода селектора 8 подается на регистр памяти для стирания имеющейся в нем информации. 5 10 15 20 25 Предмет изобретения Устройство для выделения синхронизируюHj,Hx и информационных сигналов, содержащее согласованный фильтр с преобразователем, геператор управляющих импульсов с формирователем имиульсов квантования, формирователь стробнрующих импульсов, блоки регистрации и накоиления информационных символов, блок анализа, отличающееся тем, что, с целью повыщения помехоустойчивости выделения синхроимпульса при одновременном расширении динамического диапазона принимаемого сигнала путем анализа сигнала с согласованного фильтра за определенный промежуток времени, в блоке анализа между его входом и выходом регистра памяти дополнительно включен узел смены величины порогового числа, хранящегося в регистре иамяти, подключенный своим выходом ко входу записи регистра памяти, а выход блока анализа иодсоеди нен через дополнительно введенный счетчик селектора временных интервалов к выходу синхросигналов устройства и ко входу сброса регистра памяти.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное устройство приема сложных сигналов | 1989 |

|

SU1786664A1 |

| Дельта-кодер | 1988 |

|

SU1646056A1 |

| Дельта-кодер | 1986 |

|

SU1381715A1 |

| СИСТЕМА ПЕРЕДАЧИ ИНФОРМАЦИИ | 1991 |

|

RU2043659C1 |

| Устройство для выделения маркера кадровой синхронизации | 1978 |

|

SU752313A1 |

| Устройство для передачи и приема многочастотных многопозиционных сигналов | 1988 |

|

SU1578835A1 |

| Устройство для измерения мощности цилиндров двигателя внутреннего сгорания | 1990 |

|

SU1789898A1 |

| Преобразователь сигналов с адаптивной дельта-модуляцией со слоговым компандированием в сигналы с нелинейной импульсно-кодовой модуляцией | 1990 |

|

SU1762411A1 |

| Дельта-кодер | 1986 |

|

SU1381716A1 |

| Система ввода телевизионных изображений в ЭВМ | 1989 |

|

SU1665391A1 |

( 1 Вьиоо инфм-,с:ц:.1снн0 0

.

Даты

1970-01-01—Публикация