Изобретение может быть использовано для

построения различных устройств автоматики,

телемеханики и вычислительной техники на

основе универсальных однородных структур

(вычислительных сред).

Известны элементы, которые, кроме других применений, могут быть использованы в качестве ячейки однородной структуры. Многофункциональный элемент при использовании в качестве ячейки однородной структуры обладает недостатками: в элементе коммутируются только выходы, логические входы не коммутируются. Это ограничивает его функциональные возможности, например, не позволяет использовать ячейку для однородных структур повышенного быстродействия со сквозными токопроводящими шинами, по которым сигналы распространяются практически без задержки (шинные структуры). Для связи с шинами ячейки должны иметь коммутируемые входы и выходы, т. е. принимать сигналы с шины и выдавать сигналы на шину. Кроме того, при наличии внешних помех необходимо периодически производить перезапись информации в триггеры ячеек для исправления возникаюших сбоев.

состояние. Тем самым каждый раз разрушается реализуемая структурой функция, что является существенным недостатком логической схемы.

Цель изобретения - расширение функциональных возможностей и увеличение быстродействия однородной структуры.

В предлагаемом элементе эта цель достигается тем, что без звеличения общего количества компонентов схема управления перераспределяется входами и выходами элемента, т. е. одна часть входов и выходов делается коммутируемой, а другая часть входов и выходов - некоммутируемой. При соединении элемента с шинами используются только коммутируемые входы и выходы. При соединении элементов друг с другом некоммутируемые входы одного элемента соединяются с коммутируемыми входами другого, и

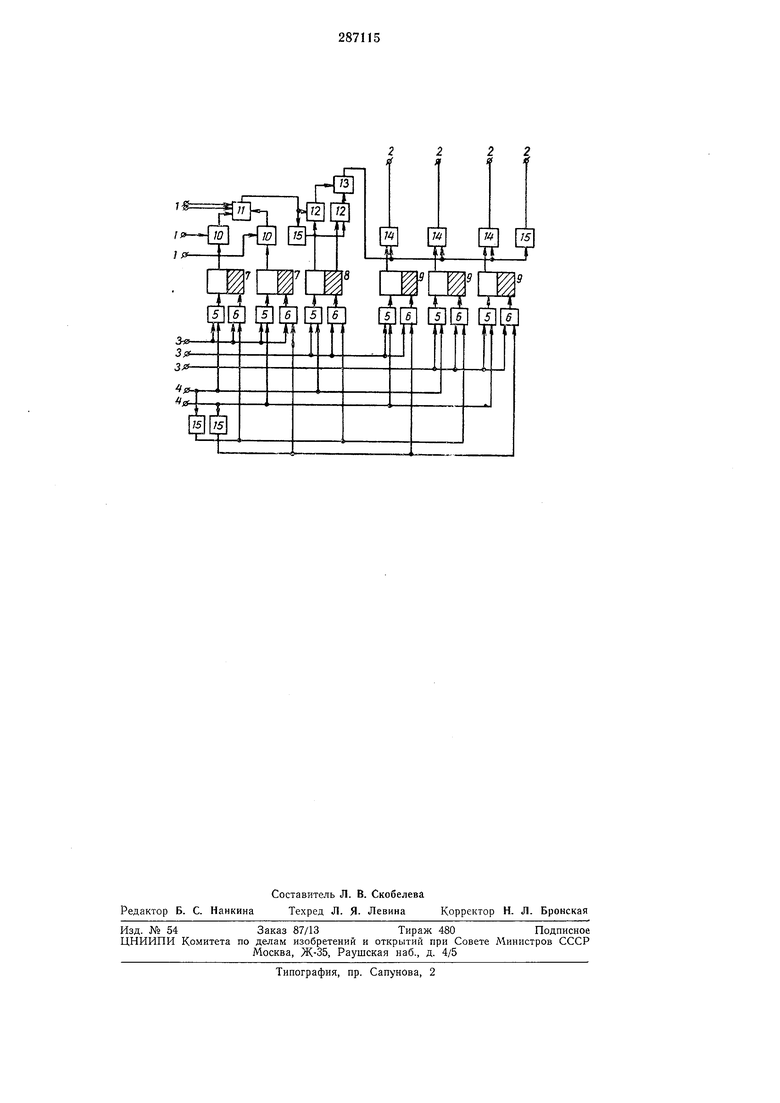

наоборот. Таким образом, между любыми двумя элементами в структуре (между соседними ячейками или между ячейками и шинами) образуется управляемый канал передачи информации, который может быть включен или выключен в зависимости от вида кода настройки. 3 стояние без предварительного сброса в нуль. Это дает возможность использовать логическую ячейку в быстродействующих шинных структурах и повысить помехоустойчивость структуры при помощи (Многократной пере-5 записи. Функциональная схема логической ячейки дана на чертеже. Логическая ячейка содержит входы 1, выходы 2, входы 3 горизонтальных и входы 4Ю вертикальных координат настройки, схемы щей 5 установки триггеров в единицу, схемы «И 6 установки триггеров в нуль, триггеры 7 управления входами, триггер 8 выбора функции, триггеры 9 управления выходами, вход-15 ные схемы 10 и 11, схемы 12 и 13 выбора функций «И и «ИЛИ, схемы 14 и 15. Схема «Сложение по модулю два реализована на схемах 12, 13 и 15. Логическая ячейка работает следующим об-20 разом. На входы / поступают сигналы с соседних ячеек или с шин, проходящих через всю структуру. Некоммутируемые сигналы подаются непосредственно на входы схемы «И 10, а25 коммутируемые - на входы схем «ИЛИ 11. На выходе схемы W реализуется конъюнкция переменных, поступающих с некоммутируемых входов непосредственно на входы схемы 10, и переменных, поступающих с коммутируемых30 входов через схемы «ИЛИ 11. Если какойлибо из триггеров 7 находится в единичном состоянии, то на соответствующий вход схемы 10 подается через схему 11 единичный сигнал. Это означает, что выход схемы 10 не зависит35 от соответствующего коммутируемого входа 1 ячейки, т. е. соответствующий канал передачи информации находится в выключенном состоянии со стороны входа данной логической ячейки. Включенным состояниям каналов40 передачи информации соответствуют нулевые состояния триггеров 7. В зависимости от состояния триггера 8 выбора функции на выходах 2 логической ячейки с помощью схемы «Сложение по модулю два реализуется либо45 конъюнкция входных переменных, либо ее отрицание. Если триггер 8 находится в нулевом состоянии, то сигнал на выходы 2 проходит с выхода схемы 10 через схемы 15, 12, 13 и 14 (т. е. инвертируется дважды). Если триггер 850 находится в единичном состоянии, то сигнал на выходы 2 проходит с выхода схемы 10 через схемы 12, 13 и 14 (т. е. инвертируется один раз). Если один из триггеров 9 управления выходами находится в нулевом состоянии,55 то на вход соответствующей схемы 14 подается нулевой сигнал, а на ее выходе сигнал равен единице независимо от сигнала на выходе схемы 13. Это значит, что соответствующий 4 канал передачи информации находится в выключенном состоянии со стороны коммутируемого выхода данной логической ячейки. Сигнал с выхода схемы 13, проходящий на выход 2 через схему 15, является некоммутируемым и должен быть подключен к коммутируемому входу / соседней логической ячейки. Выбор функции, ком.мутация входов 1 и выходов 2 производятся соответствующей настройкой триггеров 7-9. Настройка триггеров производится следующим образом. На первый вход 3 горизонтальных координат настройки подается единичный сигнал. В этот момент времени сигналы на входах 4 вертикальных координат настройки должны соответствовать требуемым состояниям первых двух триггеров 7. Например, при состоянии входов 4, «11 оба триггера устанавливаются в единичное состояние, а при состоянии входов «01 - первый триггер устанавливается в нуль, второй - в единицу. В следующий момент времени единичный сигнал подается на второй вход 3. В зависимости от кода, поданного на входы 4, вторая пара триггеров устанавливается в заданное состояние, и т. д. Очевидно, такую перенастройку можно производить многократно, не изменяя (если это требуется) состояния логической ячейки, Предмет изобретения Элемент однородной структуры, содержащий схемы «И, «ИЛИ, «И-НЕ, «НЕ, триггеры, коммутируемые и некоммутируемые входы, входы горизонтальных и вертикальных настроечных щин, отличающийся тем, что, с целью расширения функциональных возможностей и увеличения быстродействия однородной структуры, в нем схемы «И установки триггеров в единицу соединены по входам с горизонтальными и вертикальными настроечными щинами, схемы «И установки триггеров в нуль соединены по входам с горизонтальными и через схемы «НЕ с вертикальными настроечными щинами, выходы первых двух триггеров соединены со входами схем «ИЛИ, соединенных также с коммутируемыми входами элемента, выходы этих схем «ИЛИ соединены вместе с некоммутируемыми входами элемента через схему «И со входом схемы «Сложение по модулю два, с которой соединены также выходы третьего триггера, выходы оставшихся триггеров соединены с выходными схемами «И-НЕ, соединенными по входам также с выходом схемы «Сложение по модулю два и через элемент «НЕ с одним из выходов элемента структуры.

3

| название | год | авторы | номер документа |

|---|---|---|---|

| БЛОК НАСТРОЙКИ ЯЧЕЙКИ ВЫЧИСЛИТЕЛЬНОЙ СРЕДЫ | 1973 |

|

SU407311A1 |

| ЭЛЕМЕНТ ВЫЧИСЛИТЕЛЬНОЙ СРЕДЫ С ПЕРЕМЕННОЙ СТРУКТУРОЙ НАСТРОЙКИ | 1969 |

|

SU255654A1 |

| ЦИФРОВОЕ ВЫЧИСЛИТЕЛЬНО-ЛОГИЧЕСКОЕ УСТРОЙСТВО | 1970 |

|

SU273523A1 |

| ЛОГИЧЕСКОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1973 |

|

SU368643A1 |

| МАТРИЧНЫЙ КОММУТАТОР С ПРОГРАММИРУЕМОЙ ЛОГИКОЙ | 2003 |

|

RU2251792C2 |

| ВЫЧИСЛИТЕЛЬНАЯ СРЕДА | 1970 |

|

SU259474A1 |

| Многофункциональный логическийМОдуль | 1979 |

|

SU838700A1 |

| ЦИФРОВОЕ ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО" | 1973 |

|

SU368606A1 |

| УСТРОЙСТВО ПРИОРИТЕТНОГО ПОДКЛЮЧЕНИЯ ПРОЦЕССОРОВ К ОБЩЕЙ МАГИСТРАЛИ | 1971 |

|

SU317064A1 |

| ПРОЦЕССОР ДЛЯ ЦИФРОВОЙ СИСТЕМЫ ОБРАБОТКИ ДАННЫХ | 1971 |

|

SU305477A1 |

Даты

1970-01-01—Публикация