Изобретение относится к области вычислительной техники.

Известны схемы приоритетного нодключения процессоров к обще магистрали с изменяемым приоритетом, выполненные на триггерах, логических схемах и транзисторах.

В известных устройствах для реализации изменяемого приоритета используются отдельные блоки приоритета с достаточно большим количеством оборудования. В таких устройствах с подключением процессов к нескольким модулям памяти через обп;ую магистраль, в случае обращения к модулю памяти, занятого обслуживанием предыдущего запроса, снижается скорость обслуживания.

Олисываемое устройство отличается от известных тем, что в нем входная шина опроса в каждом процессоре соединена со входом первой схемы «И, другие входы которой соединены с нулевыми выходами триггера приоритета и триггера запроса обращения, а выход которой соединен со входом первой схемы «ИЛИ, вырабатывающей выходной импульс опроса, другой вход первой схемы «ИЛИ соединен со входом второй (Схемы «И, входы которой соединены соответственно с шиной занятости памяти и с выходом триггера срочности, третий вход первой схемы «ИЛИ соединен с выходом третьей схемы «И, входы которой соединены с нулевым выходом

триггера запроса обращения, единичным выходом триггера приоритета и выходом формирователя импульсов, вход которого соединен с эмиттером транзистора, подключенного своим входом 1К выходу второй схемы «ИЛИ, вход которой через схему «И подключен к входной шине опроса и единичному выходу триггера приоритета, другой вход второй схемы «ИЛИ связан с шиной гашения запросов, подключенной к нулевому входу триггера занятия магистрали, единичный выход которого соединен со входа.ми схем «И, выходы которых соединены со входами транзисторов, эмиттеры которых соединены с общей магистралью обслуживания.

Это позволяет сократить оборудование и увеличить быстродействие устройства.

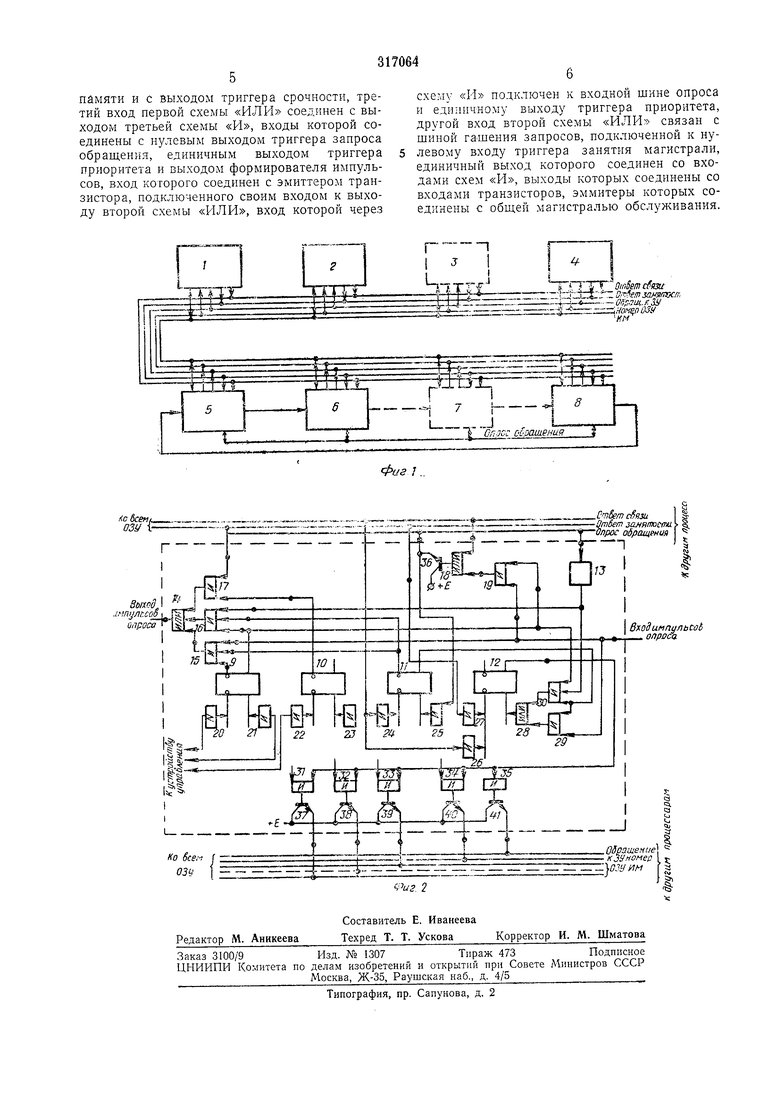

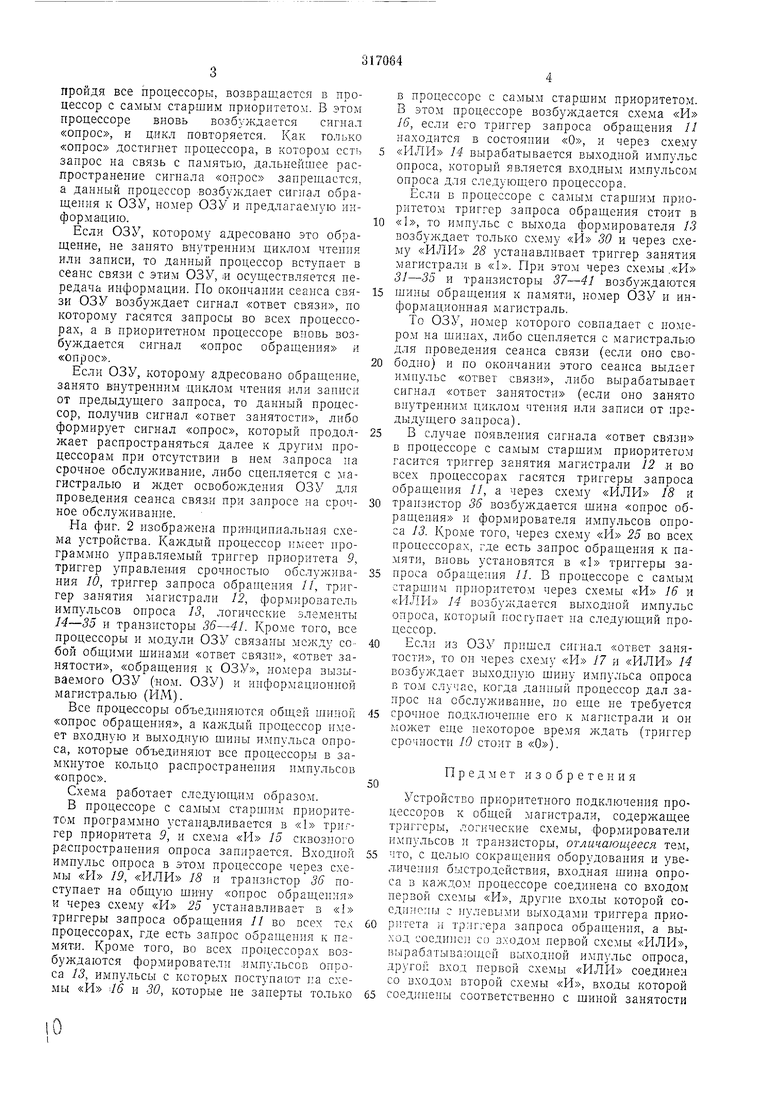

На фиг. I изображена блок-схема системы, состоящей из модулей оперативного запоминающего устройства (ОЗУ) /-4 и процессоров 5-5.

В процессоре с самым старшим приоритетом возбуждается щина «опрос обращения, от которой устанавливаются в состояние «1

триггеры запроса обращения в гех процессорах, где есть запрос на связь с памятью, а также возбуждается сигнал «опрос, который последовательно обегает все лроцессоры. Если ни в одном из процессоров нет запропройдя все процессоры, возвращается в процессор с самым старшим приоритетом. В этом процессоре вновь возбуждается сигнал «опрос, и цикл повторяется. Как только «опрос доститиет процессора, в котором сстт запрос на связь с памятью, дальнейшее распространение сигнала «опрос запрещается, а данный процессор возбуждает сиг}гал обращения к ОЗУ, иомер ОЗУ и предлагаемую информацию.

Если ОЗУ, которому адресовано это обращение, не занято внутренним циклом чтения или записи, то данный процессор вступает в сеаис связи с этим ОЗУ, 1И осзществляется нередача информации. По окончании сеаиса связи ОЗУ возбуждает сигнал «ответ связи, по которому гасятся запросы во всех процессорах, а в приоритетном процессоре вновь возбуждается сигнал «опрос обращения я «опрос.

Если ОЗУ, которому адресовано обращение, занято внутренним циклом чтения или записи от предыдущего запроса, то данный процессор, получив сигнал «ответ занятости, либо формирует сигнал «оирос, который продолжает распространяться далее к другим ироцессорам при отсутствии в нем запроса на срочное обслуживание, либо сцепляется с магистралью и ждет освобол ;депия ОЗУ для проведения сеанса связ-и при запросе на срочное обслуживание.

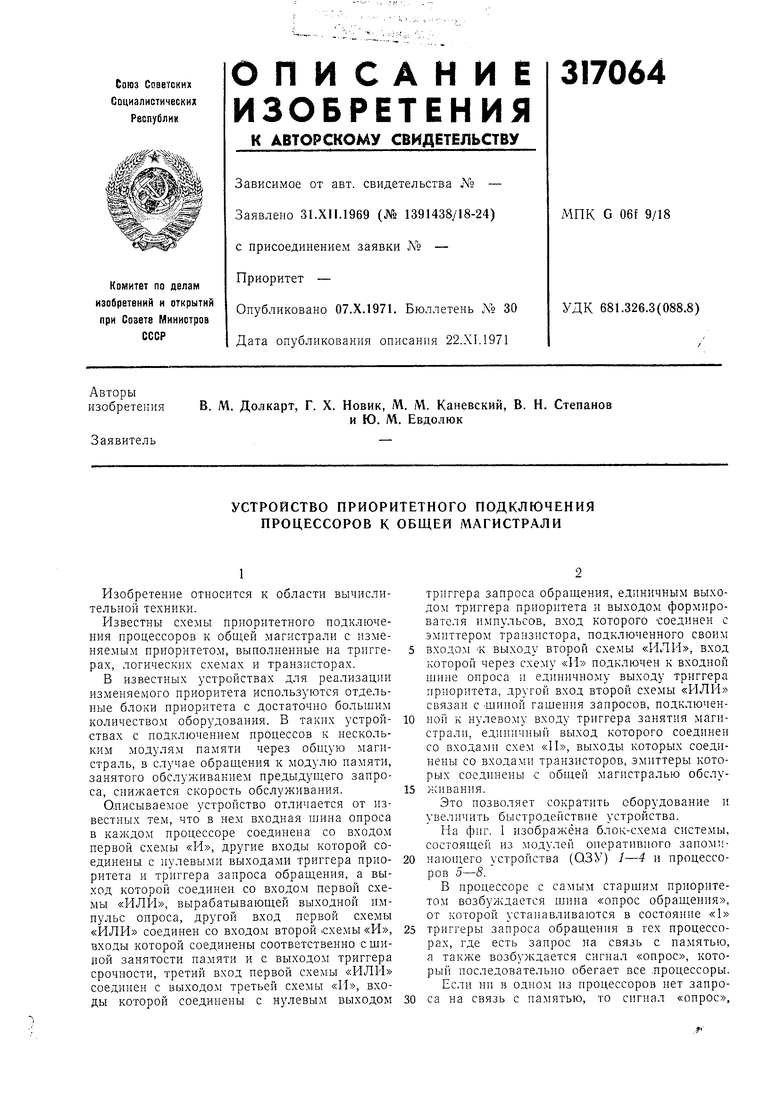

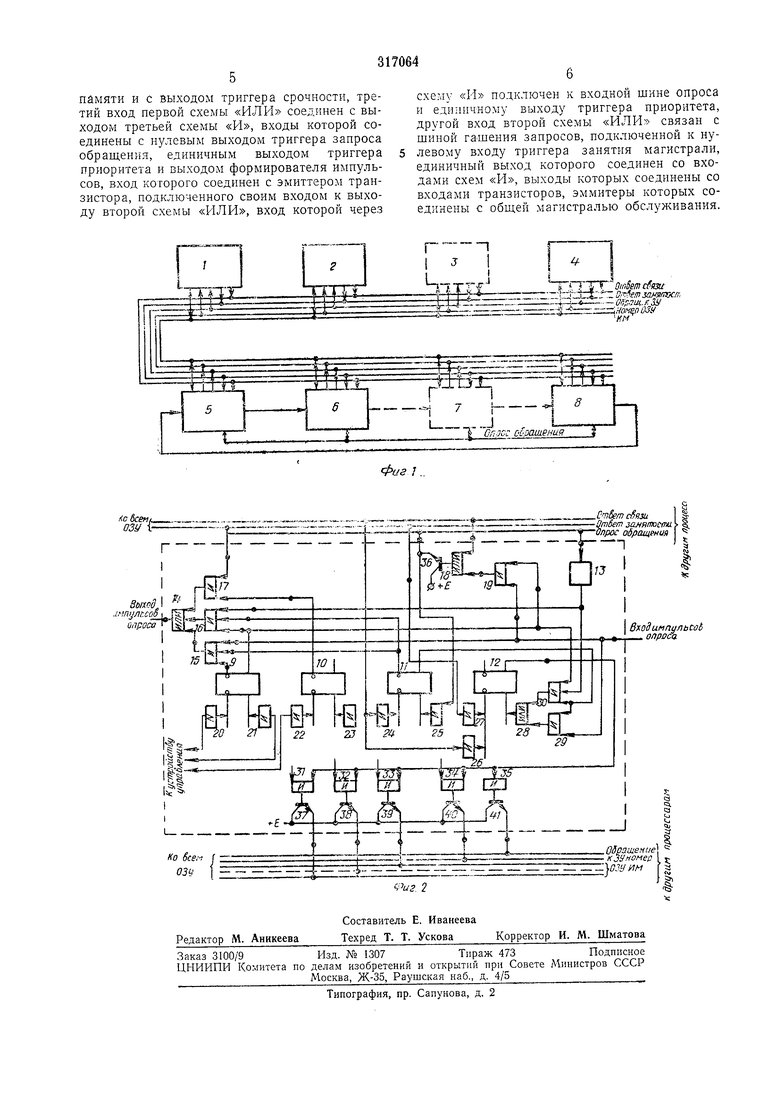

На фиг. 2 изобралсена прииципиальная схема устройства. Каждый процессор имеет программно управляемый триггер приоритета 9, триггер управления срочиостью обслуживания 10, триггер запроса обрап1ения //, триггер занятия магистрали 12, формирователь импульсов опроса J3, логические элементы 14-55 и транзисторы 36-41. Кроме того, все процессоры и модули ОЗУ связаны между собой общими щипами «ответ связи, «ответ занятости, «обращения к ОЗУ, номера вызываемого ОЗУ (НОМ. ОЗУ) и информационной магистралью (ИМ).

Все процессоры объединяются общей щиной «опрос обращения, а каждый процессор имеет входную и выходную щины импульса опроса, которые объединяют все процессоры в замкиутое кольцо распростраиепия импульсов «опрос.

Схема pai6oTaeT следующим образом.

В процессоре с самым старшим приоритетом программно устанавливается в «1 триггер приоритета 9, и схема «PI 15 сквозного распространения опроса запирается. Входпой импульс опроса в этом процессоре через схемы «И 19, «ИЛИ 18 и транзистор 36 поступает па общую щииу «опрос обращения и через схему «И 25 устанавливает в «1 триггеры запроса обращения 11 во всех тех процессорах, где есть запрос обращения к памяти. Кроме того, во scex процессорах возбуждаются формирователи импульсов опроса 13, импульсы с которых поступают па схемы «И 16 и 30, которые не заперты только

в процессоре с самым старшим приоритетом. В этом процессоре возбуждается схема «И 16, если его триггер запроса обращения 11 находится в состоянии «О, и через схему

«ИЛИ 14 вырабатывается выходной импульс опроса, который является входпым импульсом опроса для следующего процессора.

Если в процессоре с самым старшим приоритетом триггер запроса обращения стоит в

«I, то импульс с выхода формирователя 13 возбуждает только схему «И 30 и через схему «ИЛИ 28 устанавливает триггер занятия магистрали в «I. При этом через схемы .«И 31-35 и транзисторы 37-41 возбуждаются

шипы обран;ения к памяти, номер ОЗУ и информациоиная магистраль.

То ОЗУ, номер которого совпадает с номером на щипах, либо сцепляется с магистралью для проведения сеанса связи (если опо свободно) и по окончании этого сеанса выдает импульс «ответ связи, либо вырабатывает сигнал «ответ занятости (если оно занято внутренним ЦИКЛОЛ1 чтения или записи от предыдущего запроса).

В случае появления сигнала «ответ связи в процессоре с самым старшим приоритетом гасится триггер запятия магистрали 12 и во всех процессорах гасятся триггеры запроса обращения //, а через схему «ИЛИ 18 и

транзистор 36 возбуждается шина «опрос обращения и формирователя импульсов опроса 13. Кроме того, через схему «И 25 во всех процессорах, где есть запрос обращения к памяти, вновь установятся в «1 триггеры запроса обращения //. В процессоре с самым стар.шим приоритетом через схемы «И 16 и «ИЛИ 14 возбуждается выходной импульс опроса, который посгупает па следующий процессор.

Если из ОЗУ прнщсл сигнал «ответ занятости, то он через схему «И 17 и «ИЛИ 14 возбуждает выходную щину импульса опроса в том случае, когда данный процессор дал запрос на обслуживание, по еще не требз ется

срочное подключепие его к магистрали и он может еще некоторое время ждать (триггер срочности 10 стоит в «О).

Предмет изобретения

Устройство приоритетного подключения процессоров к общей магистрали, содержащее триггеры, логические схе.мы, формирователи импульсов и транзисторы, отличающееся тем,

что, с целью сокрапгепия оборудовапия и увеличения быстродействия, входная шипа опроса в каждом процессоре соединена со входом первой схемы «И, другие входы которой сосдинсаг с .нулевыми выходами триггера приорптета н триггера запроса обрандения, а выход соедп) со входом первой схемы «ИЛИ, вырабатывающей выходной импульс опроса, другой вход первой схемы «ИЛИ соединен со входом второй схемы «И, входы которой

памяти и с выходом триггера срочности, третий вход первой схемы «ИЛИ соединен с выходом третьей схемы «И, входы которой соединены с нулевым выходом триггера запроса обращения, единичным выходом триггера приоритета и выходом формирователя импульсов, вход которого соединен с эмиттером транзистора, подключенного своим входом к выходу второй схемы «ИЛИ, вход которой через

схему «И подключен к входной шине опроса и единичному выходу триггера приоритета, другой вход второй схемы «ИЛИ связан с шиной гашения запросов, подключенной к нулевому входу триггера занятия магистрали, единичный выход которого соединен со входами схем «И, выходы которых соединены со входами транзисторов, эммитеры которых соединены с обш.ей магистралью обслулшвания.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения процессоров с внешними абонентами | 1978 |

|

SU750472A1 |

| Устройство для обмена данными в вычислительной сети | 1988 |

|

SU1599864A1 |

| Многоканальное устройство для обмена данными между модулями вычислительной системы | 1985 |

|

SU1256037A1 |

| Устройство для сопряжения вычислительной машины с магистралью | 1981 |

|

SU980088A2 |

| Устройство для приоритетного обращения процессоров к общей памяти | 1979 |

|

SU883905A2 |

| Устройство для сопряжения микропроцессора с магистралью | 1985 |

|

SU1302287A1 |

| Устройство для обмена информацией | 1983 |

|

SU1198528A1 |

| Многоканальное устройство для обмена данными между модулями вычислительной системы | 1987 |

|

SU1444796A1 |

| Коммутирующая сеть | 1986 |

|

SU1411766A1 |

| Устройство для сопряжения двух магистралей | 1988 |

|

SU1509915A2 |

Даты

1971-01-01—Публикация