Предлагаемый динамический инвертор может быть использован для построения разнообразных цифровых схем, в частности сдвиговых регистров, устройств памяти в виде линий задержки.

Известны схемы однотактных динамических инверторов, выполненные на транзисторах со структурой металл - диэлектрик - полупроводник, содержащие соединенные последовательно инвертирующий и разделительный транзисторы, затворы которых подключены соответственно ко входу инвертора и входу тактовых импульсов, запоминающий конденсатор, включенный между стоком разделительного транзистора и общей шиной питания, и дополнительный конденсатор.

Предложенное устройство отличается от известных тем, что содержит нагрузочный транзистор, сток и затвор которого соединены со стоком и затвором разделительного транзистора, а дополнительный конденсатор включен между затвором и истоком нагрузочного транзистора.

Это позволяет повысить помехозащищенность устройства.

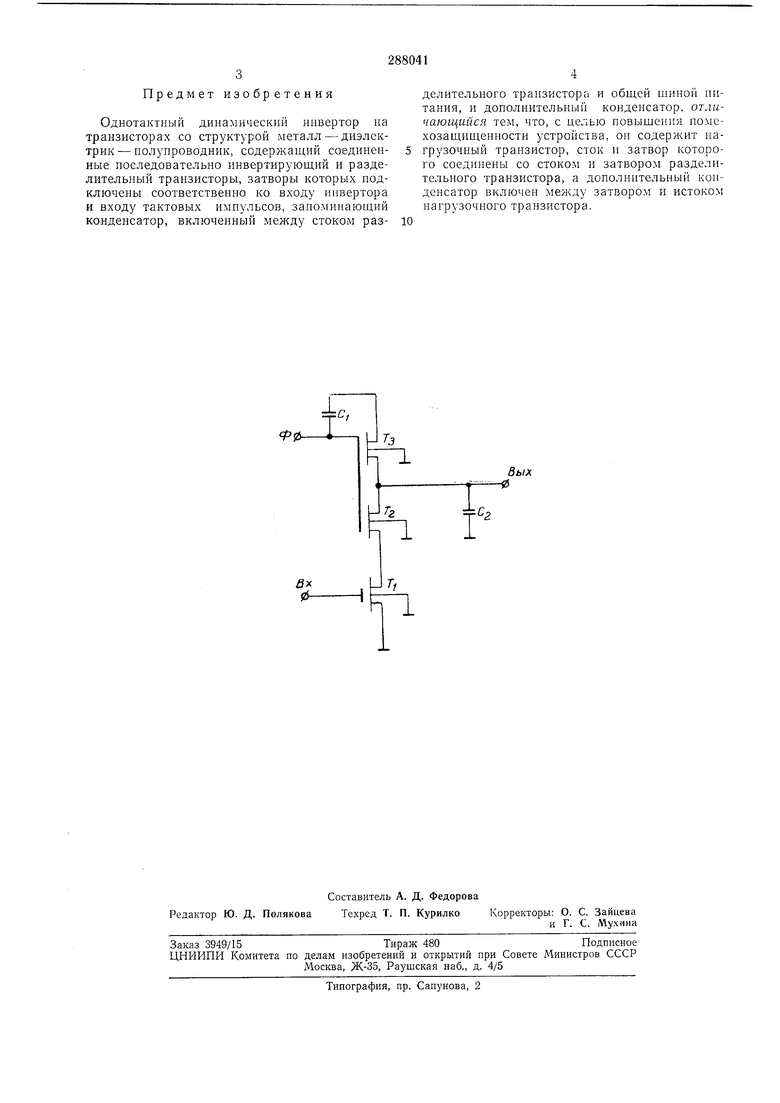

Схема предлагаемого динамического инвертора представлена на чертеже.

ход схемы от его входа; через дополнительный конденсатор С, и нагрузочный транзистор Та заряжается запоминающий конденсатор Со, который подключен к стоку транзистора Г., и к общей щине устройства.

Инверсия информации, содержащейся на входе инвертора, осуществляется следующим образом.

Предположим, что транзистор TI закрыт и на его затворе относительно общей шины напряжение равно нулю. Тактовый импульс, появляющийся на входе Ф, открывает транзисторы Т2 и Гз, и конденсатор Со заряжается по

цепи: генератор, конденсатор С, транзистор Гз, конденсатор Со, общая щина. Если же транзистор TI открыт, то конденсатор Cz зарядиться не сможет, так как окажется зашунтированным двумя последовательно соединенными и открытыми транзисторами TI и Го.

Помехозащищенность предлагаемой схемы вдвое выще, чем в известных инверторах: непосредственное прохождение сигнала от генератора тактовых импульсов связано с наличием двух проходных емкостей, которые представляют собой емкости затвор - исток транзистора Го и затвор - сток транзистора TI, что уменьщает необходимую амплитуду на3Предмет изобретения Однотактыый динамический инвертор на транзисторах со структурой металл - диэлектрик- иолупроводник, содержащий соединенные последовательно инвертирующий и разделительный транзисторы, затворы которых нодключены соответственно ко входу инвертора и входу тактовых имиульсов, заноминающий конденсатор, включенный между стоком разделительного транзистора и общей шиной питания, и донолнительный конденсатор, отличающийся тем, что, с целью повышения помехозащищенности устройства, он содержит нагрузочный транзистор, сток и затвор которого соединены со стоком и затвором разделительного транзистора, а дополнительный конденсатор включен между затвором и истоком нагрузочного транзистора.

| название | год | авторы | номер документа |

|---|---|---|---|

| ОДНОТАКТНЫЙ ДИНАМИЧЕСКИЙ ИНВЕРТОР НА МОП-ТРАНЗИСТОРАХВСЕСОЮЗНАЯ?"1-!Й?г •*•.tin»!?Л-'ЮЯУ"Н^с.иР>&пИС~"?НА•—" - -^ •„.«^-«м—-^ | 1972 |

|

SU337943A1 |

| ДИНАМИЧЕСКИЙ ИНВЕРТОР | 1969 |

|

SU253869A1 |

| Динамический инвертор | 1982 |

|

SU1023659A1 |

| Квазистатическое счетное устройство на МДП-транзисторах | 1986 |

|

SU1319255A1 |

| ДИНАМИЧЕСКИЙ ИНВЕРТОР НА ПОЛЕВЫХ ТРАНЗИСТОРАХ | 1969 |

|

SU235100A1 |

| Адресный формирователь | 1981 |

|

SU1014027A1 |

| Однотактный динамический инвертор | 1979 |

|

SU792568A1 |

| Формирователь импульсов регенерации для запоминающих устройств на мдп-транзисторах | 1974 |

|

SU500581A1 |

| Формирователь сигнала выборки на МДП-транзисторах | 1986 |

|

SU1338024A1 |

| Динамический усилитель считывания на МДП-транзисторах | 1986 |

|

SU1336101A1 |

вых

-0

Даты

1970-01-01—Публикация