Динамический иивертор на полевых транзисторах со структурой металл - окисел - иолупроводиик (МОП-транзисторах) относится к быстродействующим элементам цифровых вычислительных машин и системам автоматики.

Известны динамические инверторы на МОПтранзисторах, содержащие входной, нагрузочный и проходкой МОП-транзисторы и запоминающий конденсатор.

Пагрузочный транзистор включается тактовым имнульсом независимо от величины логического уровня на входе инвертора. Включение нагрузочного транзистора, когда на входе высокий логический уровень, приводит к тому, что потенциал, до которого разряжается входной запоминающий конденсатор следующего инвертора UА , отличен от нуля (за счет протекания тока через делитель, образованный входным и нагрузочным транзисторами). Это ухудшает помехоустойчивость схемы, пропорциональную величине(бд - UA ).

Для обеспечения помехоустойчивости схемы {UA Lo) необходимо брать нагрузочный транзистор с малыми рабочими токами, что ухудшает время зарядки входного запоминающего конденсатора последующего инвертора и, следовательно, снижает быстродействие схемы. Включение нагрузочного транзистора, когда на входе инвертора высокий уровень напряжения, приводит к дополнительному рассеянию мощности, кроме той, которая необходима для перезарядки запоминающего конденсатора.

Предложенный динамнческий инвертор на полевых .ЮП-транзисторах отличается тем, что введена дополнительная цепочка иоследовательно соединенных управляющего конденсатора и дополнительного транзистора, включенного но схеме с заземленным истоком, сток которого соединен с затвором нагрузочного МОП-транзнстора. н через управляющий конденсатор - с шиной тактовых имиульсов, а затвор подсоединен ко входу инвертора, что

позволяет повысить быстродействие и увеличить помехозащищеиность схемы.

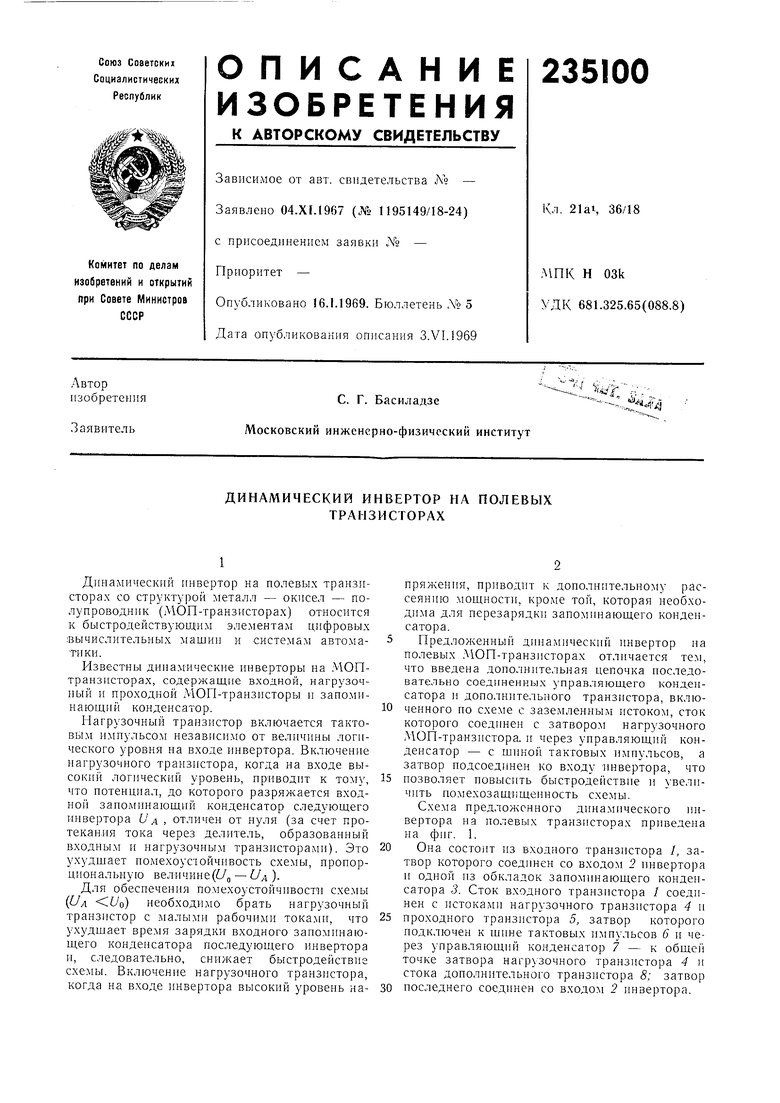

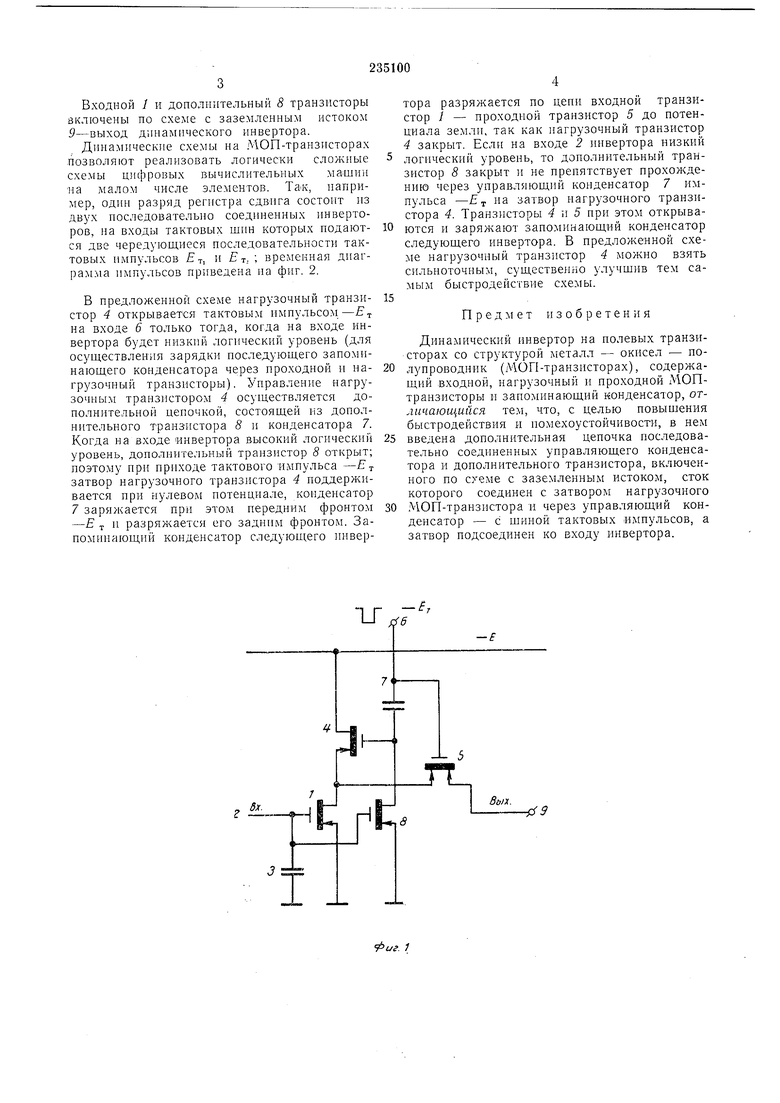

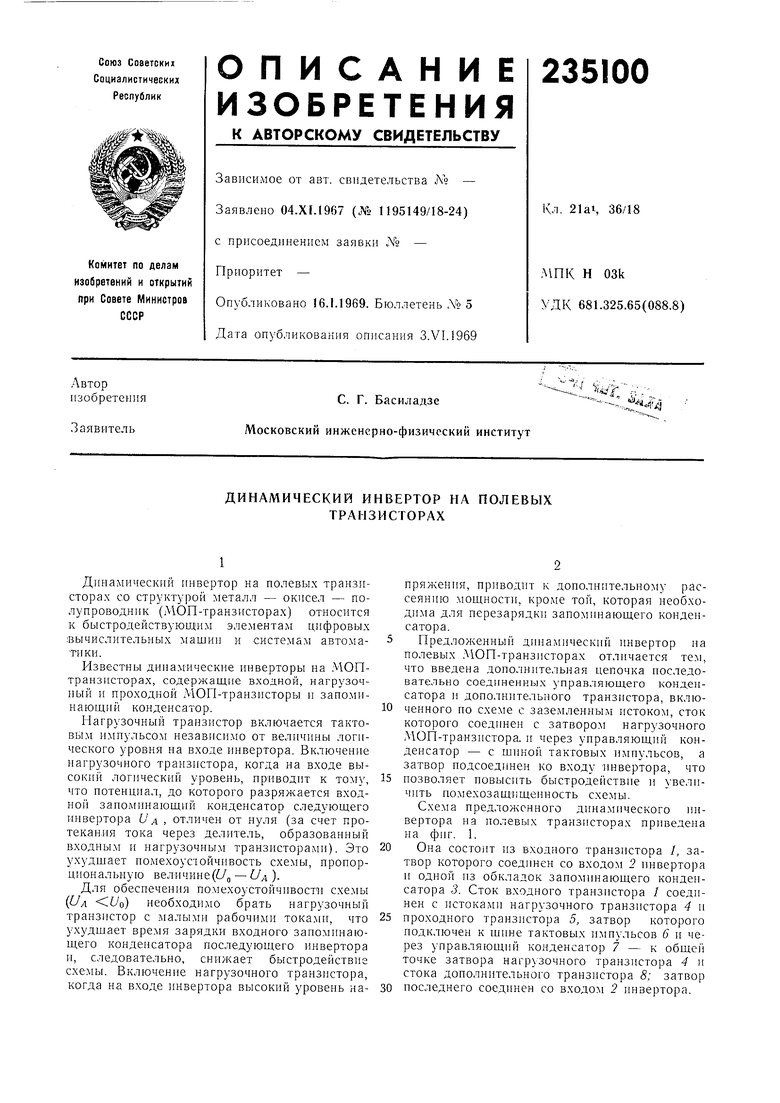

Схема предложенного динамического инвертора на полевых транзисторах приведена на фиг. 1.

Она состоит из входного транзистора /, затвор которого соединен со входом 2 инвертора и одной из обкладок запоминающего конденсатора 3. Сток входного транзистора / соедннен с нстоками нагрузочного транзистора 4 и

проходного транзистора 5, затвор которого подключен к шине тактовых импульсов 6 и через управляющий конденсатор 7 - к общей точке затвора нагрузочного транзистора 4 и стока дополнительного транзистора 8: затвор

Входной 1 и дополнительный 8 транзнсторы включены по схеме с заземленным истоком 9-выход динамического инвертора.

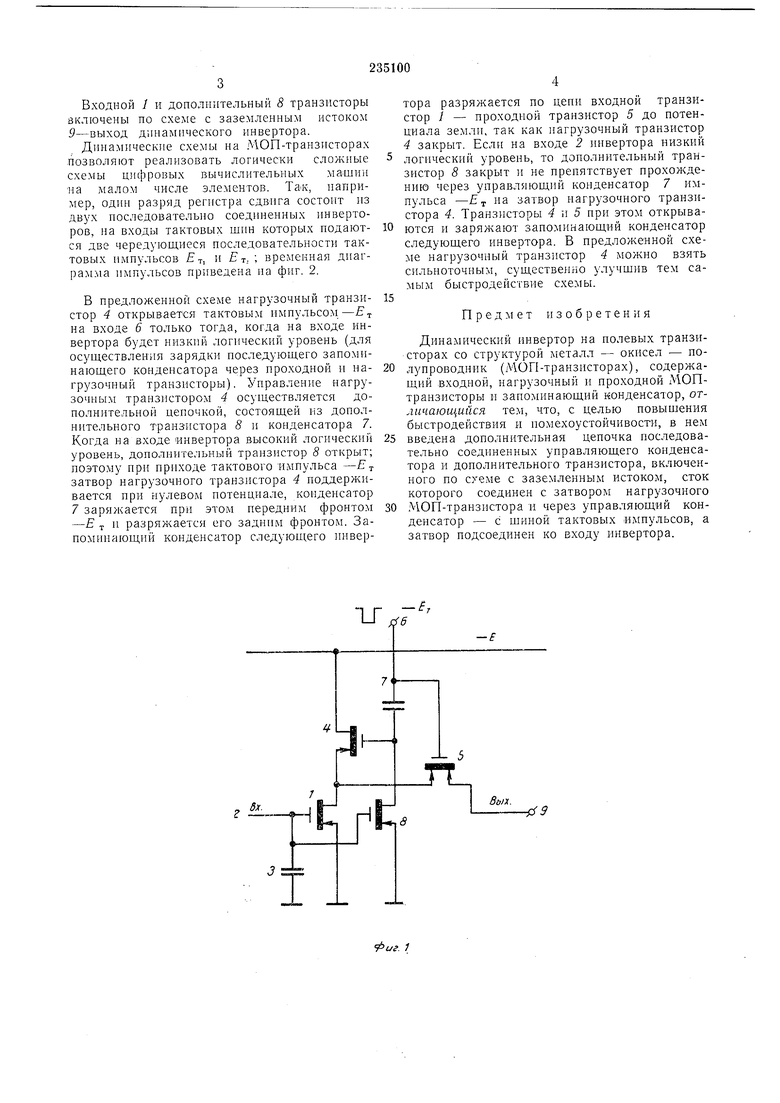

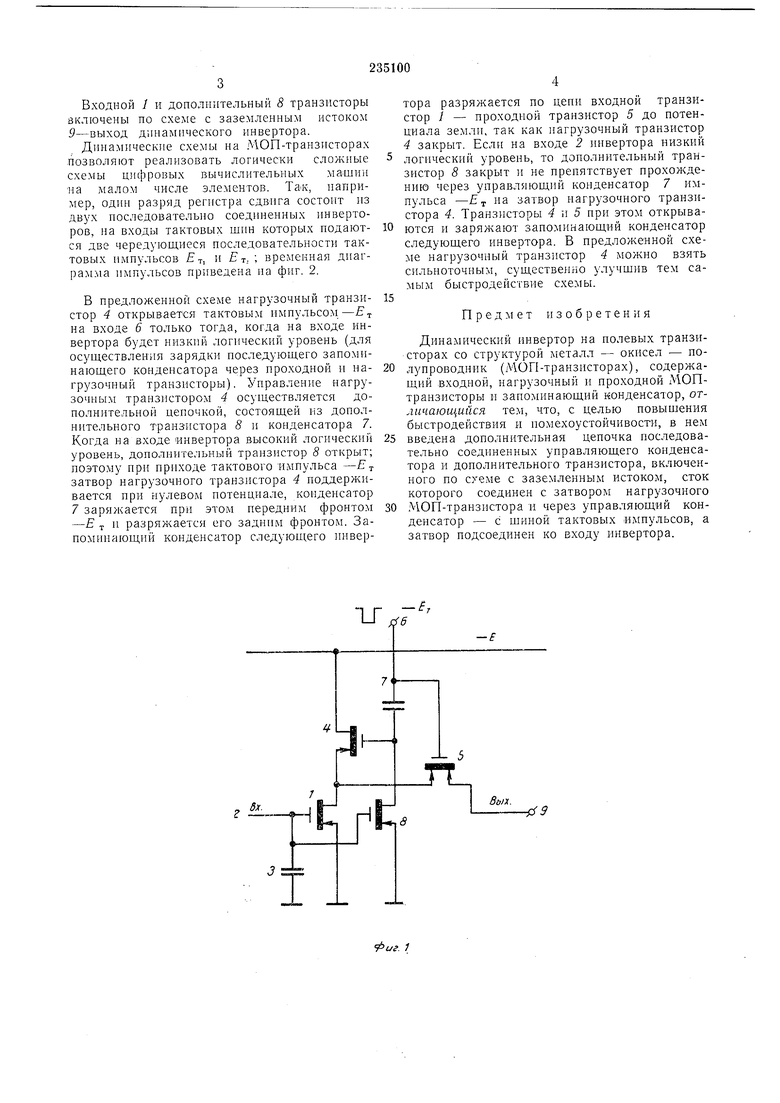

Динамические схемы на МОП-транзисторах .позволяют реализовать логически сложные схемы цифровых вычислительных машин на малом чнсле элементов. ТаК, например, один разряд регистра сдвига состоит из двух последовательно соединенных инверторов, на входы тактовых шин которых нодаются две чередующиеся последовательности тактовых импульсов т, и Е т, ; временная днаграл ма нмпульсов приведена на фиг. 2.

В предложенной схеме нагрузочный транзистор 4 открывается тактовым импульсом-Е на входе 6 только тогда, когда на входе инвертора будет низкий логический уровень (для осугцествления зарядки последующего запоминающего конденсатора через проходной и нагрузочный транзнсторы). Управление нагрузочным транзистором 4 осуществляется дополнительной цепочкой, состоящей из дополннтельного транзистора 8 и конденсатора 7. Когда на входе инвертора высокий логический уровень, дополнительный транзистор 8 открыт; поэтому при приходе тактового импульса затвор нагрузочного транзистора 4 поддерживается ири нулевом потенциале, конденсатор 7 заряжается при этом передним фронтом -Е т и разряжается его задним фронтом. Запоминающий конденсатор следующего инвертора разряжается по цени входной транзистор / - проходной транзистор 5 до потенциала землн, так как нагрузочный транзистор 4 закрыт. Если на входе 2 imeepTopa низкий

логический уровень, то дополнительный транзистор 8 закрыт и не препятствует прохождению через управляющий конденсатор 7 импульса иа затвор нагрузочного транзистора 4. Транзисторы 4 и 5 при этом открываются и заряжают запоминающий конденсатор следующего инвертора. В предложенной схеме нагрузочный транзистор 4 можно взять сильноточным, существенно улучщив тем самым быстродействие схемы.

Предмет изобретения

Динамический инвертор на нолевых транзисторах со структурой металл - окисел - полупроводник (МОП-транзисторах), содержащий входиой, нагрузочный и проходной ЛЮПтранзнсторы н запоминающий конденсатор, отличающийся тем, что, с целью повышения быстродействия и помехоустойчивости, в нем введена дополнительная цепочка последовательно соединенных управляющего конденсатора и донолнительного транзистора, включенного по схеме с заземленным истоком, сток которого соединен с затвором нагрузочного МОП-транзистора и через управляющий кондеисатор - с; тиной тактовых импульсов, а затвор подсоединен ко входу инвертора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Двухтактный сдвигающий регистр | 1968 |

|

SU736172A1 |

| Динамический усилитель считывания на МДП-транзисторах | 1986 |

|

SU1336101A1 |

| Адресный усилитель | 1982 |

|

SU1062786A1 |

| РЕВЕРСИВНОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО ДИНАМИЧЕСКОГО ТИПА НА ПОЛЕВЫХ ТРАНЗИСТОРАХ С ИЗОЛИРОВАННЫМ ЗАТВОРОМ | 2001 |

|

RU2184418C1 |

| Формирователь сигналов выборки адресов | 1981 |

|

SU1003141A1 |

| СВЕРХБЫСТРОДЕЙСТВУЮЩЕЕ СВЕРХИНТЕГРИРОВАННОЕ БИМОП ОЗУ НА ЛАВИННЫХ ТРАНЗИСТОРАХ | 1999 |

|

RU2200351C2 |

| ДИНАМИЧЕСКОЕ ПОСЛЕДОВАТЕЛЬНОЕ ФУНКЦИОНАЛЬНОЕ УСТРОЙСТВО | 2005 |

|

RU2392672C2 |

| ДВУХТАКТНЫЙ СДВИГАЮЩИЙ РЕГИСТР | 2014 |

|

RU2549136C1 |

| Формирователь сигнала выборки на МДП-транзисторах | 1986 |

|

SU1338024A1 |

| Логический элемент "не" | 1976 |

|

SU573884A1 |

-1 г -f. и

-

r,

208

f

20&

Даты

1969-01-01—Публикация