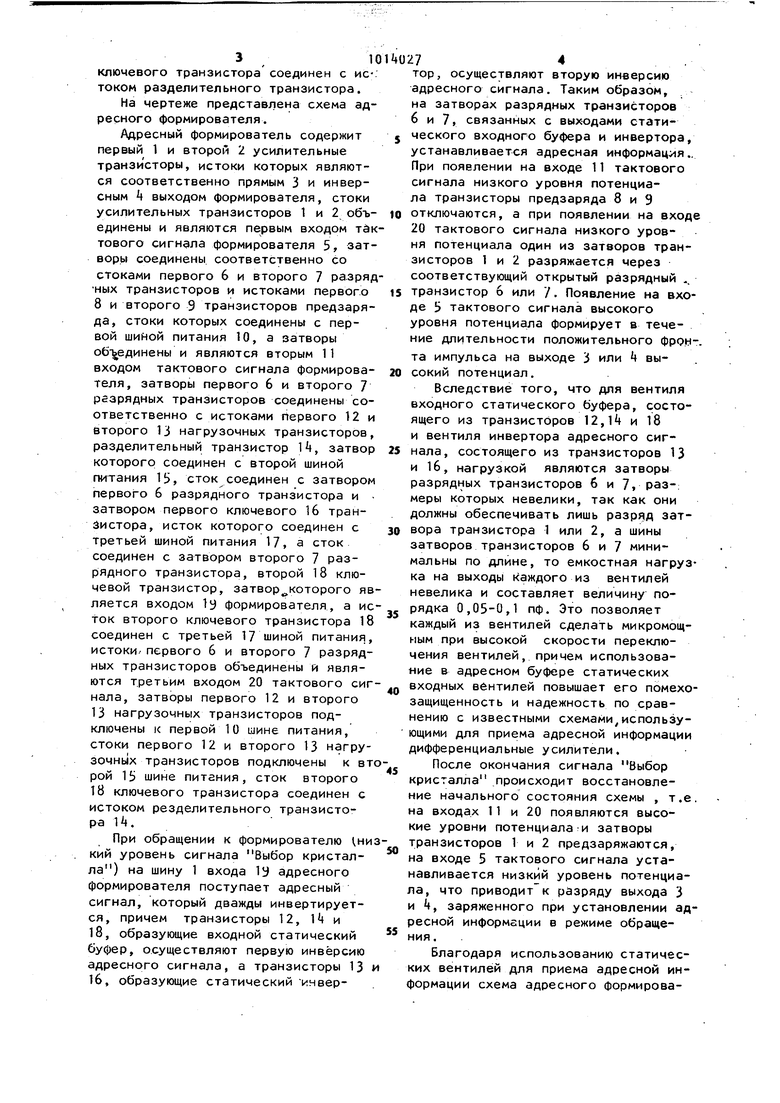

Изобретение относится к вычисли тельной технике и может быть использовано в микросхемах памяти на МДП транзисторах.. В интегральных схемах-памяти на МДП транзисторах для согласования схемы с ТТЛ схемами, приема адреса и формирования прямого и инверсного адресных сигналов, управляющих работой дешифратора адреса, обы но используются статические схемы адресных формирователей, где формирЬ вание адресных сигналов осуществляе ся при помощи инверторов 1 . Это простейшее решение определяло, вследствие большой емкости адрес ных шин, невысокое быстродействие ус ройства при сравнительно высокой потребляемой мощности, свойственной статическим схемам, С целью увеличения быстродействия и уменьшения потребляемой мощности для считывания адресной информации используют дифференциальные усилители, а для формирования адресных сигналов - динамические повторители, по ключенные к каждому из плеч дифференциального усилителя.. Использование дифференциальных усилителей позволяет, с высокой скоростью формировать на затворах динамических повторителей прямой и инверсный адресные сигналы, а использование динамических повторителей позволяет, без потерь мощности в адресном формирова теле, установить адресную информацию на адресных шинах Однако дифференциальные усилители являются наиболее сложными узлами микросхемы, они предъявляют жесткие требования к качеству технологического процесса, особенно к разбросам параметров элементов. Кроме того, дифференциальные усилители чувст вительны к помехам, воз.;икающим в интегральных схемах при переключении логических вентилей, и для обеспечения высокой чувствительности усилителей требуется тщательная проработка конструкторских решений. Наиболее близким к предлагаемому по технической сущности и схемному решению является адресный формирователь, в котором для увеличения скорости считывания информации и для увеличения помехоустойчивости дифференциального усилителя введена обрат ная связь .между динамическими повторителями и нагрузочными транзисторами дифференциального усилителя ГЗ . Известная схема обладает перечисленными выше недостатками, связанными с использованием дифференциальных усилителей, причем ее использование возможно при условии применения схемы памяти в блоке памяти, где допустимые амплитуды системных что обеспомех жестко ограничены, печивается установкой на плате шинных формирователей, уменьшающих длину адресных шин за счет уменьшения количества объединяемых адресных входов. Целью изобретения является увеличение помехоустойчивости формирователя. Поставленная цель достигается тем. что адресный формирователь, содержа-: щий первый и второй усилительные транзисторы, истоки которых являются соответственно прямым и инверсным выходом формирователя, стоки усилительных транзисторов объединены и являются первым входом тактового сигнала формирователя, затворы соединены соответственно со стоками первого и второго разрядных транзисторов и истоками первого и второго транзисторов предзаряда, стоки которых соединены с первой шиной питания, а затворы объединены и являются вторым входом тактового сигнала формирователя, затворы первого и второго разрядных транзисторов соединены соответственно с истоками первого и второго нагрузочных транзисторов , разделительный транзистор, затвор которого соединен со второй шиной питания , сток соединен с затвором первого разрядного транзистора и затвором первого ключевого транзистора, исток которого соединен с третьей шиной питания, а сток соединен с затвором второго разрядного транзистора, второй ключевой транзистор, затвор которого является входом формирователя, а исток второго ключевого транзистора соединен с третьей шиной питания, дополнительно истоки первого и второго разрядных транзисторов объединены и являются третьим входом тактового сигнала, затворы первого и второго нагрузочных транзисторов подключены к первой шине питания, стоки первого и второго нагрузочных транзисторов подключены к второй шине Питания, сток второго ключевого транзистора соединен с истоком разделительного транзистора. На чертеже представлена схема адресного формирователя. Адресный формирователь содержит первый 1 и второй 2 усилительные транзисторы, истоки которых являются соответственно прямым 3 и инверсным А выходом формирователя, стоки усилительных транзисторов 1 и 2 объединены и являются первым входом так тового сигнала формирователя 5, затворы соединены, соответственно со стоками первого 6 и второго 7 ра.зряд ных транзисторов и истоками первого 8 и второго 9 транзисторов предзаряда, стоки которых соединены с первой шиной питания 10, а затворы об- единены и являются вторым 1 1 входом тактового сигнала формирователя, затворы первого 6 и второго 7 разрядных транзисторов соединены соответственно с истоками первого 12 и второго 13 нагрузочных транзисторов разделительный транзистор 1, затвор которого соединен с второй шиной питания 15, сток соединен с затвором первого 6 разрядного транзистора и затвором первого ключевого 16 транзистора, исток которого соединен с третьей шиной питания 17, а сток соединен с затвором второго 7 разрядного транзистора, второй 18 ключевой транзистор, затвор которого яв ляется входом 1у формирователя, а ис tOK второго ключевого транзистора 18 соединен с третьей 17 шиной питания ИСТОКИ первого б и второго 7 разрядных транзисторов объединены и являются третьим входом 20 тактового сиг нала, затворы первого 12 и второго 13 нагрузочных транзисторов подключены к первой 10 шине питания, стоки первого 12 и второго 13 нагрузочнУх транзисторов подключены к вт рой 15 шине питания, сток второго 18 ключевого транзистора соединен с истоком резделительного транзистора 1. При обращении к формирователю ни кий уровень сигнала Выбор кристалла) на шину 1 входа 1У адресного формирователя поступает адресный сигнал, который дважды инвертируется, причем транзисторы 12, и 18, образующие входной статический буфер, осуществляют первую инверсию адресного сигнала, а транзисторы 13 16, образующие статический инвертор, осуществляют вторую инверсию адресного сигнала. Таким образом, на затворах разрядных транзисторов 6 и 7, связанных с выходами статического входного буфера и инвертора, устанавливается адресная информац 1Я.. При появлении на входе 11 тактового сигнала низкого уровня потенциала транзисторы предзаряда 8 и 9 отключаются, а при появлении на входе 20 тактового сигнала низкого уровня потенциала один из затворов транзисторов 1 и 2 разряжается через соответствующий открытый разрядный .. транзистор 6 или /. Появление на входе 5 тактового сигнала высокого уровня потенциала формирует в течение длительности положительного фрр.и-. та импульса на выходе 3 или k высокий потенциал. Вследствие того, что для вентиля входного статического буфера, состоящего из транзисторов 12,И и 18 и вентиля инвертора адресного сигнала, состоящего из транзисторов 13 и 1б, нагрузкой являются затворы разрядных транзисторов 6 и 7, рзз-: меры которых невелики, так как они должны обеспечивать лишь разряд затвора транзистора 1 или 2, а шины затворов транзисторов 6 и 7 минимальны по длине, то емкостная нагрузка на выходы каждого из вентилей невелика и составляет величину порядка 0,05-0,1 пф. Это позволяет каждый из вентилей сделать микромощным при высокой скорости переключения вентилей, причем использование в адресном буфере статических входных вентилей повышает его помехозащищенность и надежность по сравнению с известными схемами,использующими для приема адресной информации дифференциальные усилители. После окончания сигнала Выбор кристалла происходит восстановление начального состояния схемы , т.е. на входах 11 и 20 появляются высокие уровни потенциалаИ затворы транзисторов 1 и 2 предзаряжаются, на входе 5 тактового сигнала устанавливается низкий уровень потенциала, что приводит к разряду выхода 3 и 4, заряженного при установлении адресной информации в режиме обращения . Благодаря использованию статических вентилей для приема адресной информации схема адресного формирователя становится нечувствительной к системным помехам, возникающим на адресных шинах при работе схемы паг мяти .1В составе блока памяти. Типичная величина амплитуды системной помехи В (в ряде применений допускается амплитуда помехи, равнаи 1,2 в) при длительности сигнала помехи порядка 1-2 не. Дифференциальные усилители, обладающие чувстви тельностью в несколько десятков милливольт и защелкивающиеся на начальном участке фронта импульса, .включающего усилитель, т.е. за время порядка длительности сигнала поме хи, могут неверно считать адресную информацию, что приведет к агыбору чужой ячейки памяти, в то время как статические вентили , срабатывающие от полных перепадов логических уровней. После окончания дейст|вия помехи возвращаются в состояние, соответствующее принимаемой адресной информации. Расчет предлагаемой схемы адресного формирователя на помехоустойчивость показал возможность работы схемы при уровне помех с амплитудой 1,2 В. Использование адресного формирователя позволит увеличить надежность работы блока памяти и увеличить информационную емкость плат благодаря возможности объединения большего количества адресных выходов схем памяти и использованию меньшего количества развязывающих шинных формирователей.

/ S/

| название | год | авторы | номер документа |

|---|---|---|---|

| Формирователь сигналов выборки адресов | 1981 |

|

SU1003141A1 |

| Постоянное запоминающее устройство | 1986 |

|

SU1388950A1 |

| Адресный усилитель | 1982 |

|

SU1062786A1 |

| Выходной усилитель | 1981 |

|

SU1015436A1 |

| Ячейка фоточувствительного матричного запоминающего устройства | 1989 |

|

SU1709392A1 |

| Усилитель-формирователь | 1982 |

|

SU1065883A1 |

| Дешифратор адреса | 1982 |

|

SU1068999A1 |

| Полупроводниковое запоминающее устройство | 1981 |

|

SU987679A1 |

| Усилитель считывания для интегрального запоминающего устройства | 1976 |

|

SU928405A1 |

| Усилитель записи-считывания на КМДП-транзисторах | 1988 |

|

SU1571673A1 |

АДРЕСУЙ ФОРМИРОВАТЕЛЬ, содержащий первый и второй усилительные транзисторы, истоки которых являются соответственно прямым и инверсным выходом формирователя, стоки усилительных транзисторов объединены и являются первым входом тактового сигнала формирователя, затворы соединены соответственно со стоками первого и второго разрядных транзисторов и истоками первого и второго транзисторов предзаряда, стоки которых соединены с первой шиной питания, а затворы объединены и.являются вторым входом тактового сигнала формирователя, затворы первого и в;торого. разрядных транзисторов соединены соответственно с истоками первого и второго нагрузочных транзисторов, разделительный транзистор, затвор которого соединен со второй шиной питания, сток соединен с затвором первого разрядного транзистора и затвором первого ключевого тpaнзиctopa, исток которого соединен с третьей шиной питания, а сток соединен с затвором второго разрядного транзистора, второй ключевой транзистор, затвор которого является входом формирователя , а исток второго ключевого транзистора соединен с третьей шиной питания, о тл и чающий ся W тем, что, с целью увеличения помехоустойчивости формирователя, истоки первого и второго разрядных транзис§ торов объединены и являются третьим входом тактового , затворы первого и второго нагрузочных транзисторов подключены к первой шине питания , стоки первого и второго нагрузочных транзисторов подключены к второй шине питания, сток второго ключек вого транзистора соединен с истоком , разделительного транзистора. ч

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| IEEE J | |||

| of Solid-State Circuits, 1976, № 5, p.570-573 | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Патент США № 4146802, кл | |||

| Приспособление для выпечки формового хлеба в механических печах с выдвижным подом без смазки форм жировым веществом | 1921 |

|

SU307A1 |

| Дверной замок, автоматически запирающийся на ригель, удерживаемый в крайних своих положениях помощью серии парных, симметрично расположенных цугальт | 1914 |

|

SU1979A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Электроника, 1978, № 7, с | |||

| Способ образования коричневых окрасок на волокне из кашу кубической и подобных производных кашевого ряда | 1922 |

|

SU32A1 |

Авторы

Даты

1983-04-23—Публикация

1981-09-21—Подача