Предлагаемое изобретение относится к устройствам .кодирования информации, позволяюш,им обнаружить и исправить ошибки при записи и воспроизведении информации.

Известные устройства формируют символы для ОДНОЙ дополнительной дорон ки и одной дополнительной строки на каладый кадр фиксируемой информации из условия обеспечения нечетности числа единиц вдоль каждой строки. Контрольные символы в дополнительных строках определяются в результате математических преобразований, осущестВляемых специальным регистром с обрат1ными связями через сумматоры по модулю 2.

Предложенное устройство отличается тем, что оно содержит схему формирования коитрольного сигнала по диагонали, выполненную на ячейках памяти и сумматорах, причем выходы предыдущих сумматоров подключены ко 1входам последующих через ячейки памяти, а выходной сумматор соединен со входами блока записи и схемы свертки по модулю 2, выход которой связан с одним из входов выходного сумматора; выходы входиого регистра подключены к другим входам сумматоров и соответствующим входам схемы сварки но модулю 2 и ко входу схемы формирования контрольного сигнала по диагонали.

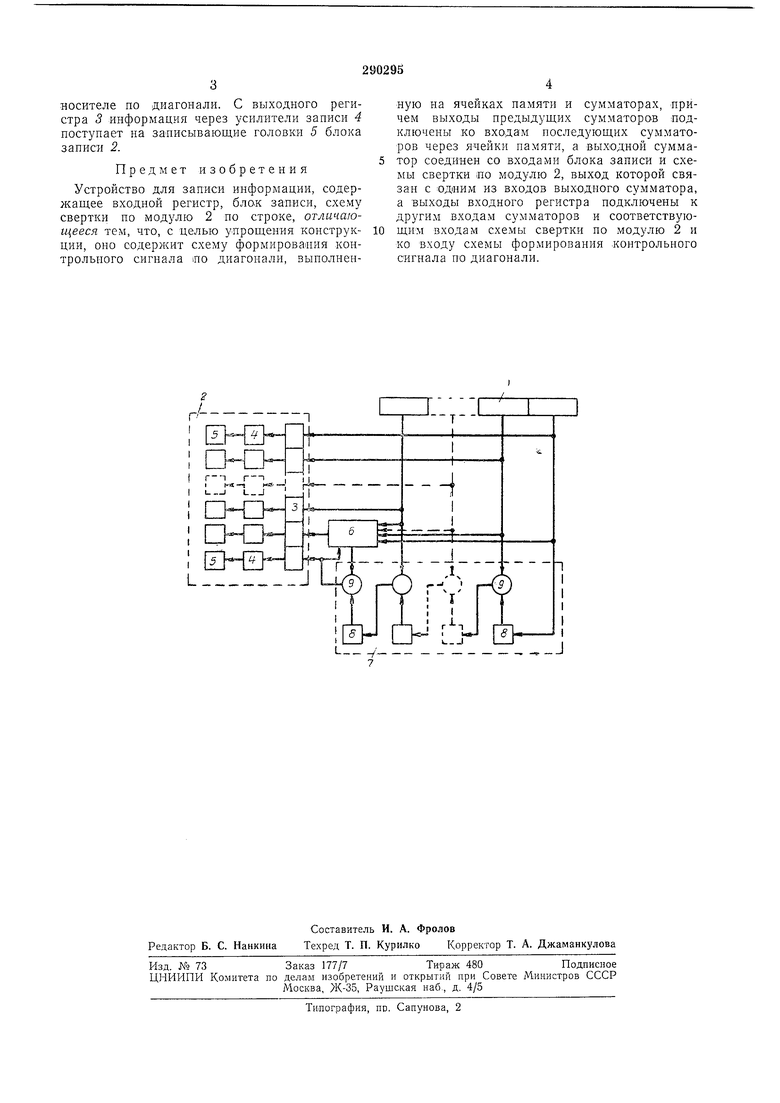

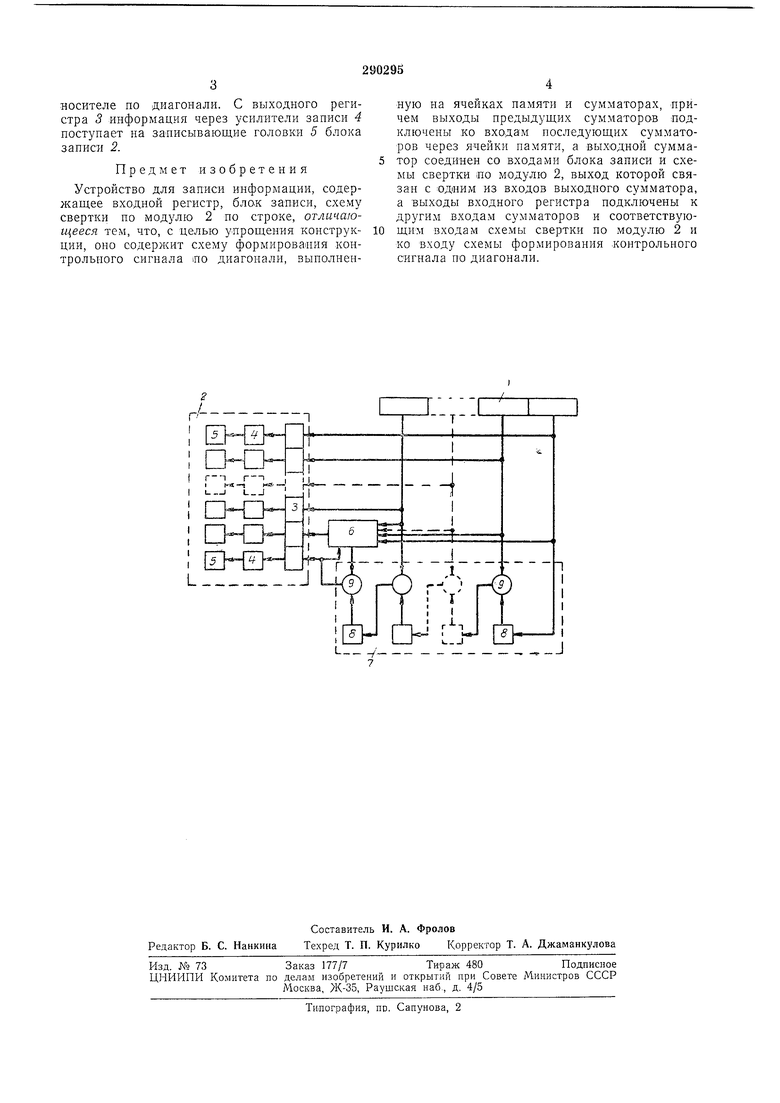

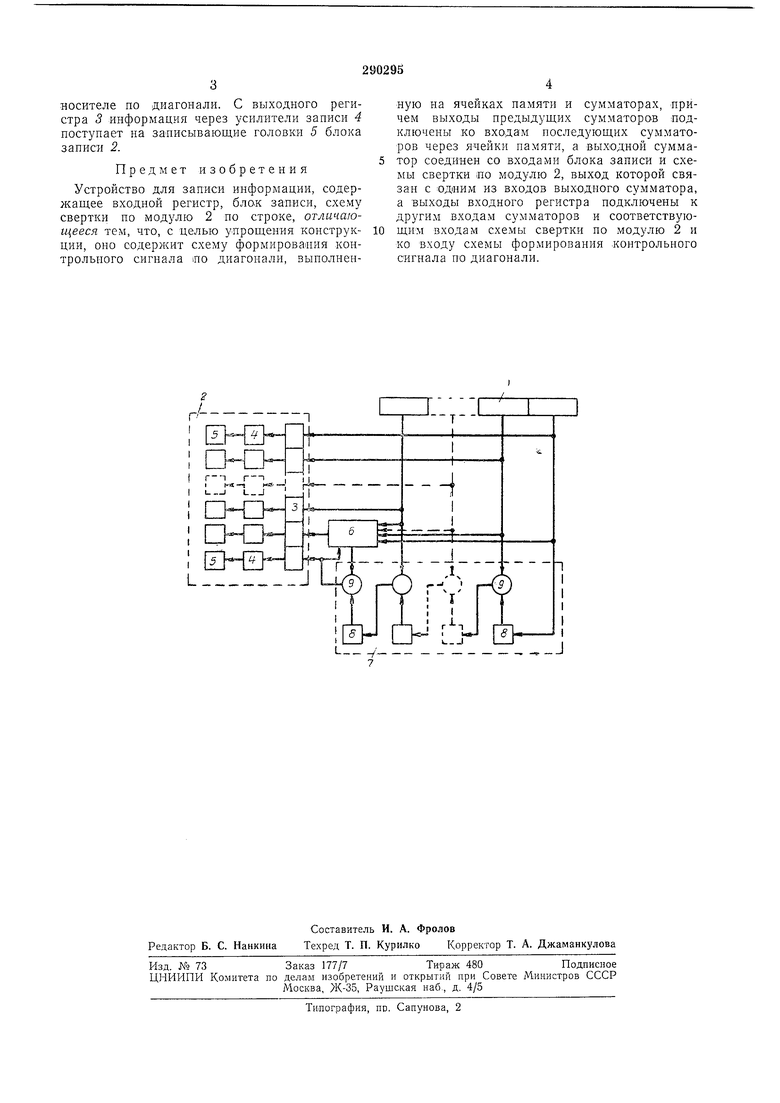

Это позволяет упростить конструкцию устройстваБлок-схема предложенного устройства представлена па чертеже, где: / - входной

регистр; 2 - блок записи, содерлсащий выходной регистр 3, усилители записи 4, записывающие головки 5; 6-схема свертки по модулю 2 по строке; 7 - схема формирования контрольного сигнала по диагонали, содержащая ячейки памяти 8 и сумматоры 9. Устройство работает следующим образом. Подлежащая кодированию информация поступает со входного регистра 1 на выходной регистр 3 блока записи 2, необходимый

для задержки информационных сигналов на время образования контрольных сигналов, на схему 6 свертки по модулю 2 для формирования контрольного сигнала по строке и на схему 7 формирования контрольного сигнала по диагонали. Сигналы со входного регистра 1 за исключением сигнала, соответствующего первой информационной дорожке, поступают на один из входов сумматоров 9, на вторые входы которых с ячеек памяти 8

подаются сигналы предыдущей строки, сдвинутые на один разряд. Производя носледовательное суммирование, на выходе выходного сумматора 9 получают контрольные сигналы, являющиеся результатом сложения но

носителе по диагонали. С выходного регистра 3 информация через усилители заниси 4 иоступает на записывающие головки 5 блока заииси 2.

Предмет изобретения

Устройство для записи информации, содержащее входной регистр, блок записи, схему свертки по модулю 2 по строке, отличающееся тем, что, с целью упрощения конструкции, оно содержит схему формирова1ния контрольного сигнала ло диагонали, выполненную на ячейках памяти и сумматорах, причем выходы предыдущих сумматоров подключены ко входам последующих сумматоров через ячейки памяти, а выходной сумматор соединен со входами блока записи и схемы свертки то модулю 2, выход которой связан с одним из входов выходного сумматора, а выходы входного регистра подключены к другим входам сумматоров и соответствующим входам схемы свертки по модулю 2 и ко входу схемы формирования контрольного сигнала по диагонали.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО для ИСПРАВЛЕНИЯ ОШИБОК | 1971 |

|

SU292175A1 |

| Устройство для задания программы | 1979 |

|

SU849148A1 |

| Устройство для записи и воспроизведения информации | 1986 |

|

SU1501104A1 |

| Устройство для исправления ошибок при параллельном считывании двоичной информации | 1972 |

|

SU455352A2 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР С КОРРЕКЦИЕЙ ОШИБОК В ДВУХ БАЙТАХ ИНФОРМАЦИИ | 2021 |

|

RU2758410C1 |

| Устройство для записи и воспроизведения информации | 1974 |

|

SU482772A1 |

| Запоминающее устройство с исправлением дефектов и ошибок | 1987 |

|

SU1536445A1 |

| Устройство для контроля блоков памяти | 1979 |

|

SU771733A1 |

| Устройство кодирования информации для памяти с записью неполными словами | 1983 |

|

SU1267485A1 |

| Устройство для сопряжения процессора с памятью | 1982 |

|

SU1059560A1 |

Даты

1971-01-01—Публикация