Изобретение относится к области вычислительной техники.

Известны устройства прерывания, включающие в себя регистр прерывания, регистр защиты, схемы поразрядного сравнения в поиска крайней единицы.

Предлагаемое изобретение дает возмол ность выполнять прерывание в мультивычислительной системе, прерывающее работу вычислителя, на котором обрабатывается задача с наименьшим приоритетом.

Эта цель достигается введением регистров приоритетов по числу вычислителей, сохранением одного регистра прерывания и одного регистра номера команд при регистрах защиты по числу вычислителей. Для этого регистры приоритетов соединеиы с входами схем сравнения, вторые входы схем сравнения соединены с блоком поиска самой левой единицы в регистрах приоритета, а к третьим входам подсоединены выходы триггеров запрета-разрешения. Одни выходы схем сравнения подключены к вентилям между счетчиками команд и одним регистром номера команд, другие выходы через логическую схему соединены с триггером конца, выход которого соединен с блоком поиска самой левой единицы в регистрах приоритета, а второй вход триггера конца через логическую схему соединен с выходами схем сравнения кодов защиты, входы схем

сравнения кодов защиты соединены с дешифратором блока поиска самой левой единицы в регистре прерывания, выходами регистра прерывания, регистров защиты, триггеров защиты-разрешения. Вторые выходы схем сравнения кодов защиты через логическую схему, блок синхронизации и триггер начала соединены с блоком поиска самой левой единицы в регистре прерывания, один выход которого через вентили подсоединен к счетчикам команд вычислителей, а другой выход соединен с входом блока поиска самой левой единицы в регистрах приоритета. Схема синхронизации соединена с триггером запрета - разрешения по

всем вычислителям.

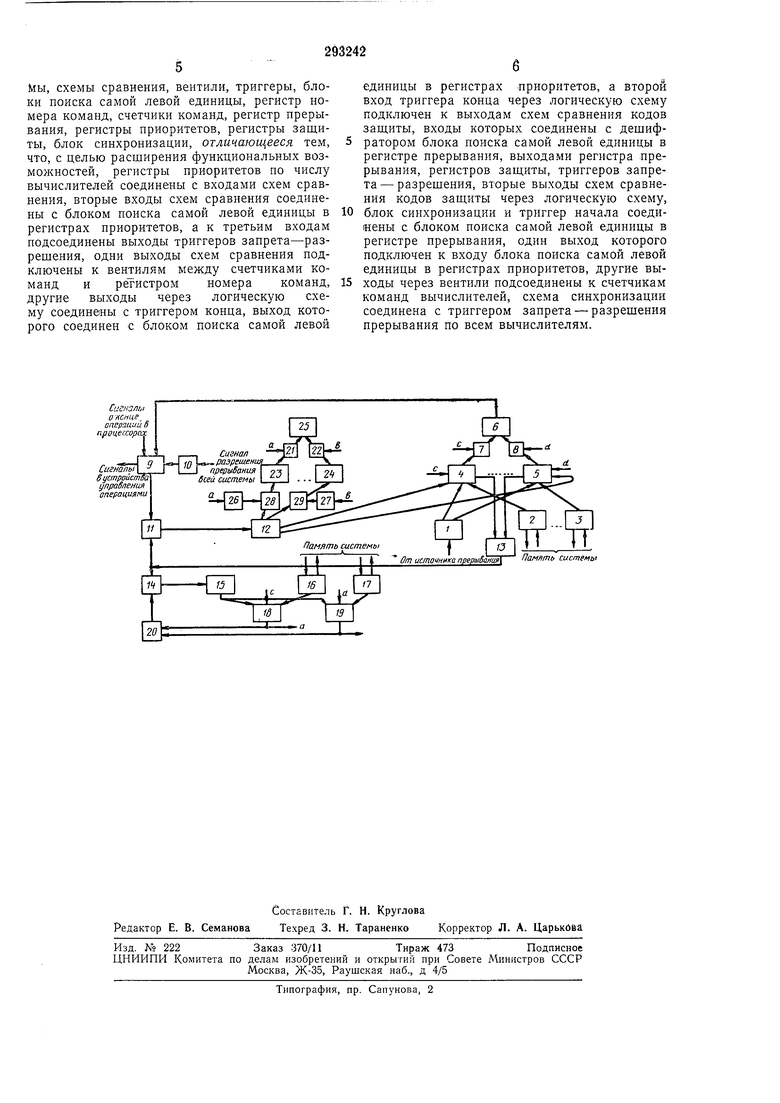

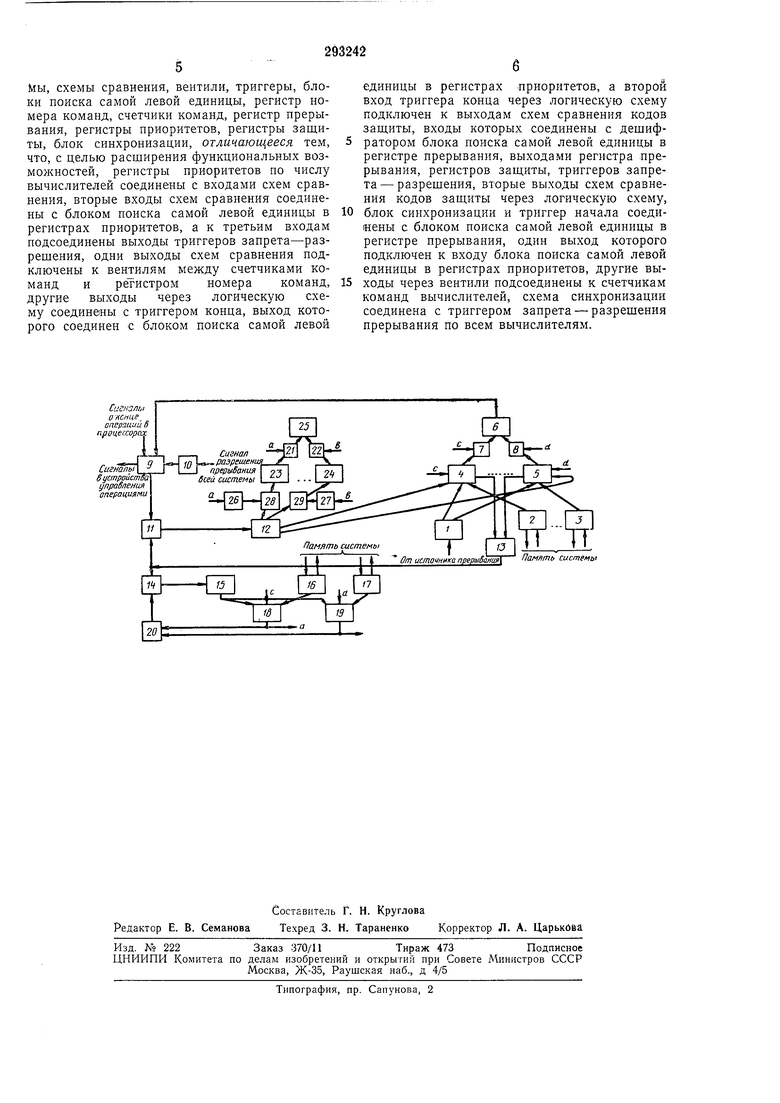

На чертеже представлена блок-схема устройства.

В работе устройства для прерывания можно отметить три основные стадии. На первой стадни выясняется возможно ли вообще прерывание хотя бы одного вычислителя. На второй стадии выясняется наиболее приоритетная причина прерывания, которой соответствует самая левая единица в регистре прерывания,

не защищенная кодами в регистрах защиты.

На третьей стадии выясняется вычислитель, на котором решается наименее приоритетная задача из всех разрешенных прерваться. Вычислитель прерывается, и происходит запомиВ процессе функционирования систелгы содержимое регистра прерывания / сравнивается с содержимым т регистров защиты (т - число процессоров).

В регистре прерывания 1 содержится информация о количестве и приоритете причин прерывания. В регистрах защиты содержатся коды защиты от прерывания соответствующего вычислителя, причем регистр 2 - регистр защиты первого вычислителя, регистр 3 - регистр защиты ш-го вычислителя.

Поразрядное сравнение осуществляется параллельно в m схемах сравнения, где схема 4 - схема сравнения первого вычислителя, а схема 5 - схема сравнения т-го вычислителя, по формуле

(аЛй,) V... (аДМ,

гдеа - содержимое регистра прерывания,

Ь - Ьт - содержимое регистров защиты вычислителей 1 - т.

Логическая операция «ИЛИ осуществляется в сборке 6. С выхода каждой схемы сравнения сигнал поступает в сборку 6 через вентили 7 -к 8, управляемые сипналами с и rf (вентиль 7 -вентиль первого вычислителя, вентиль 8 - вентиль /п-го вычислителя, сигнал с - сигнал разрещения прерывания с триггера запрета, разрещения прерывания отдельно по первому вычислителю, сигнал d - аналогичный сигнал по т-му вычислителю). Наличие сигнала на выходе сборки 6 говорит о том, что прерывание возможно, хотя бы по одному вычислителю.

Синхронизация сигнала на выходе сборки 6 и сигнала конца операции машин, допускающих прерывание, производится в блоке 9 синхронизации. Блок 9 управляется триггером .запрета - разрещения прерывания по всем .вычислителям 10.

В случае общего запрета прерывания сигнал Sустройства управления операциями вычислителей поступает, минуя устройство прерывания. В случае общего разрещения прерывания сигнал с выхода блока 9 подается на начальный триггер 11, управляющий блоком 12 поиска самой левой единицы в регистре прерывания.

Блок 12 состоит из генератора импульсов, дешифратора и счетчика кодов.

Генератор импульсов начинает подавать импульсы через счетчик в дещифратор при поступлении сигнала с начального триггера //в случае опрокидывания триггера сигналом с блока 9.

Поиск самой левой единицы в регистре прерывания осуществляется последовательно по разрядам, но параллельно по всем вычислителям при наличии разрещения по соответствующему вычислителю (сигналы си d).

кидывает триггер //, застопорив поступление импульсов от генератора блока 12 через дещифратор в схемы 4 и 5 и зафиксировав в счетчике кодов блока 12 номер разряда регистра прерывания 7, содержащего наиболее нриоритетный сигнал прерываиня, тем самым закончив работу на второй стадии, и, во-вторых, опрокидывает конечный триггер 14, унравляющий блоком 15 поиска самой левой единицы в

регистрах приоритета.

В регистрах приоритета 16 и 17 содержаться приоритеты обрабатываемых на вычислителях задач. Блок 15 содержит дещифратор и счетчик кодов и использует генератор импульсов из блока 12. В конце второй стадии конечный триггер 14 после поступления на него сигнала с выхода сборки 13 онрокидывается и открывает вентиль (на укрупненной блок-схеме устройства не показан), позводяющий импульсам с генератора блока 12 поступать в блок 15. Поиск самой левой единицы в регистрах приоритета 16 и 17 осущ.ествляется с помощью схем 18 и 19 (схема 18-схема сравнения для первого вычислителя, схема 19 - схема сравнения для /и-го вычислителя) последовательно по разрядам регистров приоритета 16 и 17, по параллельно для всех вычислителей.

При появлении сигнала на выходе любой из схем 5 и 19 сигнал проходит через сборку 20,

осуществляющую логическую операцию «РТЛИ, и опрокидывает конечный триггер 14, застопорив поступление импульсов от генератора блока 12 и зафиксировав в счетчике кодов наименьщий из приоритетов обрабатываемых на вычислителях задач. Одновременно один из сигналов ирерывания открывает вентиль 21 или 22 (вентиль 21 - вентиль первого вычислителя, вентиль 22 - вентиль т-го вычислителя), позволяющий содержимое одного

из счетчиков 23 или 24 команд вычислителей (счетчик 23 - счетчик команд первого вычислителя, счетчик 24 - счетчик команд т-го вычислителя) передать в регистр номера команд 25, тем самым запомнив номер команды, следующей за той, на которой произощло прерывание соответствующего вычислителя.

Через задержку по первому вычислителю 26 либо через задержку по т-му вычислителю 27 содержимое счетчика кодов блока 12 передается через вентиль первого вычислителя 28 либо через вентиль т-го вычислителя 29 в один из счетчиков 23 или 24, тем самым зафиксировав в них разряд регистра прерывания, указывающий на причину прерывания.

Необходимо отметить, что ради единообразия в устройстве прерывания и удобства программирования приоритеты в регистре прерывания/выбраны слева направо в порядке убывания, а в регистрах приоритета 16 и 17 - наоборот справа налево. Мы, схемы сравнения, вентили, триггеры, блоки поиска самой левой единицы, регистр номера команд, счетчики команд, регистр прерывания, регистры приоритетов, регистры защиты, блок синхронизации, отличающееся тем, что, с целью расширения функциональных возможностей, регистры приоритетов по числу вычислителей соединены с входами схем сравнения, вторые входы схем сравнения соединены с блоком поиска самой левой единицы в10 регистрах приоритетов, а к третьим входам подсоединены выходы триггеров запрета-разрещения, одни выходы схем сравнения подключены к вентилям между счетчиками команд и регистром номера команд,15 другие выходы через логическую схему соединены с триггером конца, выход которого соединен с блоком поиска самой левой 5 единицы в регистрах приоритетов, а второй вход триггера конца через логическую схему подключен к выходам cxeiM сравнения кодов защиты, входы которых соединены с дещнфратором блока поиска самой левой единицы в регистре прерывания, выходами регистра прерывания, регистров защиты, триггеров запрета - разрещения, вторые выходы схем сравнения кодов защиты через логическую схему, блок синхронизации и триггер начала соедийены с блоком поиска самой левой единицы в регистре прерывания, один выход которого подключен к входу блока поиска самой левой единицы в регистрах приоритетов, другие выходы через вентили подсоединены к счетчикам команд вычислителей, схема синхронизации соединена с триггером запрета - разрешения прерывания по всем вычислителям.

| название | год | авторы | номер документа |

|---|---|---|---|

| Автоматизированная система контроля радиоэлектронных устройств | 1989 |

|

SU1683038A1 |

| Устройство для прерывания программ | 1978 |

|

SU736101A1 |

| Устройство прерываний микропроцессорной системы | 1988 |

|

SU1621030A1 |

| Устройство многоуровневого прерывания | 1983 |

|

SU1104516A1 |

| УСТРОЙСТВО для АВТОМАТИЧЕСКОГО КОДИРОВАНИЯ | 1972 |

|

SU354409A1 |

| Устройство для сопряжения периферийных устройств с процессором и оперативной памятью | 1983 |

|

SU1156084A1 |

| Устройство для программного управления | 1985 |

|

SU1267362A2 |

| Устройство для сопряжения ЭВМ с общей магистралью | 1988 |

|

SU1532939A1 |

| Устройство многоуровневого прерывания | 1984 |

|

SU1174926A1 |

| УСТРОЙСТВО ДЛЯ ПРЕРЫВАНИЯ ПРОГРАММ | 1973 |

|

SU382089A1 |

Сигнал о

oncflau i б . -«-I д .n.a paзpeшmuf Сигтты} Г П/ ёустройолЩffceii система упраопенш операциями f ЙТГЛ От источника прерыбшЩ Память систе ь

Даты

1971-01-01—Публикация