Изобретение относится к эле ктронно-измсрительной технике и может быть применено для цифрового измерения частоты следования импульсов и длительности не1р,иодичеоких процессов.

В настоящее время существуют различные десятичные юересчетные устройства. Паибольщее распространение .получили пересчетные устройства, выполненные на основе четырех двоичных ячеек, соединенных между собой последовательно с внутренними обратными связям.и, обеспечивающими пересчет на десять. Скорость счета таких схем в основном ограничивается наличием обратных связей.

Построение быстродействующих десятичных пересчетных устройств основано на принципе деления входной частоты с помощью последовательно соединенных двоичных ячеек, не охваченных обратными связями, что ведет к усложнению конструкции.

Целью предлагаемого изобретения является упрощение конструкции и повышенпе на.(ежности устройства.

Сущность предлагаемого изобретения заключается в том, что измеряемая частота подвергается делению на 32 ири прохождении через пять последовательно соединенных двоичных ячеек, не охваченных обратной связью, и в дальнейщем поступает через умножитель на 2 на вход первой декады, а через умножитель на 3 - на выход устройства. Кроме того, остаток, который мог остаться в делителе на 32, переносится в декаду при помощи схемы опроса, благодаря чему восстанавливается коэффициент 1пе ресчета устройства до десяти.

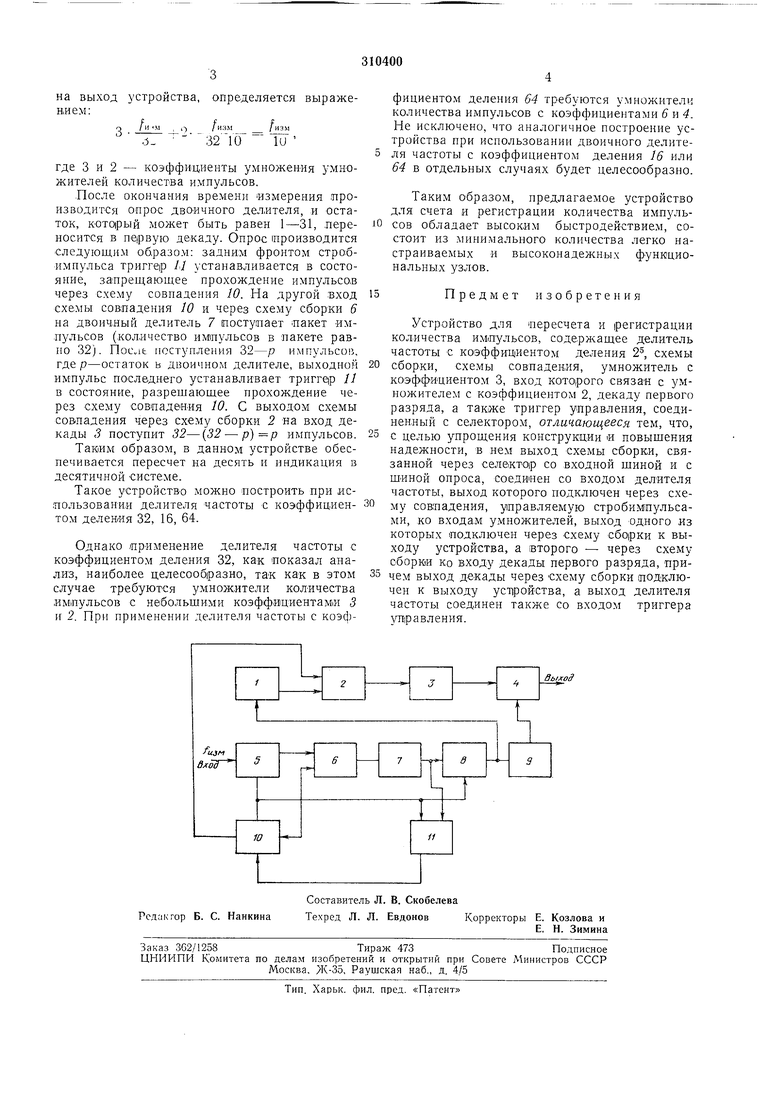

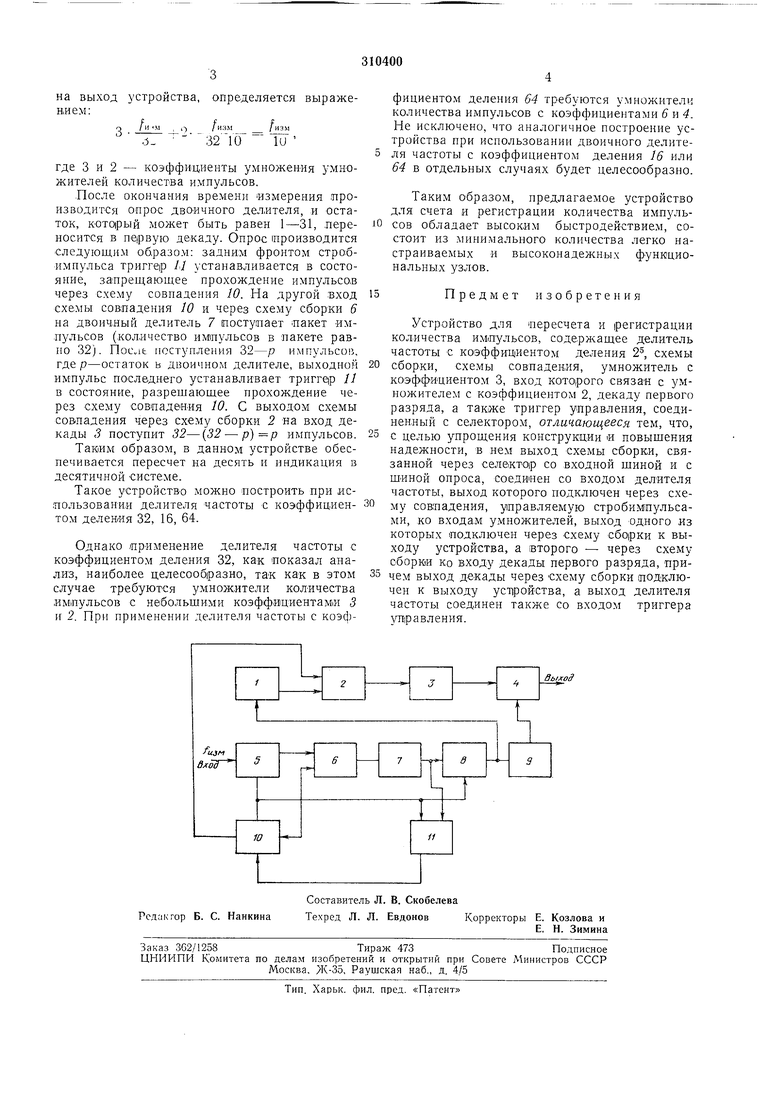

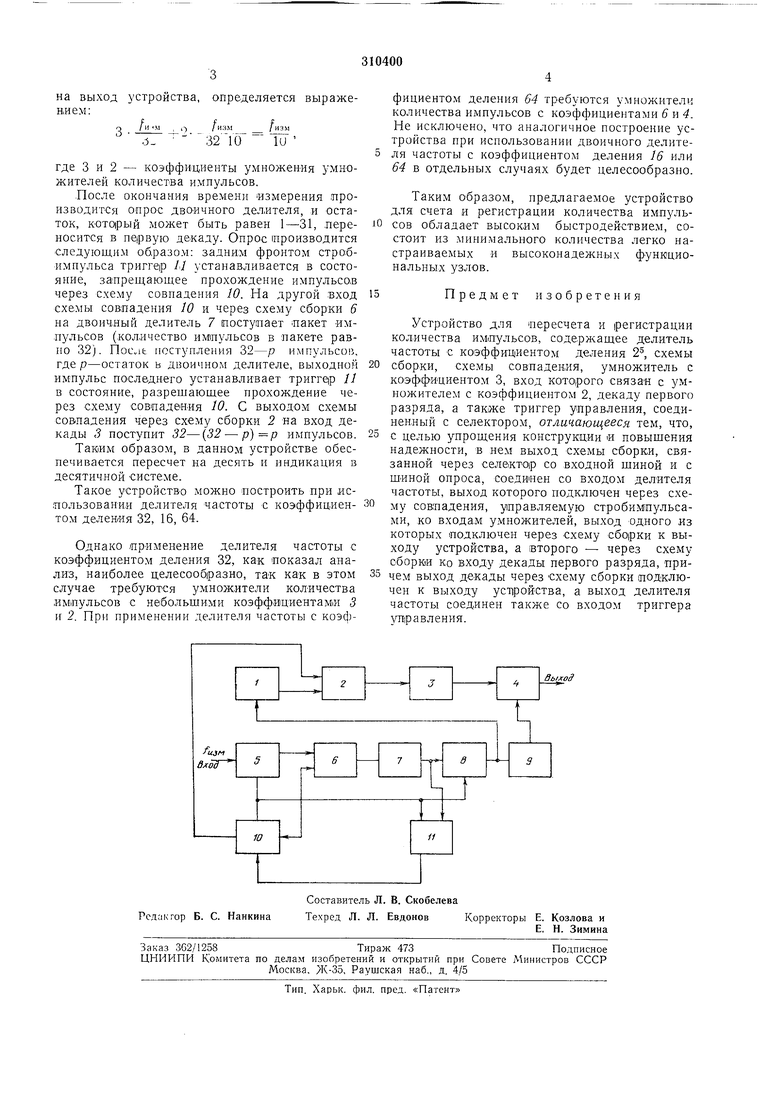

На чертеже представлена блок-схема предлагаемого устройства для пересчета ,и регистрации количества импульсов. Устройство состоит из умножителя на два /, схемы сборки 2, декады 3 первого разряда, схемы сборки 4, входного селектора 5, схемы сборки 6, двоичного делителя частоты 7, схемы совпадения 8, умножителя на три 9, схемы совпа5дения 10, триггера //.

Устройство работает следующим образом. Измеряемая частота f в течение времени измерения поступает через селектор 5 и

0 схему сборки 6 на вход двоичного делителя 7. С выхода делителя 7 частота изм поступает

Тк

через схему совпаден.ия 8 на умножитель на три 9 и через схему сборки 4 - на )д устройства. С выхода схемы совпадения 8 частота /нзм также поступает на умножитель на

зТ

два / и через схему сборк 2 на вход декады 3 первого разряда, с выхода которой поступает через схему сборки 4 на выход устройства. Количество импульсов, которое поступает

| название | год | авторы | номер документа |

|---|---|---|---|

| ВИБЛИОТЕКД J | 1971 |

|

SU299030A1 |

| ДЕСЯТИЧНОЕ ПЕРЕСЧЕТНОЕ УСТРОЙСТВО | 1969 |

|

SU241127A1 |

| УПРАВЛЯЕМЫЙ ДЕКАДНЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ С ПЕРЕМЕННЫМ КОЭФФИЦИЕНТОМ ДЕЛЕНИЯ | 1970 |

|

SU270354A1 |

| ДЕСЯТИЧНОЕ ПЕРЕСЧЕТНОЕ УСТРОЙСТВО | 1972 |

|

SU341165A1 |

| ДЕСЯТИЧНОЕ ПЕРЕСЧЕТНОЕ УСТРОЙСТВО | 1972 |

|

SU341166A1 |

| ЭЛЕКТРОННОСЧЕТНЫЙ ЧАСТОТОМЕР | 1972 |

|

SU340979A1 |

| ПЕРЕСЧЕТНОЕ УСТРОЙСТВО | 1973 |

|

SU383085A1 |

| ДЕСЯТИЧНОЕ ПЕРЕСЧЕТНОЕ УСТРОЙСТВО | 1969 |

|

SU233308A1 |

| УСТРОЙСТВО для УМНОЖЕНИЯ ЧАСТОТЫ | 1970 |

|

SU264457A1 |

| Цифровой частотомер | 1973 |

|

SU481851A1 |

Даты

1971-01-01—Публикация