Данное изобретение относится к области аналоговой вычислительной техники.

Известны аналоговые регистры сдвига, содержащие включенные в параллельные ветви последовательно соединенные ячейки конденсаторной памяти, генератор тактовой частоты и выходной интерполирующий низкочастотный фильтр. Однако эти устройства недостаточно надежны.

Предлагаемое устройство отличается от известных тем, что содержит пересчетный делитель частоты на счетчике с дещифраторами и формирующими усилителями, общее количество которых соответствует числу параллельных ветвей регистра, а также восстанавливающие цепи с ключами, причем вход счетчика пересчетной схемы соединен с выходом генератора тактовой частоты, выходы ее формирующих усилителей подключены к тактовым входам ячеек конденсаторной памяти, входы соответствующих цепей присоединены к выходам предпоследних ячеек контурной памяти каждой из параллельных ветвей регистра, а ключи восстанавливающих целей включены между выходами последних ячеек конденсаторной памяти и входом интерполирующего Низкочастотного фильтра, к которому подключен общий для всех ветвей запоминающий конденсатор. Это позволило повысить надежность устройства.

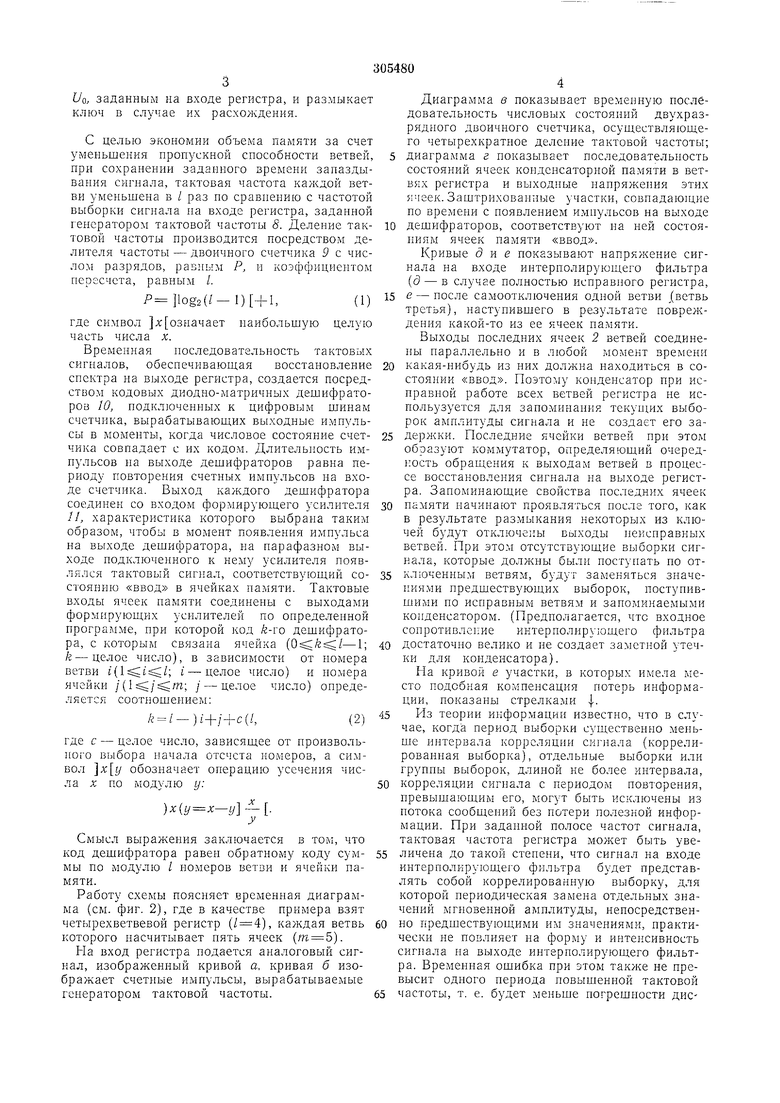

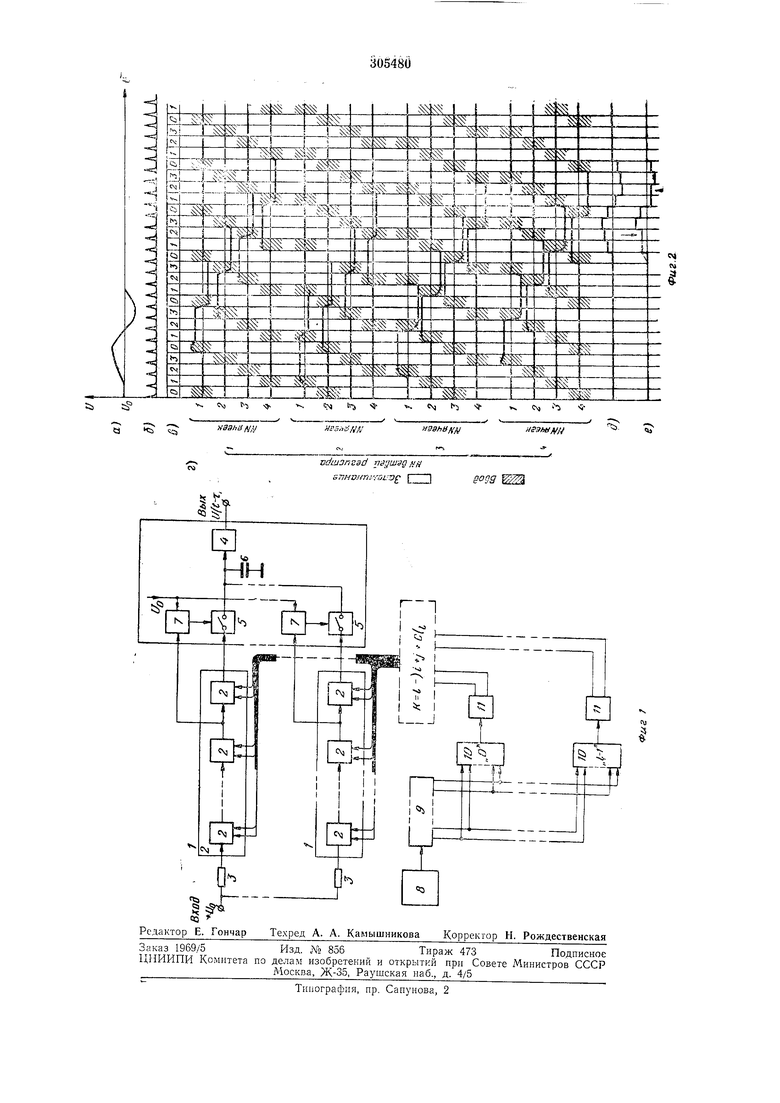

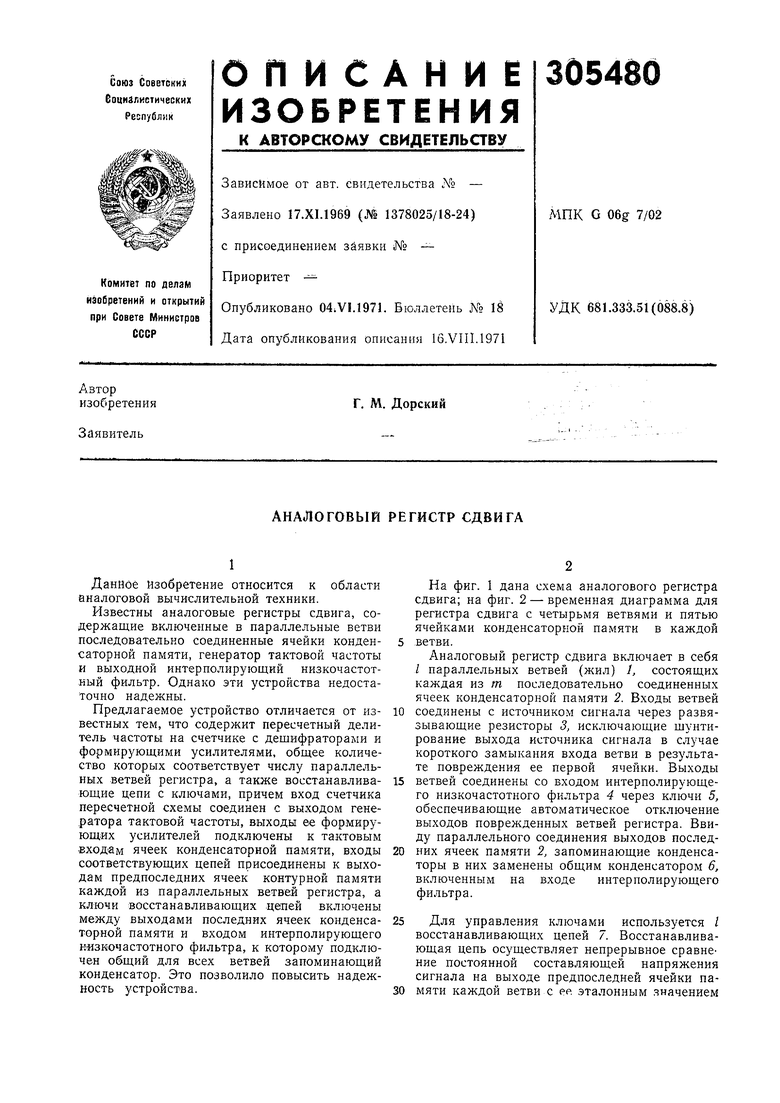

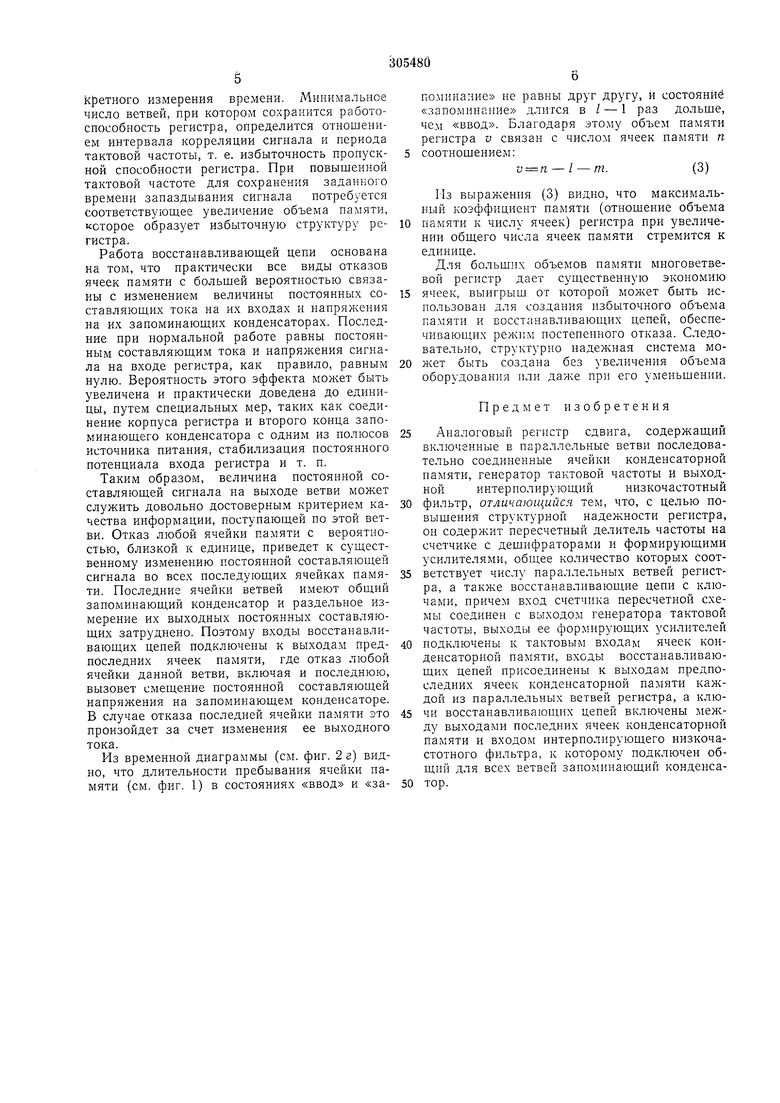

На фиг. 1 дана схема аналогового регистра сдвига; на фиг. 2 - временная диаграмма для регистра сдвига с четырьмя ветвями и пятью ячейками конденсаторной памяти в каждой .ветви.

Аналоговый регистр сдвига включает в себя / параллельных ветвей (жил) /, состоящих каждая из т последовательно соединенных ячеек конденсаторной памяти 2. Входы ветвей соединены с источником сигнала через развязывающие резисторы 3, исключающие шунтирование выхода источника сигнала в случае короткого замыкания входа ветви в результате повреждения ее первой ячейки. Выходы ветвей соединены со входом интерполирующего низкочастотного фильтра 4 через ключи 5, обеспечивающие автоматическое отключение выходов поврежденных ветвей регистра. Ввиду параллельного соединения выходов последних ячеек памяти 2, запоминающие конденсаторы в них заменены общим конденсатором 6, включенным на входе интерполирующего фильтра.

Для управления ключами

используется / Восстанавливавосстанавливающих цепей 7. ющая цепь осуществляет непрерывное сравне ние постоянной составляющей напряжения сигнала на выходе предпоследней ячейки памяти каждой ветви с ее эталонным .значением UQ, заданным на входе регистра, и размыкает ключ в случае их расхождения. С целью экономии объема памяти за счет уменьшения пропускной способности ветвей, при сохранении заданного времени запаздывания сигнала, тактовая частота каждой ветвн уменьшена в / раз по сравнению с частотой выборки сигнала па входе регистра, заданной генератором тактовой частоты S. Деление тактовой частоты производится посредством делителя частоты - двоичного счетчика 9 с числом разрядов, равным Р, н коэффициентом пересчета, равным /. log2(/-)+,(1) где символ л: означает наибольшую целую часть числа х. Временная нocлeдoвaтev ьнocть тактовых сигналов, обеснечивающая восстановление спектра на выходе регистра, создается посредством кодовых диодно-матричных дешифраторов 10, подключенных к цифровым шинам счетчика, Бырабатываюш,их выходные импульсы в моменты, когда числовое состояние счетчика совпадает с их кодом. Длительность импульсов на выходе дешифраторов равна периоду повторения счетных импульсов на входе счетчика. Выход каждого дешифратора соединен со входом формируюшего усилителя и, характеристика которого выбрана таким образом, чтобы в момент появления импульса на выходе дешифратора, на парафазном выходе подключенного к нему усилителя появлялся тактовый сигнал, соответствующий состоянию «ввод в ячейках памяти. Тактовые входы ячеек памяти соединены с выходами формирующих усилителей по определеиной программе, при которой код /е-го дешифратора, с которым связана ячейка ( k-целое число), в зависимости от номера ветви i( i - целое число) и ио.мера ячейки /( / - целое число) определяется соотношением: /e /-)i+/+c(/. где с - целое число, зависящее от произвольного выбора начала отсчета номеров, а символ обозначает операцию усечения числа X по модулю у: )х( - . Смысл выраження заключается в том, что код дешифратора равен обратному коду суммы но модулю / номеров ветви и ячейки памяти. Работу схемы поясняет временная диаграмма (см. фиг. 2), где в качестве примера взят четырехветвевой регистр (/ 4), каждая ветвь которого насчитывает пять ячеек (т 5). Диаграмма в показывает временную последовательность числовых состояний двухразрядного двоичного счетчика, осуществляющего четырехкратное деление тактовой частоты; диаграмма г показывает последовательность состояний ячеек конденсаторной памяти в ветвях регистра и выходные напряжения этих ячеек. Заштрихованные участки, совпадаюн ие по времени с появлением импульсов на выходе дешифраторов, соответствуют па ней состояниям ячеек памяти «ввод. Кривые (3 и е показывают напряжение сигнала на входе интерполируюицего фильтра (д - в случае полностью исправного регистра, е - после самоотключения одной ветви /ветвь третья), настунившего в результате повреждения какой-то из ее ячеек памяти. Выходы последних ячеек 2 ветвей соединены параллельно и в любой момент времени какая-нибудь из них должна находиться в состоянии «ввод. Поэтому конденсатор при исправной работе всех ветвей регистра не испольузуется для запоминания текуншх выборок амплитуды сигнала и не создает его задержки. Последние ячейки ветвей при этом образуют коммутатор, определяющий очередность обращения к выходам ветвей в процессе восстановления сигнала на выходе регистра. Запоминающие свойства последних ячеек памяти начинают проявляться после того, как в результате размыкания некоторых из ключей будут отключены выходы неисправных ветвей. При этом отсутствующие выборки сигнала, которые должны были ноступать по отключенным ветвям, будут заменяться значениями предществующих выборок, поступившими по исправным ветвям и запоминаемыми конденсатором. (Предполагается, что входное сопротивление интерполирующего фильтра достаточпо велико и не создает заметной утечки для конденсатора). На кривой е участки, в которых имела место подобная компенсация потерь информации, показаны стрелками |. Из теории информации известно, что в случае, когда период выборки существенно меньше интервала корреляции сигнала (коррелированная выборка), отдельные выборки или группы выборок, длиной не более интервала, корреляции сигнала с периодом повторения, превышающим его, могут быть исключены из потока сообщений без потери полезной информации. При заданной полосе частот сигнала, тактовая частота регистра может быть увеличена до такой степени, что сигнал на входе интерполирующего фильтра будет представлять собой коррелированную выборку, для которой периодическая замена отдельных значений мгновенной амплитуды, непосредственно предшествующими им значениями, практиески не повлияет на форму и интенсивность игнала на выходе интерполирующего фильта. Временная ощибка при этом также не преысит одного периода повышенной тактовой астоты, т. е. будет меньше погрешпости дискретного измерения времени. Минимальное число ветвей, при котором сохранится работосиособность регистра, определится отношением интервала корреляции сигнала и периода тактовой частоты, т. е. избыточность пропускной способности регистра. При повышенной тактовой частоте для сохранения заданного времени запаздывания сигнала потребуется соответствуюш,ее увеличение объема памяти, которое образует избыточную структуру регистра.

Работа восстанавливаюш,ей цепи основана на том, что практически все виды отказов ячеек памяти с большей вероятностью связаны с изменением величины постоянных составляюших тока на их входах и напряжения на их запоминающих конденсаторах. Последние при нормальной работе равны постоянным составляюш,им тока и напряжения сигнала на входе регистра, как правило, равным нулю. Вероятность этого эффекта может быть увеличена и практически доведена до единицы, путем специальных мер, таких как соединение корпуса регистра и второго конца запоминающего конденсатора с одним из полюсов источника питания, стабилизация постоянного потенциала входа регистра и т. п.

Таким образом, величина постоянной составляющей сигнала на выходе ветви может служить довольно достоверным критерием качества информации, поступающей по этой ветви. Отказ любой ячейки памяти с вероятностью, близкой к единице,, приведет к существенному изменению постоянной составляющей сигнала во всех последующих ячейках памяти. Последние ячейки ветвей имеют общий запомипающий конденсатор и раздельное измерение их выходных постоянных составляющих затруднено. Поэтому входы восстанавливающих цепей подключены к выходам предпоследних ячеек памяти, где отказ любой ячейки данной ветви, включая и последнюю, вызовет смещение постоянной составляющей напряжения на запоминающем конденсаторе. В случае отказа последней ячейки памяти это произойдет за счет изменения ее выходного тока.

Из временной диаграммы (см. фиг. 2 г) видно, что длительности пребывания ячейки памяти (см. фиг. 1) в состояниях «ввод и «запоминание не равны друг другу, и состояние «запоминание длится в / - 1 раз дольше, че.м «ввод. Благодаря этому объем памяти регистра и связан с числом ячеек памяти п соотношением:

v n - l - m.(3)

Из выражения (3) видно, что максимальный коэффициент памяти (отношение объема

памяти к числу ячеек) регистра при увеличении общего числа ячеек памяти стремится к единице.

Для больших объемов памяти многоветвевой регистр дает существенную экономию

ячеек, выигрыш от которой мож.ет быть использован для создания избыточного объема памяти и восстанавливающих цепей, обеспечивающих режим постепенного отказа. Следовательно, структурно надежная система может быть создана без увеличения объема оборудования пли даже npii его уменьщении.

Предмет изобретения

Аналоговый регистр сдвига, содержащий включенные в параллельные ветви последовательно соединенные ячейки конденсаторной памяти, генератор тактовой частоты и выходной интерполирующий низкочастотный

фильтр, отличающийся тем, что, с целью повышения структурной надежности регистра, он содерлчит пересчетный делитель частоты на счетчике с дешифраторами и формирующими усилителями, общее количество которых соответствует числу параллельных ветвей регистра, а также восстанавлнвающие цепи с ключами, причем вход счетчика пересчетной схемы соединен с вы.ходом генератора тактовой частоты, выходы ее формирующих усилителей

подключены к тактовым входам ячеек конденсаторной памяти, входы восстанавливающих цепей присоединены к выходам предпоследних ячеек конденсаторной памяти каждой из параллельных ветвей регистра, а ключи восстанавливающпх цепей включены мелсду выходами последних ячеек конденсаторной памяти и входом интерполирующего низкочастотного фильтра, к которому подключен общий для всех ветвей запоминающий конденсатор. Н6фф:Ы fetfTTsksist(КТ Ч 7-i-i тг Z .ТГ.1 ilSiJ Hfeh-h- %t 1 .izz:ripi i4 fe i rt i }; it-i4 - .. es)h4h

,V//

иЗЗЛс /V,{/

(3

vdijj3ns3d rtsjiuyg ftfl

5ПНО.ЧШ-ГйиГ} I 1 i...,.

iisahUf/H

3ahUK/j

вода ш: CM 5

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальный коммутатор | 1979 |

|

SU809291A1 |

| Ячейка памяти для регистраСдВигА | 1979 |

|

SU809384A1 |

| Стенд для измерения частотных характеристик свойств веществ | 1982 |

|

SU1114981A1 |

| СУММИРУЮЩАЯ ЛИНИЯ ЗАДЕРЖКИ | 1972 |

|

SU420095A1 |

| УСТРОЙСТВО для ОБРАБОТКИ ЗАПИСЕЙ НЕПРЕРЫВНЫХ . СЕЙСМИЧЕСКИХ КОЛЕБАНИЙ | 1971 |

|

SU312224A1 |

| АНАЛОГОВЫЙ РЕГИСТР СДВИГА | 1970 |

|

SU275533A1 |

| Устройство для контроля высоковольтного тиристорного вентиля | 1983 |

|

SU1153374A1 |

| Устройство для контроля качества изделий | 1983 |

|

SU1171707A1 |

| ИМПУЛЬСНЫЙ КОДОВЫЙ ПРЕОБРАЗОВАТЕЛЬ | 2004 |

|

RU2248607C1 |

| Пересчетное устройство | 1982 |

|

SU1046935A1 |

Даты

1971-01-01—Публикация