Изобретение относится к области вычислительной техники и предназначено для использования в системах памяти с циклическим магнитным носителем (барабанами или дисками).

Известные усилители воспроизведения для запоминающих устройств с циклическим магнитным носителем, содержащие двоичный счетчик, регистры, формирующие и логические схемы и линию задержки, используют относительно большой объем дорогостоящей аппара Р 1Отличием описываемого устройства является то, что выход задающего генератора, содержащего схему «И - НЕ, линию задержки и схему согласования, подключен к объединенным входам двоичного счетчика и схемы совпадения, другой вход которой соединен с выходом схемы формирования пачки импульсов, записанных перед массивом информации, выход схемы совпадения подключен к объединенным входам блокирующего регистра и набора схем совпадения, выходы которых соединены со входами набора регистров, а их вторые входы объединены со входами набора схем сравнения и соединены с выходами двоичного счетчика, а другие входы набора схем сравнения подключены к выходам набора регистров.

Это позволяет упростить устройство и сократить объем используемой аппаратуры.

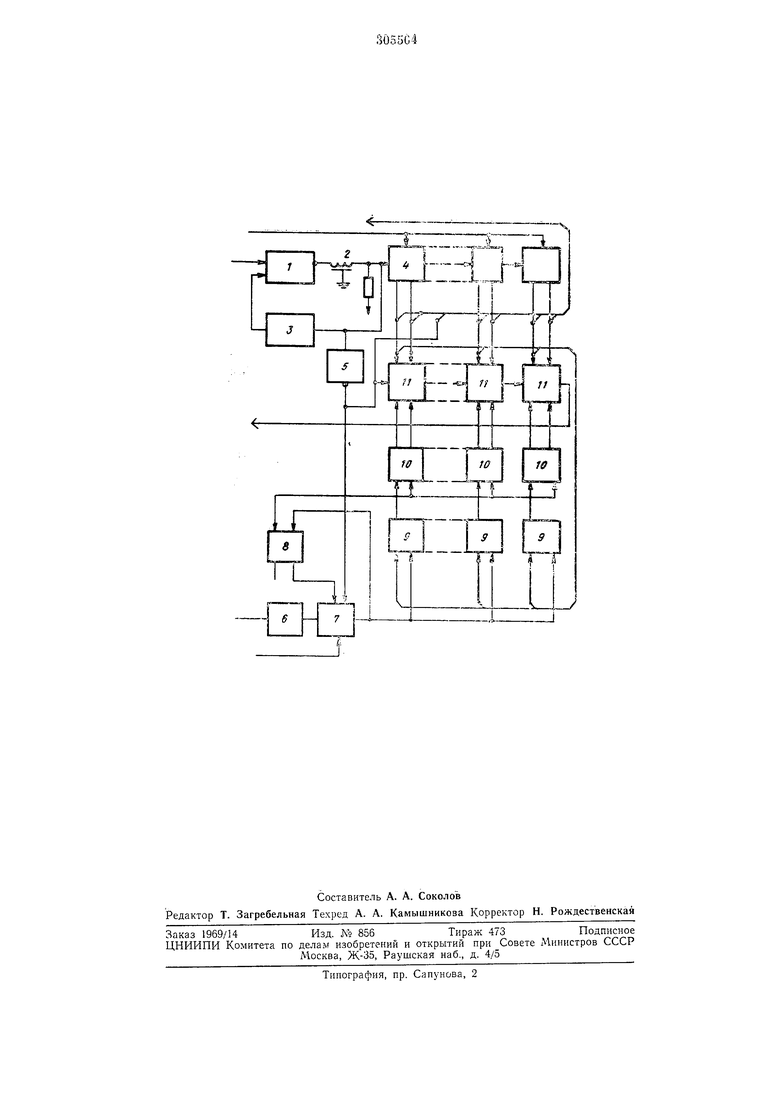

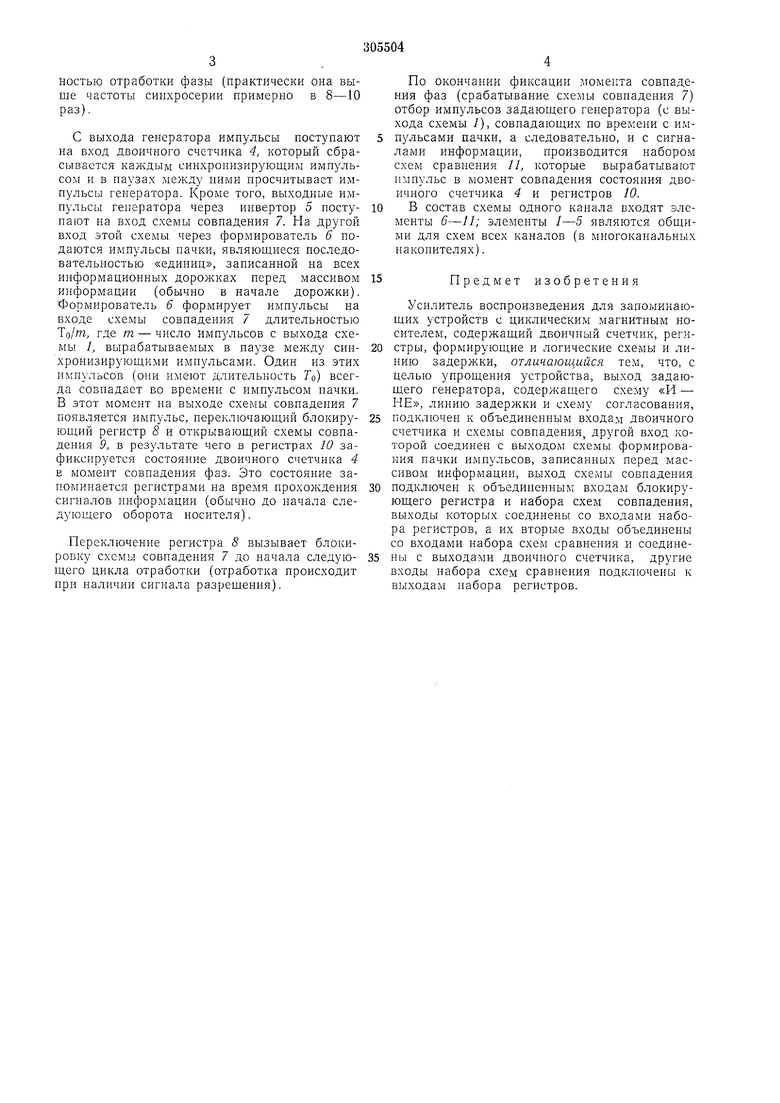

На чертеже показана функциональная схема устройства.

Оно состоит из быстродействующей логической схемы «И - НЕ 1, которая совместно с линией задержки 2 и элементом согласования 3 образует задающий генератор, двоичного счетчика 4, инвертора 5, формирователя

импульсов 6, схемы совпадения 7, с помощью которой фиксируется момент совпадения фаз, блокирующего регистра 8, блока набора схем совпадения 9, которые управляют входами набора регистров 10 и набора схем сравнения //.

Устройство работает следующим образом. Па один из входов логической схемы «И - НЕ 1 поступают синхронизирующие импульсы, стабилизированные по длительности. Во

время действия этих импульсов, которые поступают в виде сигналов запрета, логическая схема / закрыта; в паузе между импульсами вследствие действия обратной связи через линию задержки 2 и элемент согласования 3 логическая схема переходит в режим автоколебаний, вырабатывая импульсы с частотой /

: - , где /3 - время задержки линии.

ностью отработки фазы (практически она выше частоты сиихросерии примерно в 8-10 раз).

С выхода генератора импульсы поступают на вход двоичного счетчика 4, который сбрасывается каждым синхронизирующим импульсом и в паузах между пими просчитывает импульсы генератора. Кроме того, выходные импульсы генератора через инвертор 5 поступают на вход схемы совпадения 7. На другой вход этой схемы через формирователь 6 подаются импульсы пачки, являющиеся последовательностью «единиц, записанной на всех информационных дорожках перед массивом информации (обычно в начале дорожки). Формирователь 6 формирует импульсы на входе схемы совпадения 7 длительностью То/т, где т - число импульсов с выхода схемы 1, вырабатываемых в паузе между сипхронизирующими импульсами. Один из этих импульсов (они имеют длительность Го) всегда совпадает во времени с импульсом пачки. В этот момент на выходе схемы совпадения 7 появляется импульс, переключающий блокируюп ий регистр 8 и открывающий схемы совпадения 9, в результате чего в регистрах 10 зафиксируется состояние двоичного счетчика 4 в момепт совпадения фаз. Это состояние запоминается регистрами на время прохождения сигналов информации (обычно до начала следующего оборота носителя).

Переключение регистра 8 вызывает блокировку схемы совпадения 7 до начала следующего цикла отработки (отработка происходит при наличии сигнала разрещепия).

По окончании фиксации .дтомепта совпадения фаз (срабатывание схемы совпадения 7) отбор импульсов задающего генератора (с выхода схемы /), совпадающих по времени с импульсами пачки, а следовательно, и с сигналами информации, производится набором схем сравнения 11, которые вырабатывают имнульс в момент совпадения состояния двоичного счетчика 4 и регистров 10. В состав схемы одного канала входят элементы 6-11; элементы /-5 являются общими для схем всех каналов (в многоканальных накопителях).

Предмет изобретения

Усилитель воспроизведения для запоминающих устройств с циклическим магнитным носителем, содержащий двоичный счетчик, регистры, формирующие и логические схемы и линию задержки, отличающийся тем, что, с целью упрощения устройства, выход задающего генератора, содержащего схему «И - НЕ, линию задержки и схему согласования,

подключен к объединенным входам двоичного счетчика и схемы совпадения, другой вход которой соединен с выходом схемы формирования пачки импульсов, записанных перед массивом информации, выход схемы совпадения

подключен к объединенным входам блокирующего регистра и набора схем совпадения, выходы которых соединены со входами набора регистров, а их вторые входы объединены со входами набора схем сравнения и соединены с выходами двоичного счетчика, другие входы набора схем сравнения подключены к выходам пабора регистров.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля логических узлов | 1980 |

|

SU991430A1 |

| ПРИЕМО-ПЕРЕДАТЧИК ДЛЯ ПОЛУДУПЛЕКСНОЙ СВЯЗИ | 1993 |

|

RU2065254C1 |

| СПОСОБ КОДИРОВАНИЯ ЦИФРОВЫХ СИГНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1999 |

|

RU2168270C2 |

| Устройство для контроля знаний обучаемых | 1990 |

|

SU1758658A1 |

| Цифровой измеритель частоты заполнения радиоимпульсов | 1982 |

|

SU1161892A1 |

| Устройство для формирования тестовой последовательности | 1984 |

|

SU1218389A1 |

| Многоканальное устройство тестового контроля логических узлов | 1988 |

|

SU1564623A1 |

| УСТРОЙСТВО для ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 1971 |

|

SU321809A1 |

| Устройство для передачи и приема информации | 1987 |

|

SU1437894A1 |

| Логическое запоминающее устройтво | 1979 |

|

SU858104A1 |

Даты

1971-01-01—Публикация