Изо.бретение относится к области ЕЫЧИСЛИтелькой техники, в частности к устрскотвам уиравлеиия обращениями к памяти каналов и центрального вычислителя.

Известны устройства для выборки блоков па.мяти, содержащие триггеры, счетчики, вентили, сумматор и регистр з аиоминания.

Недостаток известных схем состоип в том, что высокоскоростной селекторный синхронный канал при совместной, работе с быстро,;ей1ству1ощей памятью через сонряжекия канала с памятью не может использовать ее высокую производительность и как следствие имеет иолноразрядные устройства буферизации данных.

Пред.юженное устройство отличается от известных тем, что в нем триггер предварительной выборки блоков памяти соедийен с щиной нредваритешьной выборки, с вентилем выдачи интервалов в сумматор и с сумматором, триггер предварительного чтения данных из памяти соединен с устройством управления обращением к памяти и с сумматором, триггер «настройки устройства для обмена с каналом подключен к устройству управлекия обраще 1ием к памяти и к вентилю выдачи интервалов, сумматор соединен с регистром запо.ИТ1ания периода между требованиями от капала, со счетчиком числа блокируемых блоков памяти и с устройством упразлеки.я обращение к памяти, вентиль выдачи интервалов сседш ен с сумматором и с устройством управления обращением к памяти, счетчик числа блокируемых блоков памяти иодключен к устройству управления обращением к намятп, регистр запоминания перг1ода между требованиями от канала соединен с сумматором, счетчик адреса данных канала соединен с триггером предварительного чтения и с устройством управления обращения к памяти.

Это позволяет увеличить пропускную способность высокоскоростного селекторного канала, более эффективно использовать производительность памяти и. уменьшить объем оборудования для обмена информацией между памятью и высокоскоростными внешними устройствами.

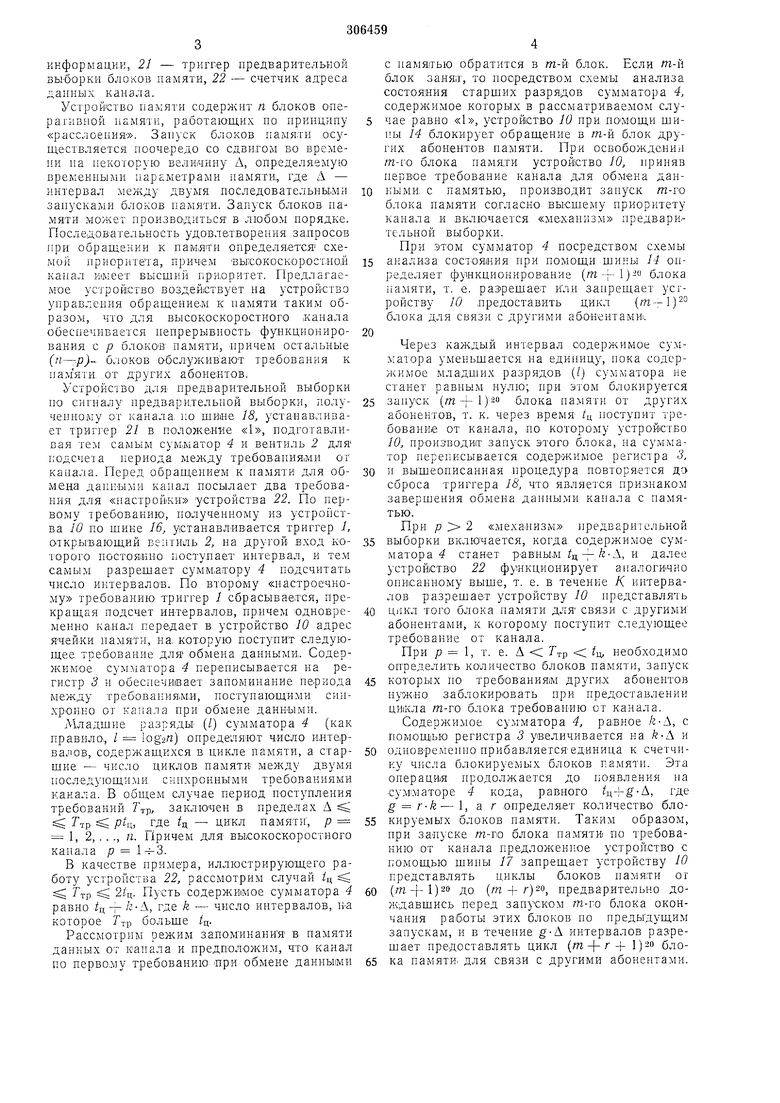

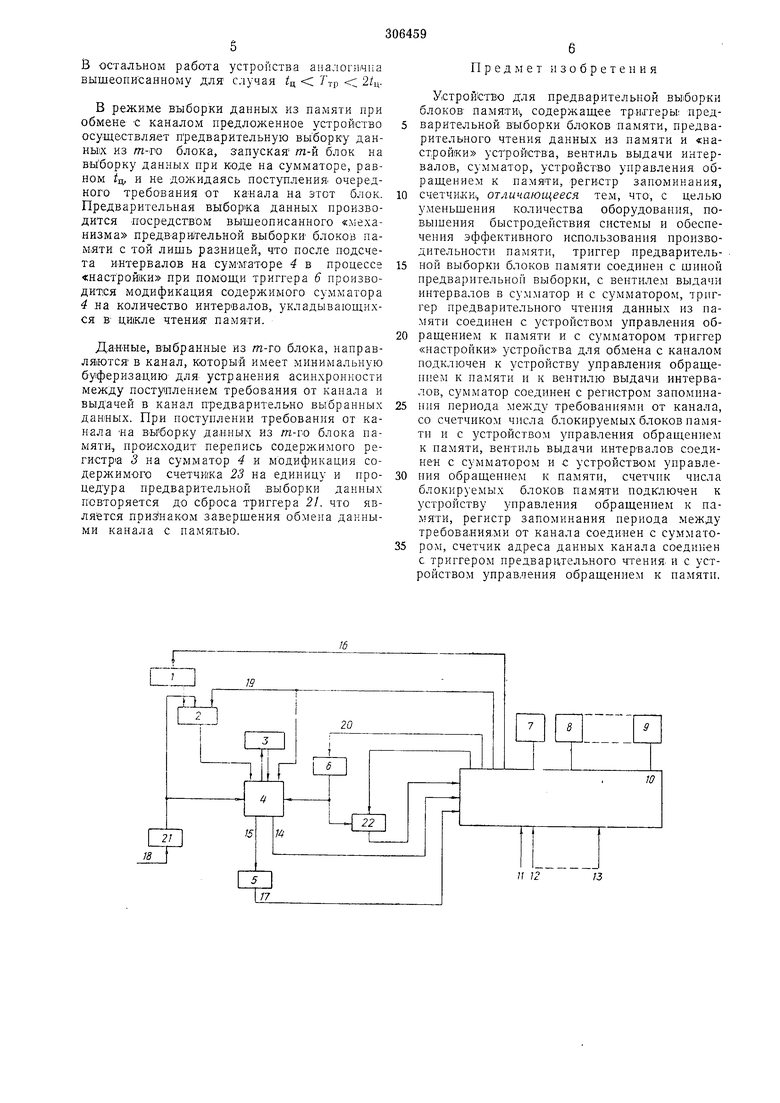

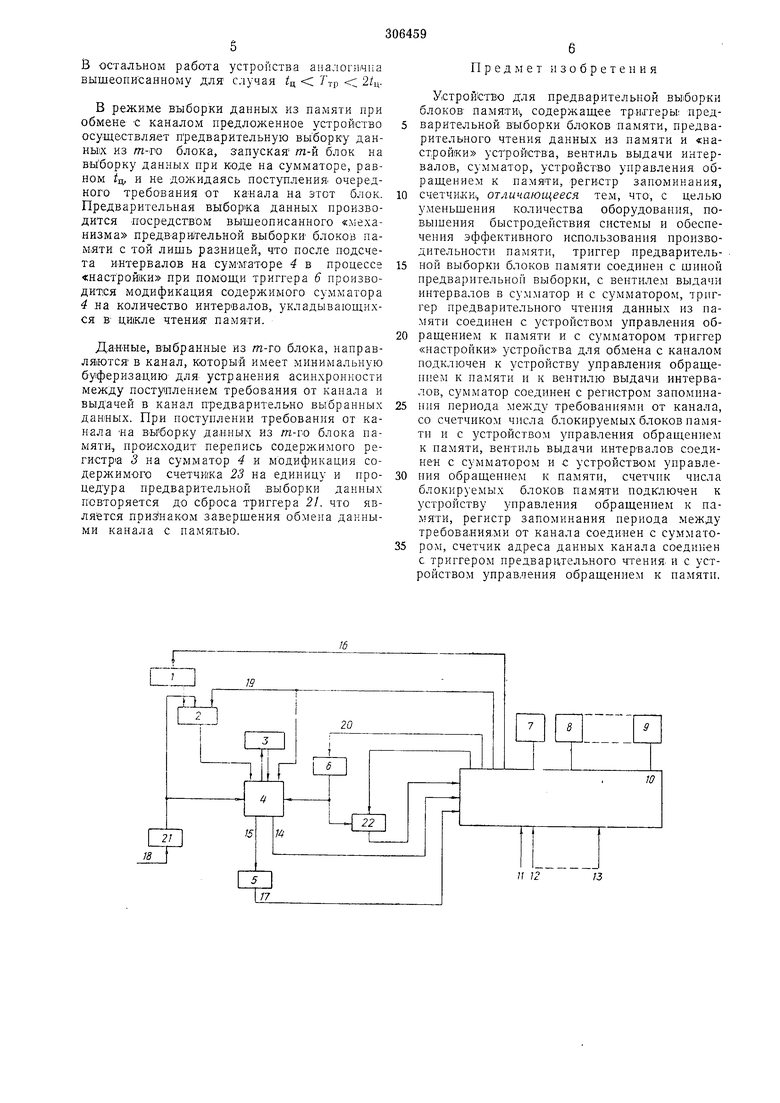

На чертеже представлена схема предлагаемого устройства, где / - триггер «настройки для обмена с каналом, 2 - вентиль выдачи интервалов в сумматор, 3 - регистр запоминания периода между требова.ниями от канччла, 4 - сумматор со схемой анализа состояния, 5 - счетчик числа блокируемых блоков памяти, 6 - триггер г.редварительпого чтения данных из памяти для ожидаемого требоваиия ка.нала, 7-9-(1, 2,...., п) блоки памяти, 10 - устройство управле1П1я обращением к памяти, )/-20-щины передачи

информации, 21 - триггер предварительной зЫборки блоков памяти, 22 - счетчик адреса даипых капала.

Устройство памяти содержит п блоков операгивной памяти, работающих по принципу «расслоения. Запуск блоков памяти осуществляется поочередо со сдвигом во времепи па шкоторую величину А, определяемую временны.Д1И параметрами памяти,, где Л - интервал между двумя последовательпььми запусками блоков памяти. Запуск блоков памяти может производиться в любо.м порядке. Последовательпость удовлетворения зацросов прц обращении к памяти определяется схемой приоритета, причем вы:сокоскорост,но.й канал ицмеет высший нраоритет. Предлагаемое устройство воздействует на устройство управления обращением к намяти таким образом, что для высокоскоростного |Канала обеснечивается непрерывность функционирования с р блокоБ памяти, причем остальные (п-р) блоков абслужнвают требовапия к памяти от других абопейтов.

Устройство ДЛЯ нредварнтельно.й выборки по сигналу предварительной выборки, получеппому от канала по шиие 18, устанавливает триггер 21 в ноложе«ие «1, подготавливая тем самым сум.матор 4 и вентиль 2 для ьодсчеча периода между требовапиЯ(МП от капала. Перед обращением к памяти для обмена дапными канал посылает два требования для «настройКИ устройства 22. По первому требованию , получеппому из устройства 10 по шине 16, устапавЛНВается триггер L открывающий вентиль 2, на другой вход которого постоянно поступает интервал, и тем самы.м разрешает сумм.атору 4 нодсчитать число интервалов. По второму «настроечному требованию триггер 1 сбрасывастся, прекращая подсчет интервалов, причем одновременно канал передает в устройство 10 адрес ячейКИ памяти, па. которую поступит следующее требовапие для обмена данными,. Содержимое сумматора 4 неренисывается на регистр 3 и обеспечивает зано.минание периода между требОванияАШ, поступающими синхронно от канала при обмене данными.

Младшие разрядьг (/) сумматора 4 (как правило,, / iog2«) определяют число n.HTeipвалов, содержащихся в цикле намяти, а старшие - число циклов памяти между двумя последующи ми синхронными требованиями канала. В общем случае нериод поступления требований , заключен в пределах Д Тгр р1ц, где ц - цикл памяти , р 1, 2, . . ., п. Причем для высокоскоростного канала р 1 .

В качестве примера, иллюстрирующего работу устройства 22, рассмотрим случай /ц Ттр 2/ц. Пусть содержи1мое сумматора 4 равно ц-г --, где k - число интервалов, на которое Гтр больше /ц.

Рассмотрим режим запоминания в намяти данных от канала и предположим, что канал по перво.му требованию при обмене данными

с намжтью обратится в т-й блок. Если т-й блок занят, то посредством схемъ анализа состояния старших разрядов сумматора 4, содержимое которых в рассматриваемом случае равно «1, устройство 10 при номощи шипы 14 блокирует обращение в т-и блок других абонентов памяти. При освобождении т-го блока памяти устройство 10, приняв нервое требование канала для обмена данными, с намятью, производит зануск т-го блока памяти согласно высшему приоритету кана.та и включается «механизм нредвари-тельной выборки.

При этом сумматор 4 посредством схемы

анализа состояния при помощи шины 14 определяет функционирование (/п-;-)- блока памяти, т. е. раз-решает Или занрешает усгройству 10 ,нредоставить цикл (т-)° блока для связи с другими абОнентами.

Через каж,дый интервал содержимое сумматора уменьшается, на единицу, пока содержимое младших разрядов (/) сумматора не станет равны.м нулю; нри этом блокируется

зануск (от-ь 1)2о блока памяти от других абОнентов, т. к. через время- /ц поступит требование от канала, НО которому устройство 10, производит зануск этого блока, на сумматор перег1исывается содержимое регистра 3,

и вышеОПИсанная нроцедура новторяется да сброса триггера 18, что является признаком завершения обмена данными канала с намятью.

При /3 2 «механизм предварительной

выборки включается, когда содержимое сумматора 4 станет р-авныл , и далее устройство 22 функционирует аналогично описанному выше, т. е. в течение /С интервалов разрешает устройству 10 нредставлять

цикл того блока памяти для связи с другими абонентами, к которому ностунит следующее требование от канала.

При / 1, т. е. Д Г

ц, необходимо

тр определить колнчество блоков памяти, запуск

которых по требования1М других абонентов нужно заблокировать нри нреДОставлении ци1кла т-го блока требоваНИЮ от канала.

Содержимое сулгматора 4, равное /е-Д, с помощ1ью регистра 3 увеличивается на /г-Д и

одновременно нрибавляетсяединица к счетчику числа блокируемых блоков намяти. Эта онерацйя нродолжается до появления на cyMiMaTope 4 кода, равного , где g r-k- I, а г ,онределяет количество блокируемых блоков иамяти. Таким обраЗОМ, нри запуске т-го блока намяти: по требованию от канала предложенное устройство с помощью щины 17 запрещает устройству 10 нредставлять циклы блоков памяти ог

(/п-4-1)2| до (т-f г)2о, предварительно доЖдавшись перед зануском т-го блока оконча,ния работы этих блоков по предыдущим запускам, и в течение g-Д интервалов разрешает иредоставлять цикл ( + 1)2о бло

| название | год | авторы | номер документа |

|---|---|---|---|

| Система ввода-вывода для микропрограммируемой ЭВМ | 1988 |

|

SU1667084A1 |

| УСТРОЙСТВО КОММУТАЦИИ | 1971 |

|

SU294139A1 |

| СЕЛЕКТОРНЫЙ КАНАЛ ПАМЯТИ | 1972 |

|

SU326578A1 |

| Резервированное устройство формирования сигналов управления абонентами | 1975 |

|

SU526894A1 |

| Микропрограммное устройство для ввода-вывода информации | 1983 |

|

SU1144099A1 |

| Многоканальное устройство для подключения абонентов к общей магистрали | 1990 |

|

SU1797123A1 |

| Устройство для обмена данными между электронно-вычислительной машиной и абонентами | 1985 |

|

SU1277125A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1156073A1 |

| Адаптивная система обработки данных | 1985 |

|

SU1312596A1 |

| УСТРОЙСТВО ДЛЯ ПЕРВИЧНОЙ ОБРАБОТКИ ИНФОРМАЦИИ | 1973 |

|

SU367426A1 |

Даты

1971-01-01—Публикация