Изобретение относится к области вычислительной техники.

Известны устройства коммутации считанных из основной памяти данных, содержащие регистры, схемы сборки, логические схемы, триггеры, дешифраторы, схемы управления.

Известные устройства дают возможность одновременно работать лишь двум блокам основной памяти, что снижает их быстродействие.

Изобретение позволяет увеличить быстродействие устройст1ва управления основной памятью, использовать В вычислительной системе блоки памяти с различными циклами, заменять блоки памяти на более быстрые без изменения структуры устройства унравлепия памятью.

С этой целью выход схемы управления выборкой уира1вляюпдих слов основной памяти соединен с первым входом схемы выборки управляюпдих слоев, а вторые входы связаны с выходами регистров магазина управляюш их слов основной -памяти, ее первый выход подсоединен к первому входу схемы управления считыванием из основной памяти, второй вход которой соединен с выходом регистра концов чтения, вход которого связан с шиной концов чтения, связанной со всеми блоками основной памяти, первый выход схемы управления считыванием из основной памяти

соединен с первым входом триггера блокировки, второй выход подключен к первым входам схемы сборки считанной информации и схемы сборки сбоев, первый выход триггера блокировки связан со входом схемы управления выборкой управляющих слов основной памяти, первые входы схемы выборки кода номера блока основной памяти соединены с выходами регистров магазина управляющих

слов основной памяти, ее вторые входы подключепы к первому выходу схемы управления сбросом, выход схемы выборки кода ломера блока основной намяти соединен с первым входом схемы сброса регистров магазина,

второй вход которой подсоединен к выходу схемы слежения, выход схемы сброса магазина соединен со входом схемы управления сбросом и с управляющими входами регистров магазина управляюших слов осповной

памяти, второй выход схемы управления сбросом связан с первым входом схемы слежения, второй вход которой соединен с выходом схемы унравлепия выборкой управляющих слов.

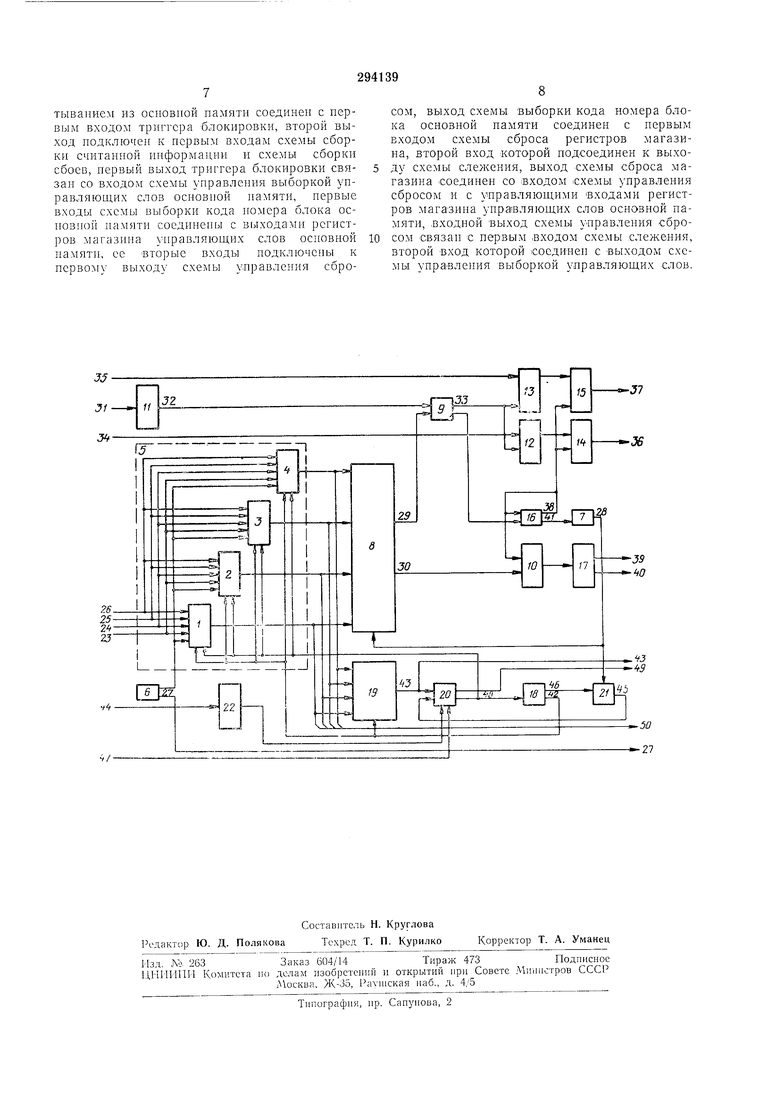

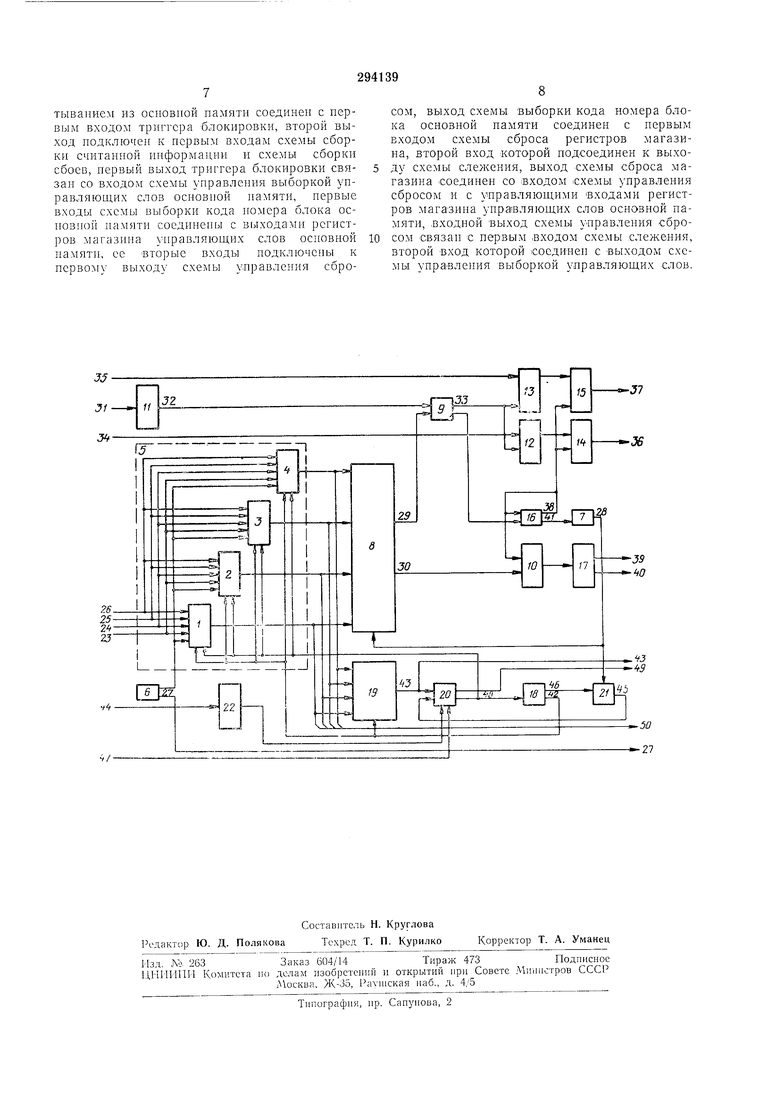

Иа чертеже представлена блок-схема устройства коммутации считанных из ос}ювнон памяти дапных.

ной памяти, схему 6 в магазин, схему 7 управления выборкой управляющих слов основной памяти, схему 8 выборки управляющих слов, схему 9 управления считывания из основной памяти, регистр 10 номера приемника, регистр }} концов чтения, схему 12 сборки считанной информации, схему 13 сборки сбоев, регистр 14 считанной информации, регистр 15 сбоев, триггер 16 блокировки, схему /7 распределения считанных данных, схему 18 управления сбросом регистров магазина, схему 19 выборки кода номера блока основной памяти, схему 20 сброса регистров магазина, схему 21 слежения, регистр 22 концов циклов.

В исходном состоянии регистры /-4 магазина 5 управляющих слов основной намяти свободны. Схема 6 управления записью в магазин, включающая счетчик записи и расшифровывающий его состояние дешифратор, указывает, что записьПервого управляющего слова основиой памяти будет производиться в регистр 4 магазина управляющих слов. В управляющее слово основной памяти входят; признак занятости соответствующего блока памяти, код номера запроса, по которому производится обращение в основную , признак режима памяти и код номера блока намяти. Признак занятости блока памяти, признак режима памяти и код номера блока памяти поступают соответственно по линиям 23, 24, 25 из устройства анализа запросных слов и коммутации основной намяти. Из этого же устройства поступает сигнал разрещения записи в магазин управляюп1,их слов осиовной намяти.

Код номера занроса ностунает по линии 26 из устройства обработки запросов.

По сигналу из устройства аналИза запросных слов производится запись управляющего слова памяти в регистр 4 магазина управляющих слов, и к содержимому счетчика схемы 6 управления зап.и.сью в магазии прибавляется единица. Таким образом, следующее управляющее слово основной памяти запишется в регистр 3 магазина и т. д.

Одновременно с записью в магазин эта схема вырабатывает сигнал сброса, который но линии 27 поступает в устройство обработки запросов. Последнее по этому сигиалу подготавливается к обработке новых запросов.

Поскольку пуск блоков основпой памяти осуществляется последовательно н управляющие слова работающих блоков иамяти раснолагаются в магазине 5 в норядке заиуска этих блоков, то выборка из оспов1ной памяти и, следовательно, из регистров магазина 5 управляющих слов также производится последовательно. Схема 7 управлення выборкой из магазина, в состав которой входит счетчик выборки управляющих слов и дешифратор состоЯПия счетчика, указывает по линии 28 регистр магазина, из которого производится считываиие управляющего слова.

Схема 8 выборки управляющих слов считывает содержимое этого регистра 1магазина и по линии 29 передает код номера блока памяти и признак режима памяти на схему 9 управления считыванием из основной иамяти. Код номера запроса передается по линии 30 на вход регистра 10 номера приемника считанных из основной памяти данных. В момент окончания выборки информации каждый

блок основной памяти посылает сигнал «Конец чтення по линии 3.1. Этот сигнал запомннается на соответствующелг триггере регистра 11 концов чтения.

Код аюмера блока основной памяти с регистра магазина расшифровывается на схеме 9 унравления считыванием из основной памяти. При наличии сигнала «Конец чтения на линии 32 с выхода триггера, соответствующего расщифрованному коду блока регистра 11 концов чтения, вырабатывается сигиал разрешения считывания из памяти. Этот сигнал по линии 33 открывает соответствующие вентили считанной информации на схеме 12 сборки считанной информации и вентили сбоев, обнаруженных в блоке памяти, на схеме 13.

Считанная из информация и сбои, обнаруженные в блоках памяти, передаются соответственно по линиям 34, 35 одновременно с сигналами :кО:Нцов чтения. Информация и сбои, которые считаны из блока основной иамяти, соответствующего расщифроваиному коду номера блока на схеме 9 унравления считыванием, принимаются на регистр 14 считанной информации и регистр 15 сбоев. Из этих регистров по линиям 36 и 37 информация и сбои передаются в соответствующие регистры нриемпика капалов и цвнтра тьного вычислителя.

Одновременно с приемом считанной информации и сбоев производится запись кода помера приемника в регистр 10 и устанавливается в единицу тр.иггер 16 блокировки, который по линии 38 блокирует ирием на регистры 10, 14, 15. Код, записанный в регистре 10 номера приемника, расшифровывается на схеме 17 распределения считанных данных, и в соответствующий абонент посылается сигнал сопровождения считанных данных. Сигналы сопровождения данных передаются в центральный вычислитель по линии 39, к каналам - тю линии 40.

Если осун;ествляется режим заииси информации в намять, то информация на регистр

14 не нринимается, и в соответствующий абонент передаются только сбои, обнаруженные в памяти, и сигнал сопровождения считанных данных. Сигнал сопровождения считанных данных указывает абоненту, что обмен с основной памятью окончен. Этот сигнал передается в соответствующий абонент независимо от режима памяти и наличия сбоев.

став схемы 7, на единицу. Таким образом, схема 7 указывает следующий регистр магази«а 5 управляющих слов основной памяти, из которого будет выбираться управляющее слово для расшифровки.

Схема 18 управления сбросом регистров магазина 5, в состав которой входит счетчик управления сбросом и дешифратор состояния этого счетчика, указывает по линии 42 регистр магазина 5 управляющих слов, который должен освободиться в первую очередь. Очевидно, что и блок памяти, код номера которого записан в этом регистре, должен освободиться в первую очередь. Схема 19 выборки кода номера блока основной намят.и при наличии сигнала на линии 42 выбирает этот код из соответствующего регистра магази.на 5. По линии 43 код выбранного блока передается в устройство обработки запросов для сравнения с кодами номеров блоков основной памяти, записанными в регистрах буфера признаков неудовлетворенных запросов. Кроме того, этот код передается на вход схемы 20 сброса регистров магазина.

Сброс освобождающегося регистра магазина 5 управляющих слов основной памяти должен производиться при выполнении следующих условий.

1.Если блок основной памяти, которому соответствует записаиный в этом регистре код номера блока, освободился, т. е. при наличии сигнала конца цикла от этого блока памяти по линии 44. Это условие связано с необходимостью алализа занятости блоков памяти, при котором код .номера блока обрабатывающегося запроса сравнивается с кодами номеров блоков памяти, записанными в регистрах магазина 5.

2.Если данные, считанные из памяти, приняты на соответствующие регистры 14 и 15, т. е. При наличии сигнала на линии 45 с выхода схемы 21 слежения. При этом код на счетчике схемы 7 управления выборкой управляющих слов основной памяти должен быть на единицу больше кода на счетчике схемы 18 управления сбросом регистров магазина. За состоянием этих счетчиков следит схема 21 слежения, на первый вход которой по линии 46 заводится код счетчика схемы 18, на второй вход по лилии 28 заводится код счетчика схемы 7.

Это условие особенно важно при малом цикле блоков основной памяти, поскольку при уменьшении цикла памяти уменьшается временной интервал между концом чтения и концом цикла. Очевидно, что этого промежутка времени может быть недостаточно для передачи считанных данных в каналы ввода - вывода.

3.При совпадении кода номера блока памяти из освобождающегося регистра магазина 5 с кодом номера блока памяти, записанном в каком-либо регистре буфера признаков неудовлетворенных запросов (устройства обработки запросов), необходимо произвести

выборку признаков из этого регистра буфера. При это.м гашение освобождающегося регистра магазина 5 осуществляется лишь при наличии сигнала по линии 47 из устройства обработки запросов.

При выполнении всех этих условий схема 20 сброса регистров магазина вырабатывает сигнал по линии 48, который производит сброс освобождающегося регистра магазина 5 и

прибавляет единицу к содержимому счетчика схемы 18 управления сбросом. При этом схема .8 по линии 42 указывает следующий ос; вобождающийся регистр.

Сигнал «Конец цикла блока основной памяти, соответствуюп;его выбранному из магазина 5 коду номера блока, передается в устройство обработки запросов с выхода схемы 20 по линии 49.

Коды номеров блоков основной памяти с

регистров магазина 5 передаются в устройство анализа заПросных слов и коммутации шин памяти по линии 50.

Регистр 22 концов циклов необходим для запоминания сигналов окончания работы блоков основной памяти.

Наличие магазина 5 управляющих слов основной памяти дает возможность осуществить одновременную работу нескольких блоков памяти. Это позволяет полностью использовать

возможности основной памяти при наличии большого количества автономных блоков. Наличие сигналов конца чтения и конца цикла от каждого блока основной памяти дает возможность осуществить асинхронный принцип

связи устройства управления основной памятью с блоками памяти. Асинхронный принцип связи упрощает структуру устройства управления основной памятью, дает возможность заменять блоки памяти на более быстрые, не накладывает жестких требований на идентичность циклов блоков основной памяти и позволяет располагать блоки памяти на произвольном расстоянии от центрального вычислителя.

Предмет изобретения

Устройство ком.мутации считанных из основной памяти данных, содержащее регистры,

схемы сборки, триггеры, дешифраторы, логические схемы, схемы управления, схему распределения считанных данных, схемы выборки, отличающееся тем, что, с целью повышения быстродействия, выход схемы управления

выборкой управляющих слов основной памяти соединен с первым входом схемы выборки управляющих слов, а вторые входы связаны с выходами регистров магазина управляющих слов основной памяти, ее первый выход подсоединен к первому входу схемы управления считыванием из основной памяти, второй вход которой соединен с выходом регистра концов чтения, вход которого связан с шиной концов чтения, связанной со всеми блоками основной

тыванием из основной па.мяти соединен с первым входом триггера блокировки, второй выход подключен к норвым входам схемы сборки считанной информации и схемы сборки сбоев, иервый выход триггера блокировки связан со входом схемы управления выборкой управляющих слов основной памяти, нервые входы схемы выборки кода номера блока осHOBHoii намятн соединены с выходамн регистров магазина унравляюгцих слов основной памяти, ее вторые входы подключены к первому выходу схемы управления сбросом, выход схемы выборки кода номера блока основной памяти соединен с нервым входом схемы сброса регистров магазипа, второй вход которой нодсоединен к выходу схемы слежения, выход схемы сброса магазина Соединен со входом Схемы управления сбросом и с управляющими входами регистров магазина унравляющих слов основной намяти, входной выход схемы управления сбросом связан с первым входом схемы с.тежения, второй вход которой соединен с выходом схемы управления выборкой управляющих слов.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЛАТЕНТНО-УЕХиЛ-ГКАЯ,БИБЛИОТЕКА | 1970 |

|

SU283685A1 |

| УСТРОЙСТВО ДЛЯ ОБРАБОТКИ ЗАПРОСОВ~.„„.„,™^ ! еСс-СО:0-НАЯ I>&'• V:':-'*^^ -••-,-•-.:--.• i ' t -• ik - и i^ - .. -.i ,•?••'*• "^^ r-: -f^'"'- —; •• лi—- .Л—.Mt'^-^y i ^'. ;'".-,'-\ | 1971 |

|

SU294141A1 |

| ЦЕНТРАЛЬНЫЙ ПРОЦЕССОР МУЛЬТИПРОГРАММНОЙ МУЛЬТИПРОЦЕССОРНОЙ ВЫЧИСЛИТЕЛЬНОЙ СИСТЕМЫ | 1971 |

|

SU309363A1 |

| БУФЕРНОЕ ЗАПОМИНАЮЩЕЕ УСТРОИСГСО | 1970 |

|

SU287123A1 |

| Устройство для сбора данных о работе ЭВМ | 1982 |

|

SU1121679A1 |

| Устройство для сопряжения периферийного устройства с ЭВМ | 1988 |

|

SU1596339A1 |

| Система ввода-вывода для микропрограммируемой ЭВМ | 1988 |

|

SU1667084A1 |

| Устройство внешних каналов | 1988 |

|

SU1695313A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1984 |

|

SU1288704A1 |

| Процессор полупроводниковой внешней памяти высокопроизводительной вычислительной системы | 1987 |

|

SU1539789A1 |

Авторы

Даты

1971-01-01—Публикация