Изобретение относится к области вычислительной техники и, в частности к селекторному каналу памяти для обмена данными между устройствами памяти системы.

Известны селекторные каналы памяти, содержащие устройство для сопряжения канала с памятью, регистр адреса внешнего устройства, регистр адреса команды, один регистр данных, регистр счета данных, сумматор, регистр ключа защиты, регистр «флажков, регистр состояний канала, регистр кода операции, дещифратор кода операции.

Недостатком известных селекторных каналов памяти является сложное управление и сравнительно небольшое быстродействие.

Для устранения этих недостатков предложенный селекторный канал памяти содержит второй регистр данных, дешифратор адреса внешнего устройства, второй дешифратор кода операции, дешифратор разрядов счета данных первого управляющего слова канала, триггер обмена массивом произвольной длины, счетчик числа обслуживаемых устройством расширенной памяти требований от канала, триггер и шииу предварительной выборкТ устройства памяти, причем дешифратор адреса внешнего устройства связан с устройством для сопряжения канала с вычислителем и с устройством для сопряжения канала с памятью; второй регистр адреса данных соединен с устройством для сопряжения канала с памятью, с первым регистром адреса данных и с сумматором; второй дешифратор кода операции подключен к регистру кода операции, к триггеру секторного обмена и соединен со 1вторым регистром адреса данных; триггер .обмена массивом произвольной длины подключен ко

второму регистру адреса данных; триггер предварительной выборки устройства памяти связан со счетчиком числа требований от канала, обслуживаемых устройством памяти, и с щиной предварительной выборки; счетчик

числа требований от канала, обслуживаемых устройством памяти, соединен с шиной сопровождения данных расширенной памяти.

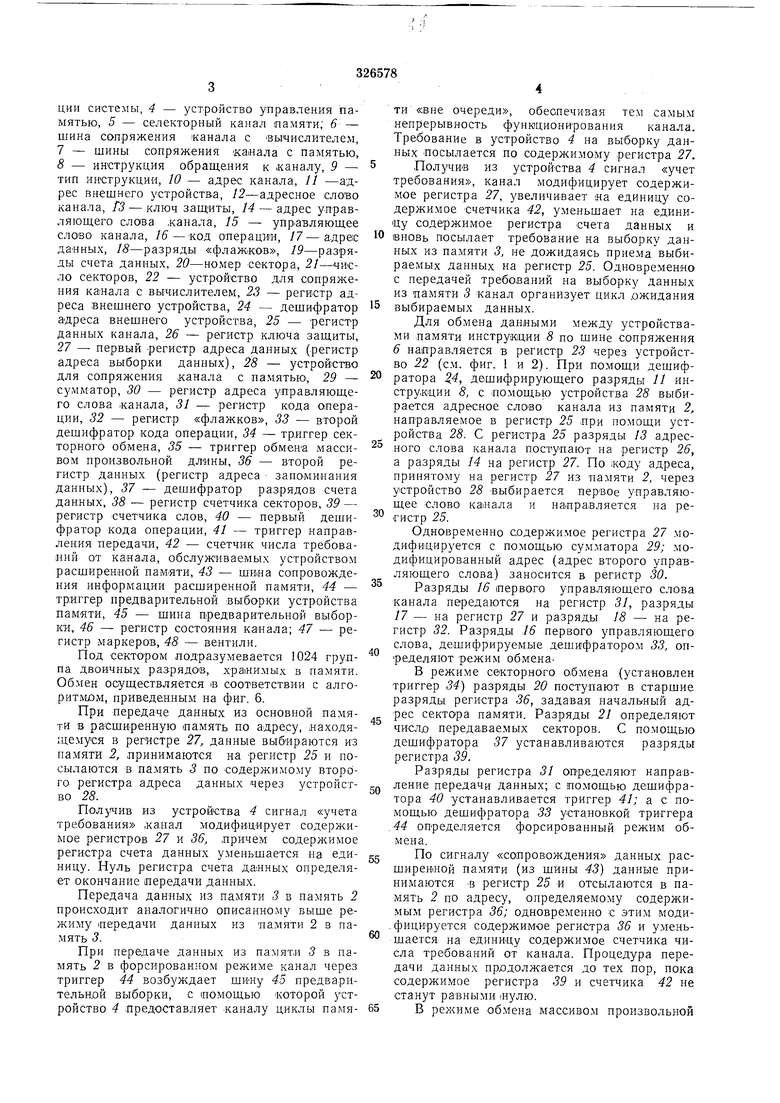

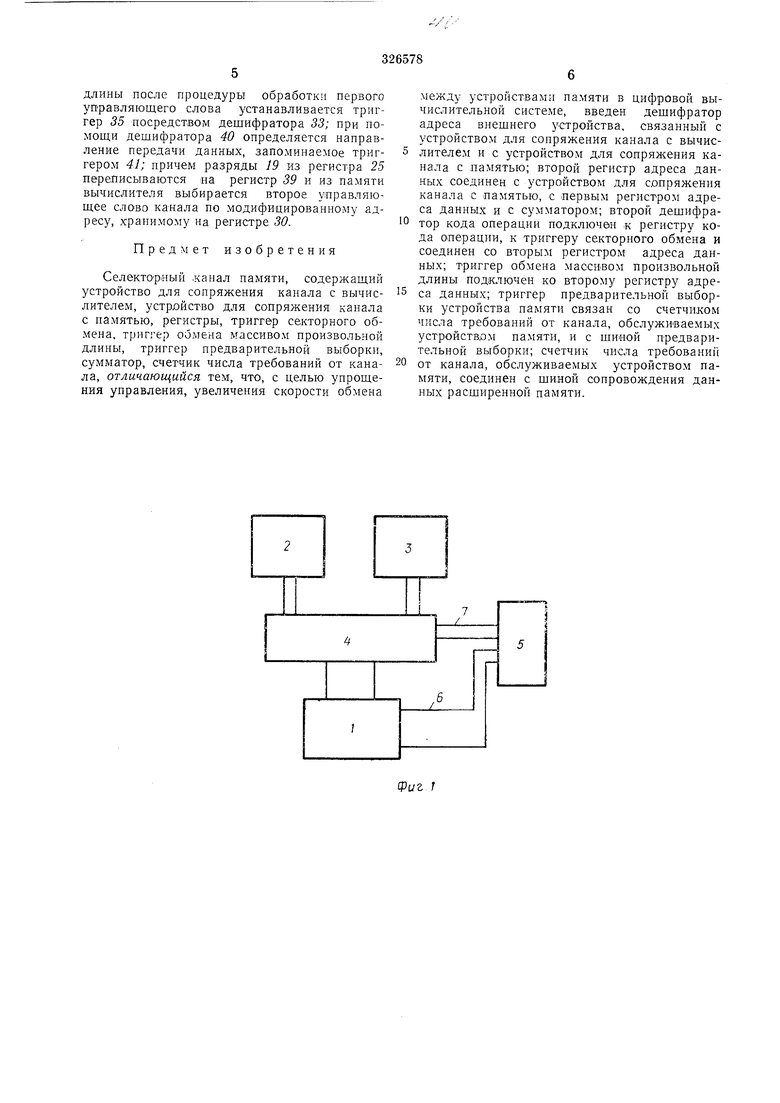

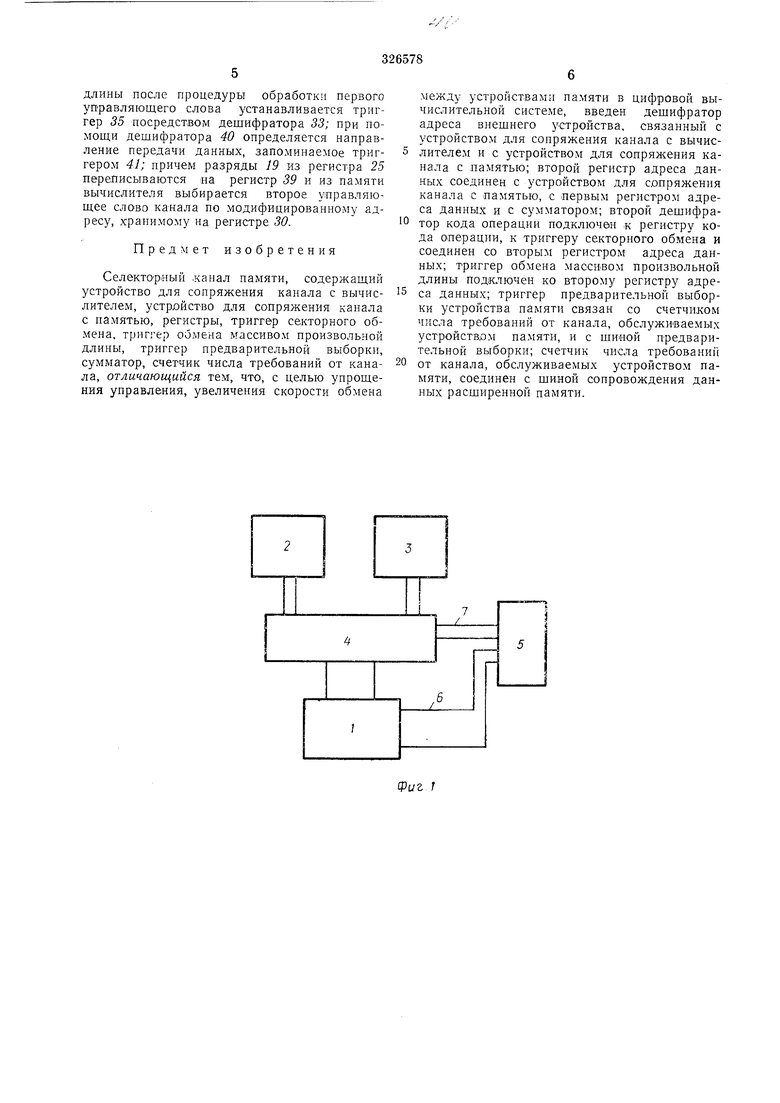

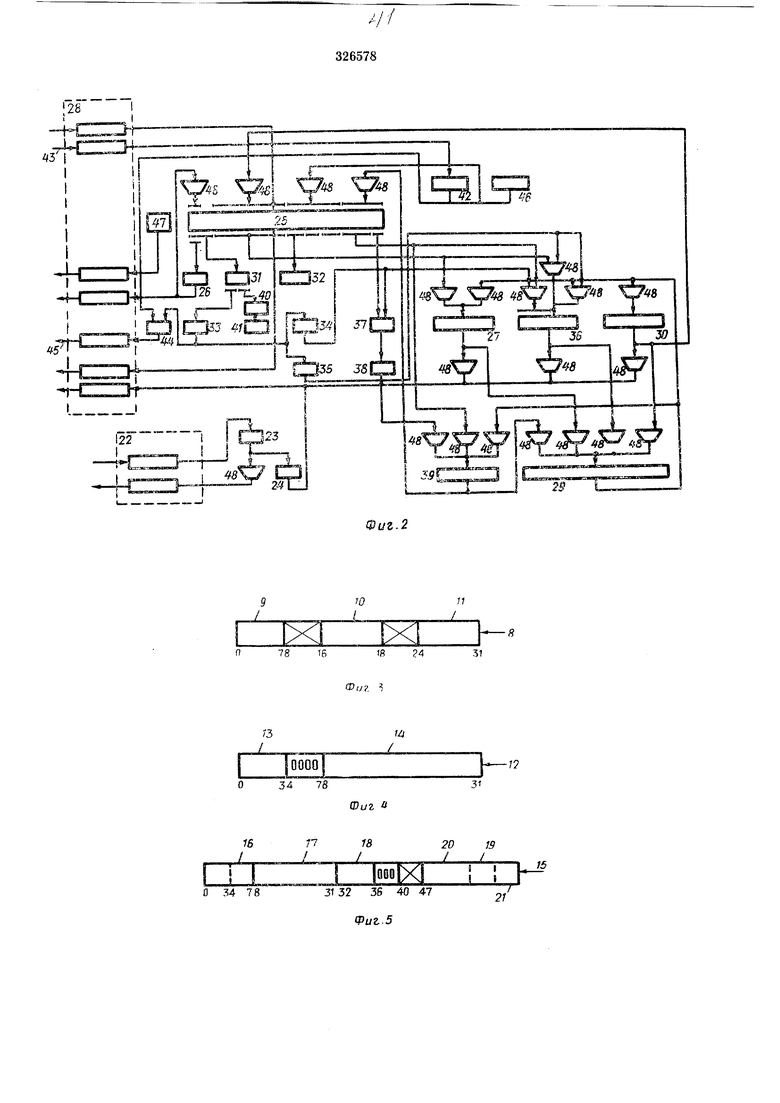

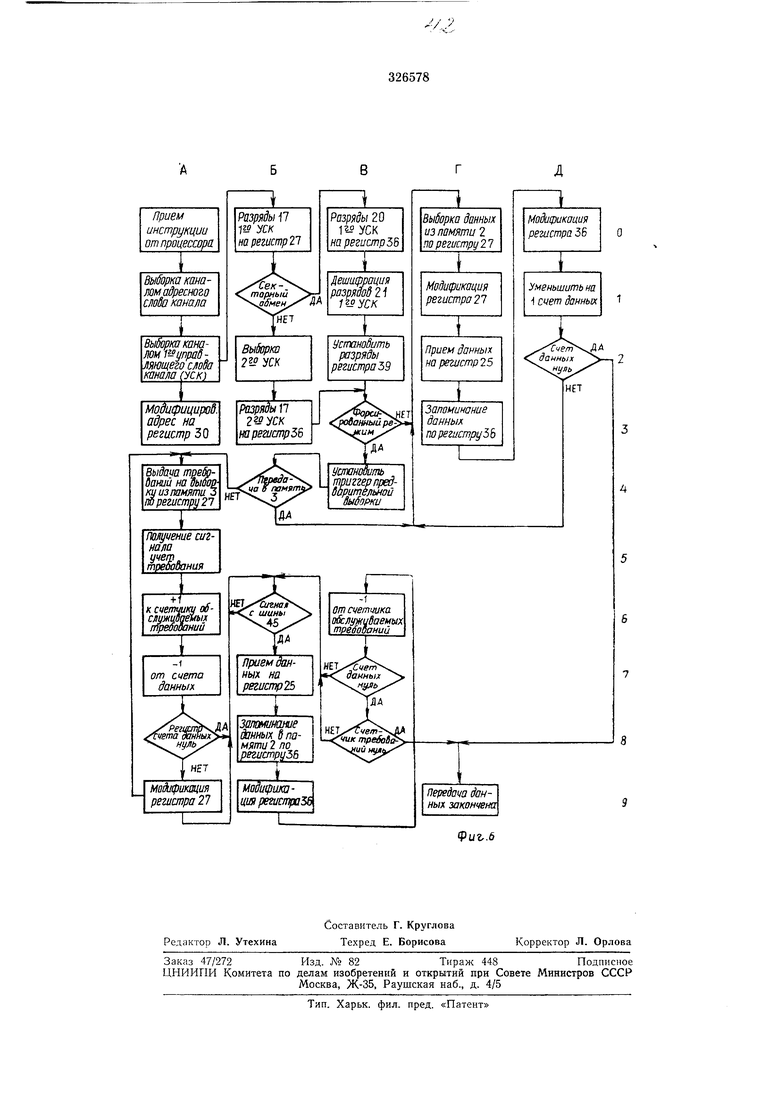

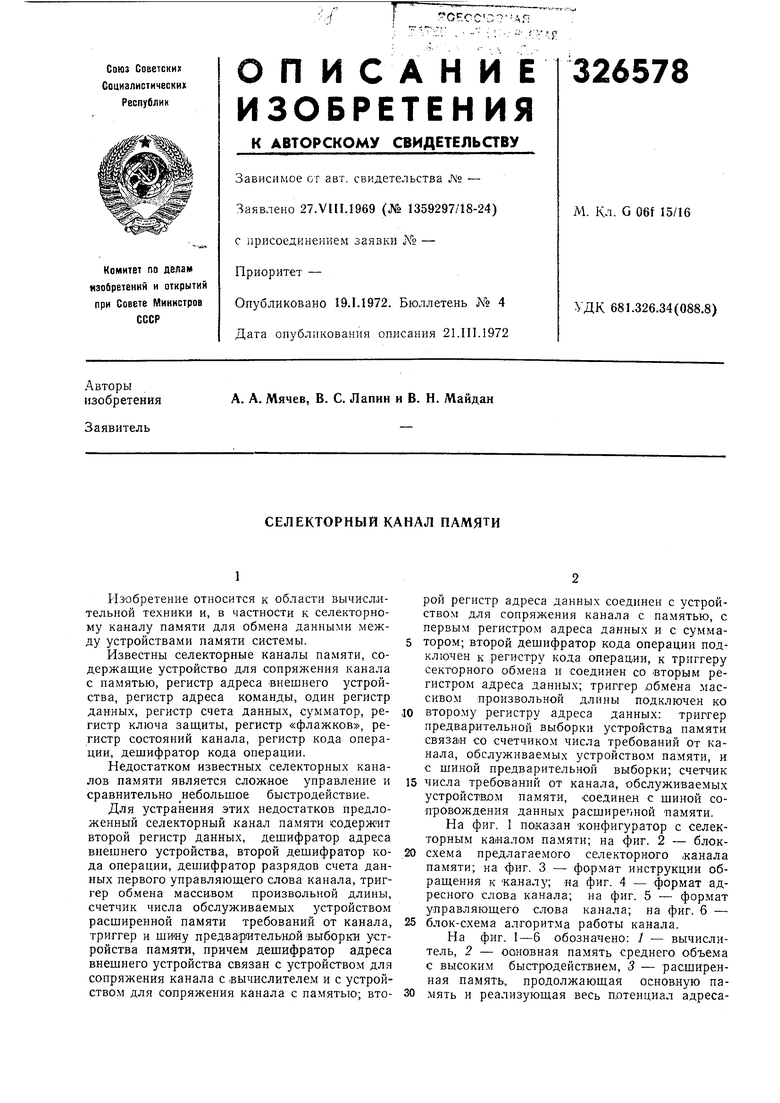

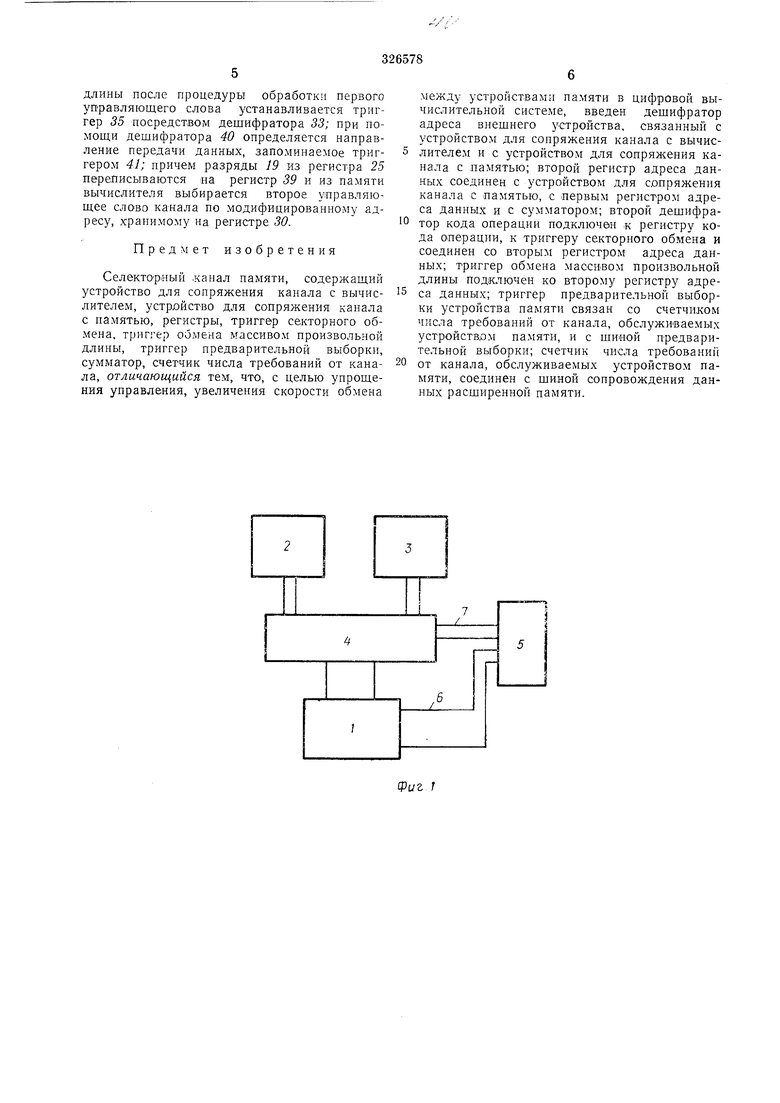

На фиг. I показан конфигуратор с селекторным каналом па.мяти; на фиг. 2 - блоксхема предлагаемого селекторного .канала памяти; на фиг. 3 - формат инструкции обращения к каналу; на фиг. 4 - формат адресного слова канала; на фиг. 5 - формат управляющего слова канала; на фиг. 6 -

блок-схема алгоритма работы канала.

На фиг. I-6 обозначено: 1 - вычислитель, 2 - основная память среднего объема с высоким быстродействием, 3 - расширенная память, продолжающая основную память и реализующая весь аотенциал адресации системы, 4 - устройство управления памятью, 5 - селекторный канал памяти; 6 - шина сопряжения канала с вычислителем,

7- шины сопряжения канала с памятью,

8- инструкция обраш,ения к каналу, 9 - тип инструкции, 10 - адрес канала, // -адрес внешнего устройства, 12-адресное слово канала, ГЗ - ключ защиты, 14 - адрес управляющего слова .канала, 15 - упр авляющее слово канала, 16-код операции, 17-адрес данных, 18-разряды «флажков, 19-разряды счета данных, 20-номер сектора, 21-число секторов, 22 - устройство для сопряжения канала с вычислителем, 23 - регистр адреса внешнего устройства, 24 - дешифратор адреса внешнего устройства, 25 - регистр данных канала, 26 - регистр ключа защиты, 27 - первый регистр адреса данных (регистр адреса выборки данных), 28 - устройство для сопряжения канала с памятью, 29 - сумматор, 30 - регистр адреса управляющего слова -канала, 31 - регистр кода операции, 32 - регистр «флажков, 33 - второй дешифратор кода операции, 34 - триггер секторного обмена, 35 - триггер обмена массивом произвольной длины, 36 - второй регистр данных (регистр адреса - запоминания данных), 37 - дешифратор разрядов счета данных, 38 - регистр счетчика секторов, 39 - регистр счетчика слов, 40 - первый дешифратор кода операции, 41 - триггер направления передачи, 42 - счетчик числа требований от канала, обслуживаемых устройством расширенной пам-яти, 43 - шина сопровождения информации расширенной памяти, 44 - триггер предварительной выборки устройства памяти, 45 - шина предварительной выборки, 46 - регистр состояния канала; 47 - регистр маркеров, 48 - вентили.

Под сектором подразумевается 1024 группа двоичных разрядов, хранимых в памяти. Об.мен осуществляется в соответствии с алгоритмом, приведенным на фиг. 6.

При передаче данных из основной памяти в расширенную память по адресу, находягцемуся в регистре 27, данные выбираются из памяти 2, принимаются на регистр 25 и посылаются в память 3 по содержимому второго регистра адреса данных через устройство 28.

из устройства 4 сигнал «учета требования канал .модифицирует содержимое регистров 27 и 36, причем содерлсимое регистра счета данных уменьшается на единицу. Нуль регистра счета данных определяет окончание передачи данных.

Передача данных из памяти 3 в память 2 происходит аналогично описанному выше режиму передачи данных из памяти 2 в па.мять 3.

ти «вне очереди, обеспечивая тем самым непрерывность функционирования канала. Требование в устройство 4 на выборку данных посылается по содержимому регистра 27.

Получив из устройства 4 сигнал «учет

требования, канал модифицирует содержимое регистра 27, увеличивает яа единицу содержимое счетчика 42, уменьшает на единицу содержимое регистра счета данных и

0 вновь посылает требование на выборку данных из памяти 3, не дожидаясь приема выбираемых данных на регистр 25. Одновременно с передачей требований на выборку данных из памяти 5 канал организует цикл .ожидания

выбираемых данных.

Для обмена данными между устройствами памяти инструкции 8 по шине сопряжения 6 направляется в регистр 23 через устройство 22 (с.м. фиг. 1 и 2). При помощи дешифратора 24, дешифрирующего разряды // инструкции 8, с помощью устройства 28 выбирается адресное слово канала из памяти 2, направляемое в регистр 25 при помощи устройства 28. С регистра 25 разряды 13 адрес° ного слова канала поступают на регистр 26, а разряды М на регистр 27. По коду адреса, принятому на регистр 27 из памяти 2, через устройство 28 выбирается первое управляющее слово ка1нала и направляется на ре гистр 25.

Одновременно содержимое регистра 27 .модифицируется с помощью сумматора 25; .модифицированный адрес (адрес второго управляющего слова) заносится в регистр 30.

° Разряды 16 первого управляющего слова канала передаются на регистр 3/, разряды 17 - на регистр 27 и разряды J8 - на регистр 52. Разряды 16 первого управляющего слова, дешифрируемые дешифратором 33, определяют режим обменаВ режиме секторного обмена (установлен триггер 34) разряды 20 поступают в старшие разряды регистра 36, задавая начальный адрес сектора памяти. Разряды 27 определяют число передавае.мых секторов. С помощью дешифратора 37 устанавливаются разряды регистра 39.

Разряды регистра 31 определяют направg ление передачи данных; с помощью дешифратора 40 устанавливается триггер 41; а с помощью дешифратора 33 установкой триггера ,44 определяется форсированный режим обмена.

По сигналу «сопровождения данных расширенной памяти (из шины 43) данные принимаются в регистр 25 и отсылаются в память 2 по адресу, определяемому содержимым регистра 36; одновременно с этим моди, фицируется содержимое регистра 36 и уменьшается на единицу содержимое счетчика числа требований от канала. Процедура передачи данных продолжается до тех пор, пока содержимое регистра 39 и счетчика 42 не станут равными шулю.

длины после процедуры обработки первого управляющего слова устанавливается триггер 35 посредством дешифратора 33; при иомощи дешифратора 40 определяется направление передачи данных, запоминаемое триггером 41; причем разряды 19 из регистра 25 переписываются яа регистр 39 и из памяти вычислителя выбирается второе управляющее слово канала по модифицированному адресу, хранимому на регистре 30.

Предмет изобретения

Селекторный .канал памяти, содержащий устройство для сопряжения канала с вычислителем, устройство для сопряжения канала с памятью, регистры, триггер секторного обмена, триггер обмена массивом произвольной длины, триггер предварительной выборки, сумматор, счетчик числа требований от канала, отличающийся тем, что, с целью упрощения управления, увеличения скорости обмена

между устройствами памяти в цифровой вычислительной системе, введен дешифратор адреса внешнего устройства, связанный с устройством для сопряжения канала с вычислителем и с устройством для сопряжения канала с памятью; второй регистр адреса данных соединен с устройством для сопряжения канала с памятью, с первым регистром адреса данных и с сумматором; второй дешифратор кода операции подключен ,к регистру кода операции, к триггеру секторного обмена и соединен со вторым регистром адреса данных; триггер обмена массивом произвольной длины подключен ко второму регистру адреса данных; триггер предварительной выборки устройства памяти связан со счетчиком числа требований от канала, обслуживаемых устройством памяти, и с шиной предварительной выборки; счетчик числа требовани от канала, обслуживаемых устройством памяти, соединен с щиной сопровождения данных расширенной памяти.

| название | год | авторы | номер документа |

|---|---|---|---|

| Селекторный канал | 1982 |

|

SU1053096A1 |

| Система ввода-вывода для микропрограммируемой ЭВМ | 1988 |

|

SU1667084A1 |

| Селекторный канал | 1983 |

|

SU1160427A1 |

| Селекторный канал | 1981 |

|

SU1029175A2 |

| ПРОЦЕССОР ДЛЯ ЦИФРОВОЙ СИСТЕМЫ ОБРАБОТКИ ДАННЫХ | 1971 |

|

SU305477A1 |

| Устройство отсчета времени в цвм | 1977 |

|

SU691828A1 |

| Устройство внешних каналов | 1988 |

|

SU1695313A1 |

| Селекторный канал | 1988 |

|

SU1534465A2 |

| Устройство для сопряжения электронно-вычислительной машины (ЭВМ) с внешним устройством | 1984 |

|

SU1272337A1 |

| Устройство для управления вводом-выводом | 1989 |

|

SU1735859A1 |

IX ТКГ

П7816

/3

I jooooj

о34 78

Гб

77ГЙ

//

34 78

31 32 36 40 47

Фиг.2

31

-;

31

20

/ /

/5

21

Фиг 5

Даты

1972-01-01—Публикация