Изобретение отноеитея к области вычислительной техники.

Известно устройство для сложения и вычлтания, работающее в десятичном коде е запоминаинел цифры «пять, в котором десяти иый разряд выполнен на 5 триггерах.

В предлагаемом вычислительном устройстве десятичный разряд выполнен на 4 триггерах, а схема управления младшими разрядами содержит схему коррекции запрещенных кодовых состояний, один выход которой соедиен со входом (п-1)-го разряда регистра сум., другой выход - СО входом младшего разряда регистра суммы и со входом схемы сложения цифры «пять, выход которой соединен со входом (п-1)-го разряда регистра суммы, вы:;од схемы младшего разряда ре..мстра суммы соединен со входом схемы коррекции.

Зто позволяет сократить оборудование и повысить быстродействие устройства.

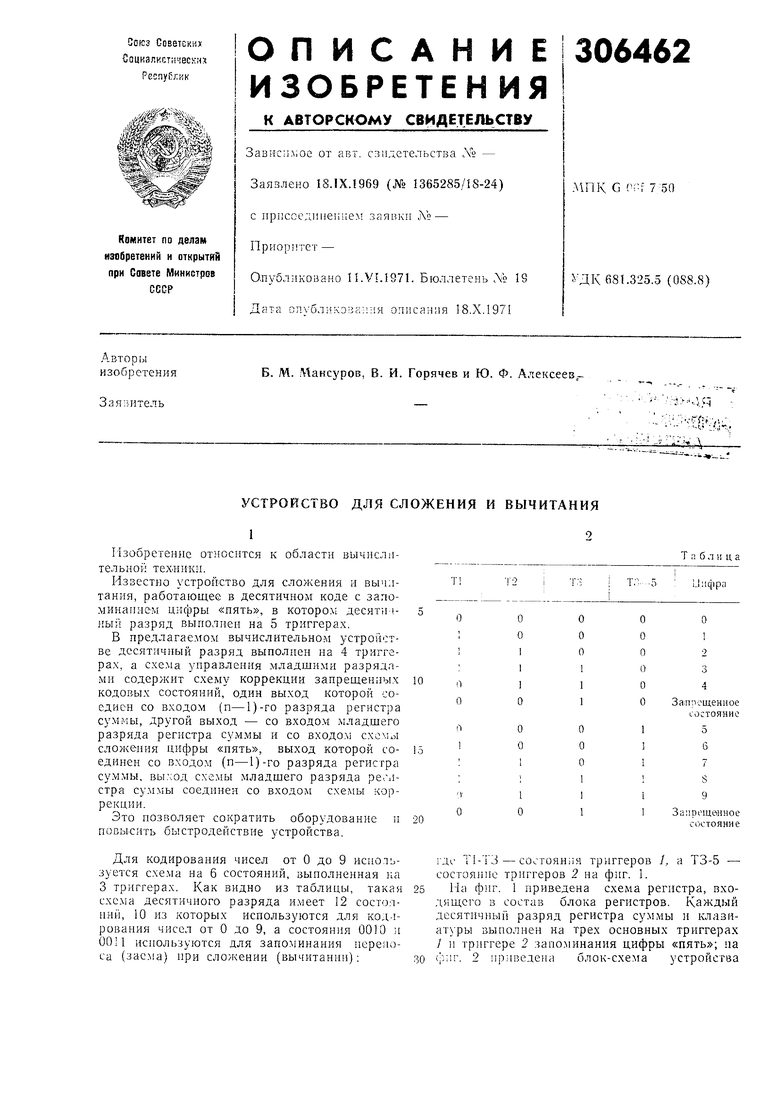

Для кодирования чисел от О до 9 исиользуется схема на 6 состояний, выполненная на 3 триггерах. Как видно из таблицы, такая схема десятичного разряда имеет 12 состолний, 10 из которых используются для кодирования чисел от О до 9, а состояния 0010 и ООП используются для запоминания переноса (засма) при сложении (вычитанни);

Таблица

то

ТЛ- -5

О О 1 1 1 О

о о

Запрещенное состояние

гдо TI-T3 - состоян11я триггеров 1, а ТЗ-5 - состояние триггеров 2 на фиг. 1.

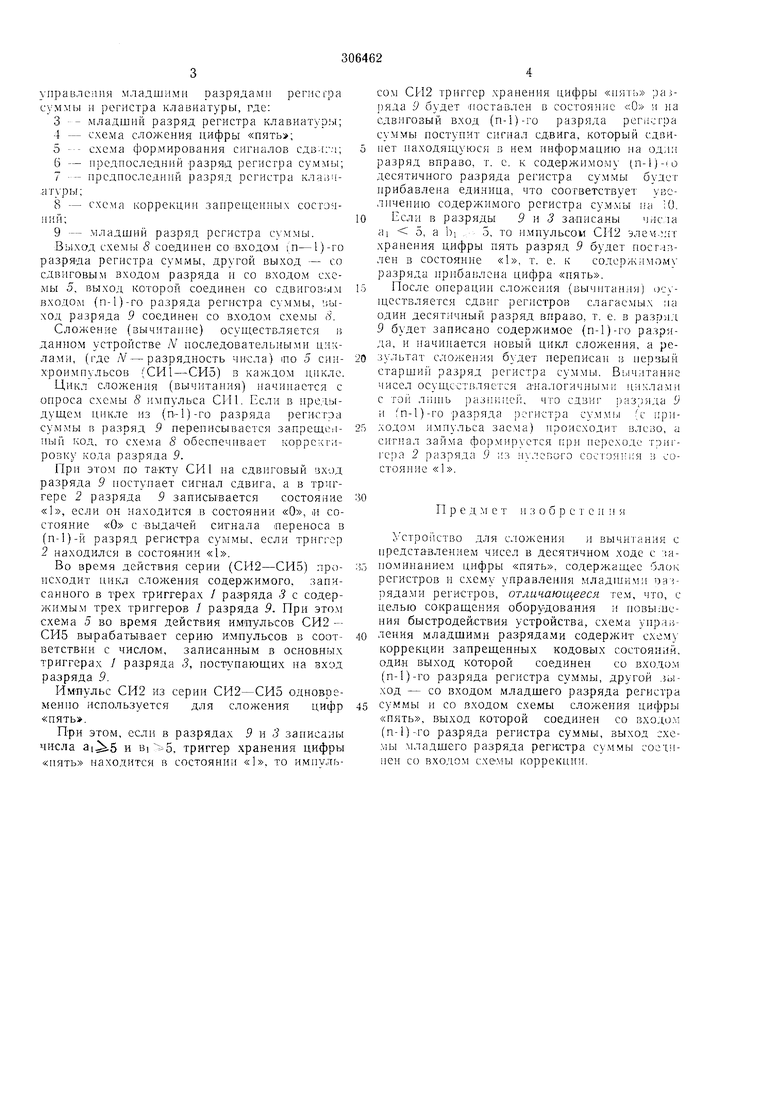

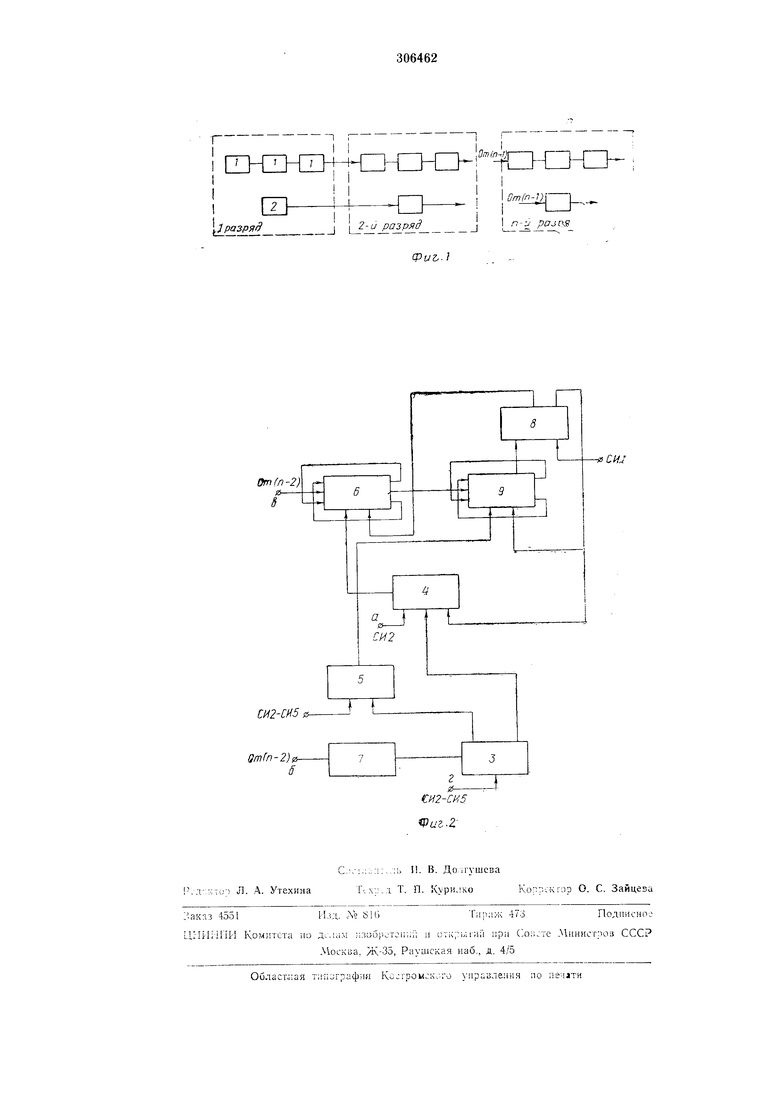

Ма фиг. 1 приведена схема регистра, входящего в состав блока регистров. Каждый десятичный разряд регистра суммы и клавиатуры выполнен на трех основных триггерах / и триггере 2 запо.минания цифры «пять ; па (j-nr. 2 ириведеиа блок-схема устройства

регистра

управлсшя младшими разрядами суммы и регистра клавиатуры, где;

младший разряд регистра клавиатуры; схема сложения цифры «пять ;

4 - схема формирования сигиалов сдвл;-,

5- предпоследний разряд регистра суммы;

6- иредпоследний разряд регистра .атуоы;

8 -

схема коррекции запрещеиных еостояПИЙ;

9 - младший разряд регистра суммы.

Выход схемы 8 соединен со входам (п-1)-го разряда регистра суммы, другой выход - со сдвиговым входом разряда и со входом схемы 5, выход которой соединен со сдвигов1лм входов (n-l)-ro разряда регистра суммы, 1 ыход разряда 9 соедииеи со входом схемы S.

Сложение (вычитание) осуществляется г, данном устройстве N носледовательиыми циклами, (где /V-разрядность числа) но 5 сиихроимиульсов (СИ1 - СИ5) в каждом и1кле.

Цикл сложения (вычитания) начинается с опроса схемы S импульса СИ1. Если в предыдущем цикле из (п.-1)-го разряда регистэа суммы в разряд 9 переписывается запрещеииыГ1 код, то схема 8 обеспечивает корректировку кода разряда 9.

При этом по СИ1 на сдвиговый вход разряда 9 ностунает сигнал сдвига, а в триггере 2 разряда 9 записывается состояние «1, если он находится в состоянии «О, « состояние «О с -выдачей сигнала переноса в (п-)-й разряд регистра суммы, если триггер 2 находился в состоя.нии «1.

Во время действия серии (СИ2-СИ5) происходит никл сложения содержимого, записанного в трех триггерах / разряда 3 с содержимым трех триггеров / разряда 9. Прц этом схема 5 во время действия импульсов СИ2 - СИ5 вырабатывает серию импульсов в соответствии с числом, записанным в основных триггерах / разряда 3, поступающих на вход разряда 9.

Импульс СИ2 из серии СИ2-СИ5 одновременно используется для с.тожения цифр «пять.

При этом, если в разрядах 9 и 3 записаны числа и BI , триггер хранения цифры «пять находится в состоянии «1, то импульсом CI--I2 триггер .хранения цифры «пять разряда 9 будет Поставлен в состояние «О и на сдвиговый вход (n-i)-ro разряда региегра су.ммы поступит сигнал сдвига, который сдвинет паходящ юся в ием инфор.мацию на од;1и разряд вправо, т. с. к содержи.мому (n-l)-i:o дееятичного разряда регистра суммы будет нрибавлена един1ща, что соответствует увеличению содержимого регистра сум.мы на ;0.

Если в разряды .9 и записаны чиста ill 5, а hi 5, то и.мпульсом С112 .;;{т хранения цифры пять разряд .9 будет посг.шлен в состояние «1, т. е. к содср/к 1мому разряда ирнбавлена цифра «пять.

После операции сложения (вычитания) осуществляется сдвиг регистров слагаемых на один десятичный разряд вправо, т. е. в разря.ч 9 будет занисано содержимое (n-l)-ro разряда, и иачинается новый цикл сложения, а результат сложения будет переписан и перзый старший разряд регистра суммы. В1,1читание чисе.т осуществляется аналогичными циклами с той Л1пнь разнице :, что 1аз;)яда 9 и fn-l)-ro разряда рсгиСтра суммы (с ириходо.м импульса заема) происходит влево, а сигнал зай.ма фор.мируется при переходе трш1е;)а 2 разряда 9 из п лсвОГО состояния в состояиие «1.

П р е д м е т п з о б р е т е п и я

ycTpoiicTBO для сложения и вычитаиия с представлением чисел в десятичном ходе с :;апо.минанием цифры «пять, содержащее блсж регистров и схему управле 1ия младюими i iaiрядами регистров, отличающееся тем, что, с целью сокращения оборудования и новышения быстродействия устройства, схе.ма ynpai5ления младшими разрядами содержит схему коррекции запрещенных кодовых состояний, оди.н выход которой соединен со входо.м (п-)-го разряда регистра суммы, другой .зыход - со входом младшего разряда регистра суммы и со входом схемы сложения цифры «пять, выход которой соединен со входом (n-i)-ro разряда регистра суммы, выход схемы младшего разряда регистра суммы соетииен со входом схемы коррекции.

разря I V

фуг../

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для алгебраического сложения чисел | 1986 |

|

SU1339552A1 |

| ЭЛЕКТРОННАЯ КЛАВИШНАЯ ВЫЧИСЛИТЕЛЬНАЯ МАШИНА | 1973 |

|

SU395837A1 |

| Устройство для деления десятичных чисел | 1982 |

|

SU1048473A1 |

| Суммирующее устройство с контролем | 1983 |

|

SU1140112A1 |

| Устройство для формирования адресов операндов процессора быстрого преобразования Фурье | 1983 |

|

SU1133597A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1985 |

|

SU1300640A1 |

| Устройство для вычисления коэффициентов Фурье | 1985 |

|

SU1315999A1 |

| Конвейерное устройство для одновременного выполнения арифметических операций над множеством чисел | 1977 |

|

SU922726A1 |

| Преобразователь двоичного кода в р-ичный позиционный код | 1983 |

|

SU1163479A1 |

| Преобразователь двоичного кода в двоично-десятичный код | 1978 |

|

SU742923A1 |

Даты

1971-01-01—Публикация