1 1

Изобретение относится к цифровой вычислительной технике и может быть использовано при построении преобразователей кодов и вычислительных уст ройств

Цель изобретения - упрощение преобразователя и расширение класса решаемых задач путем обеспечения возможности изменения основания системы счисления.

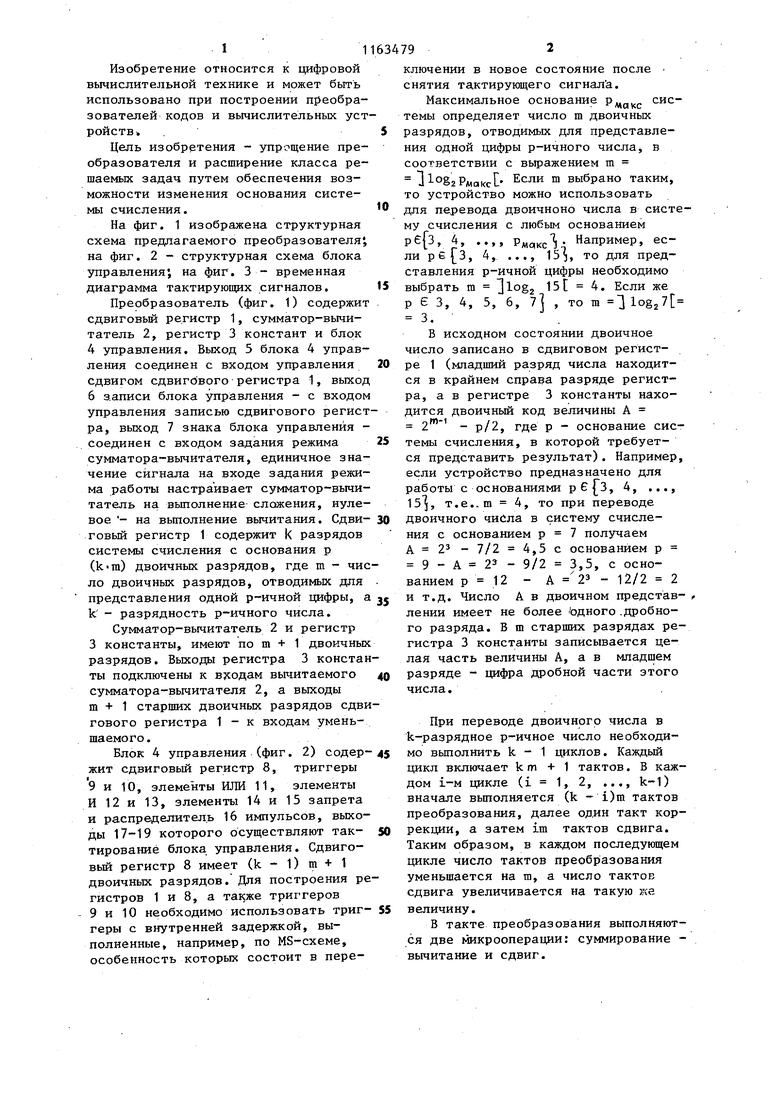

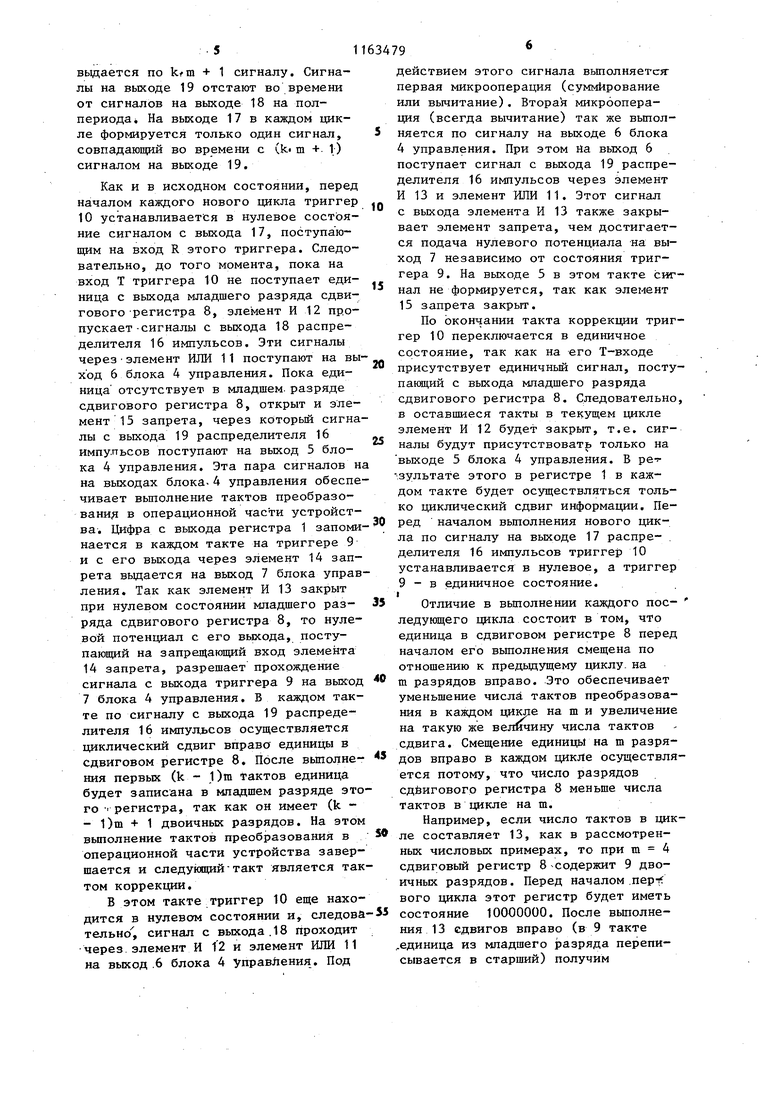

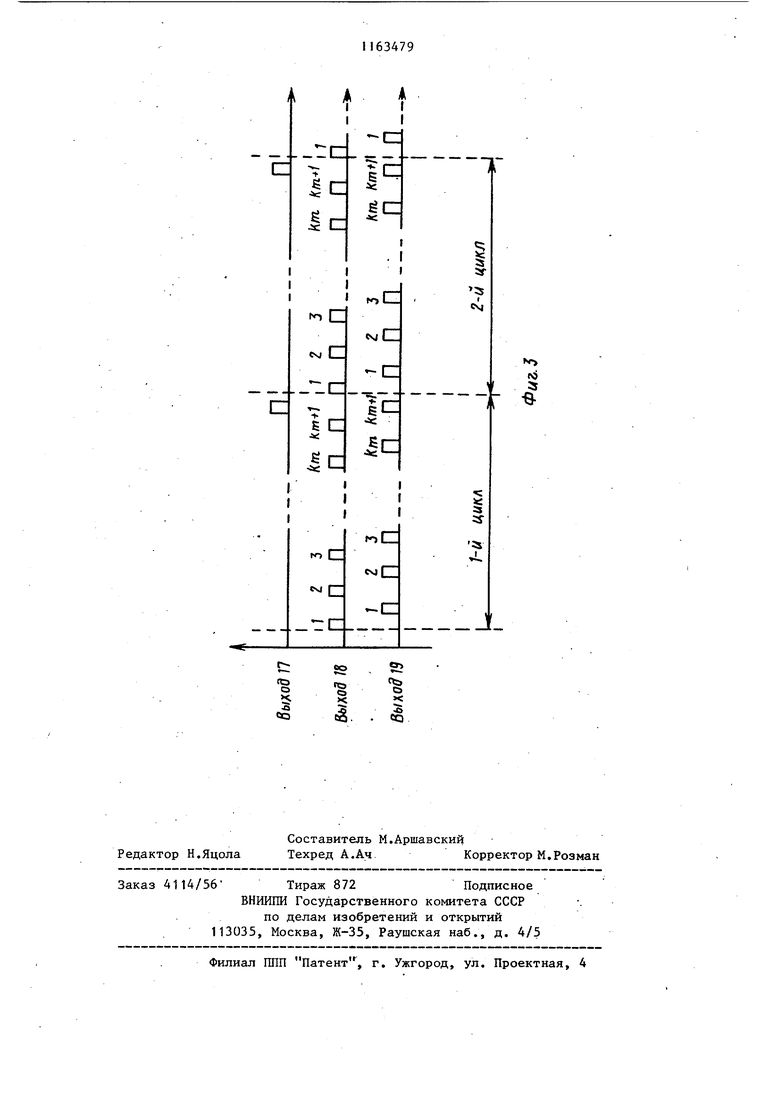

На фиг. 1 изображена структурная схема предлагаемого преобразователя; на фиг. 2 - структурная схема блока управления; на фиг. 3 - временная диаграмма тактирующих сигналов.

Преобразователь (фиг. 1) содержит сдвиговый регистр 1, сумматор-вычитатель 2, регистр 3 констант и блок 4 управления. Выход 5 блока 4 управления соединен с входом управления сдвигом сдвигбвого регистра 1, выход 6 записи блока управления - с входом управления записью сдвигового регист ра, выход 7 знака блока управления соединен с входом задания режима сумматора-вычитателя, единичное значение сигнала на входе задания режима работы настраивает сумматор-вычитатель на вьшолнение сложения, нулевое - на вьшолнение вычитания. Сдвиговый регистр 1 содержит К разрядов системы счисления с основания р (kln) двоичных разрядов, где m - чис ло двоичных разрядов, отводимых для представления одной р-ичной цифры, а k - разрядность р-ичного числа.

Сумматор-вычитатель 2 и регистр 3 константы, имеют по m + 1 двоичных разрядов. Выходы регистра 3 констан ты подключены к вкодам вычитаемого сумматора-вычитателя 2, а выходы m + 1 старших двоичных разрядов сдви гового регистра 1 - к входам уменьшаемого.

Блок 4 управления (фиг. 2) содержит сдвиговый регистр 8, триггеры 9 и 10, элементы ИЛИ 11, элементы И 12 и 13, элементы 14 и 15 запрета и распределитель 16 импульсов, выходы 17-19 которого осуществляют тактирование блока управления. Сдвиговый регистр 8 имеет (k - 1) m + 1 двоичных разрядов. Для построения регистров 1 и 8, а триггеров 9 и 10 необходимо использовать триггеры с внутренней задержкой, выполненные, например, по MS-схеме, особенность которых состоит в пере792

ключении в новое состояние после снятия тактирующего сигнала.

Максимальное основание ,. системы определяет число m двоичных разрядов, отводимых для представления одной цифры р-ичного числа, в соответствии с выражением m Jlogjp g. Если m выбрано таким, то устройство можно использовать

для перевода двоичноно числа в систему счисления с любым основанием ре{з, 4, ..,, РМЯКС Д Например, если , 4, ..., 15, то для представления р-ичной цифры необходимо

выбрать m ogj 15 4. Если же р е 3, 4, 5, 6, 7 , то ш logj7 3.

В исходном состоянии двоичное число записано в сдвиговом регистре 1 (младший разряд числа находится в крайнем справа разряде регистра, а в регистре 3 константы находится двоичный код величины А - р/2, где р - основание системы счисления, в которой требуется представить результат). Например, если устройство предназначено для работы с основаниями , 4, ..., 15, т.е..т 4, то при переводе

двоичного числа в систему счисления с основанием р 7 получаем А 2 - 7/2 4,5 с основанием р 9 - А 23 - 9/2 3,5, с основанием р 12 - А 2 - 12/2 2

и т.д. Число А в двоичном представлении имеет не более одного .дробного разряда. В m старших разрядах регистра 3 константы записывается целая часть величины А, а в младшем

разряде - цифра дробной части этого числа.

При переводе двоичного числа в k-разрядное р-ичное число необходиМО вьшолнить k - 1 циклов. Каждый цикл включает k m + 1 тактов. В каждом i-M цикле (i 1, 2, ..., k-1) вначале вьшолняется (k - i)m тактов преобразования, далее один такт коррекции, а затем im тактов сдвига. Таким образом, в каждом последующем цикле число тактов преобразования уменьшается на га, а число тактов сдвига увеличивается на такую же

величину.

В такте преобразования выполняются две микрооперации: суммирование вычитание и сдвиг.

Первой микрооперацией управляет сигнал с выхода 6 блока 4 управления По этому сигналу в m + 1 старших разрядов регистра 1 числа записывается результат суммирования (вычитания) чисел, поступающих на входы сумматора-вычитателя 3. Если при этом на выходе 7 блока 4 управления присутствует единичный потенциал, то к содержимому m + 1 старших разрядов регистра 1 числа прибавляется величина А, записанная в регистре 3 конс танты, а если нулевой потенциал вычитается величина А. По сигналу с , выхода 5 блока 4 управления о существляется сдвиг информации в регистре 1 числа на один двоичный разряд влево. В процессе сдвига цифра из старшего разряда этого регистра переписывается в его младший разряд, а также запоминается в блоке 4 управления (в триггере 9), В следующем такте соответствующий этой цифре потенциал присутствует на выходе 7 блока управления, управляя работой сумматора-вычитателя 2. В отличии от всех последующих тактов преобразования в первом такте каждого цикла на выходе 7 блока 4 управления всегда присутствует единичный потенциал, независимо от значения цифры,- поступающей на. вход блока 4 управления в предыдущем такте. В связи с этим на сумматоре-вычитателе 2 всегда осуществляется суммирование.

В такте коррекции блок 4 управления поочередно вьщает два управляющих сигнала на выход 6, в результате чего вьтолняются две микрооперации. По первому сигналу, в зависимости от значения цифры, поступившей в-бло 4 управления в предьщущем такте, осуществляется прибавление к содержи мому старших разрядов регистра 1 , числа величины А или вычитании этой величины. По второму сигналу на выг ходе 6 всегда производится вычитание величины А, так как на выходе 7 блока 4 управления в этом случае всегда присутствует нулевой потенциал. В такте коррекции сдвиг не выполняется

В каждом также сдвига блок 4 управления вьвдает только один управляющий сигнал на выход 5, в результате которого осуществляется циклический сдвиг информации в регистре 1.

Будем считать, что устройство предназначено для получения трех-разрядов р-ичного числа, где , 4, ..., isl . Следовательно, k 3 и im 4. в этом случае для получения результата необходимо выполнить k - 1 2 цикла преобразования. Первый цикл будет содержать (k - 1)m (3 - 1)4 8 тактов преобразования, такт коррекции и i-ш 1«4 4 такта сдвига. Второй цикл будет включать (k - 1) (3 - 2) 4 4 такта преобразования, такт коррекции и i in 24 8 тактов сдвига.

Если ойуществляется преобразование в систему с р 15, то в исходном состоянии преобразуемое двоичное число записано в регистре 1, а в регистре 3 константы установлен двоичный код величины А . . - р/2 15/2 0,5, т.е. содержимое 5-разрядного регистра 3 KOHCTEHTbf Имеет вид 0000,1.

При преобразовании двоичного числа в систему счисления с основанием р 7 получаем А -р/2 8 - 7/2 4,5, т.е. в регистре 3 константы записано 0100,1, Результа преобразования имеет вид Xj 654.

8данном случае, как и в рассмотренном, для предтсавления р-ичной цифры используются 4 двоичных разряда, поскольку преобразрватель предназначен для работы с основаниями

р 15. Для системы счисления с оснванием р 7 достаточно трех двоичных разрядов. Если необходимо построить устройство, для которого р. 7 являеися максимальным основанием, то можно уменьшить разрядность блоков 1-3 устройства, приняв m 3. При этом уменьшается и число тактов в каждом цикле.

Блок 4 управления обеспечивает выдачу управляющих сигналов следующим образом. В исходном состоянии в старшем разряде сдвигового регистра 8 записана единица (остальные разряды обнулены),, триггер 10 установлен в нулевое, а триггер

9- в единичное с.остояние. С начало работы преобразователя распредели- тель импульсов начинает.вырабатывать регулярную последовательность управляющих сигналов на выходах 17-19 в соответствии с временной диаграммой, приведенной на фиг. 3 (цепи запуска распределителя 16 импульсов условно не показаны). В каждом цикле на выходы 18 и 19 51 выдается по k/m + 1 сигналу. Сигналы на выходе 19 отстают во времени от сигналов на выходе 18 на полпериода На выходе 17 в каждом цикле формируется только один сигнал, совпадающий во времени с (k« m + 1) сигналом на выходе 19. Как и в исходном состоянии, перед началом каждого нового цикла триггер 10 устанавливается в нулевое состояние сигналом с выхода 17, поступающим на вход R этого триггера. Следовательно, до того момента, пока на вход Т триггера 10 не поступает единица с выхода младшего разряда сдвигового регистра 8, элемент И 12 пропускает -сигналы с выхода 18 распределителя 16 импульсов. Эти сигналы черезэлемент ИЛИ 11 поступают на вы ход 6 блока 4 управления. Пока единица отсутствует в младшем, разряде сдвигового регистра 8, открыт и элемент 15 запрета, через который сигна лы с выхода 19 распределителя 16 импульсов поступают на выход 5 блока 4 управления. Эта пара сигналов н на выходах блока-4 управления обеспе чивает выполнение тактов преобразовани 1 в операционной части устройства. Цифра с выхода регистра 1 запоми нается в каждом такте на триггере 9 и с его выхода через элемент 14 запрета выдается на выход 7 блока управ ления. Так как элемент И 13 закрыт при нулевом состоянии младшего разряда сдвигового регистра 8, то нулевой потенциал с его выхода, поступающий на запрещающий вход элемента 14 запрета, разрешает прохождение сигнала с выхода триггера 9 на вых-од 7 блока 4 управления. В каждом такте по сигналу с выхода 19 распределителя 16 импульсов осуществляется циклический сдвиг вправо едини1№1 в сдвиговом регистре 8. После вьшолнения первых (k - l)m тактов единица будет записана в младшем разряде это го регистра, так как он имеет (k - Dm + 1 двоичных разрядов. На этом вьшолнение тактов преобразования в операционной части устройства завершается и следуняций такт является так том коррекции. В этом такте триггер 10 еще находится в нулевом состоянии и, следова тельно, сигнал с выхода. 18 проходит через.элемент И 12 и элемент ИЛИ 11 на выход .6 блока 4 управления. Под 79 действием этого сигнала вьшолняетсяпервая микрооперация (суммирование или вычитание). Вторая микрооперация (всегда вычитание) так же выполняется по сигналу на выходе 6 блока 4 управления. При этом На вькод 6 поступает сигнал с выхода 19 распределителя 16 импульсов через элемент И 13 и элемент ИЛИ 11. Этот сигнал с выхода элемента И 13 также закрывает элемент запрета, чем достигается подача нулевого потенциала на выход 7 независимо от состояния триггера 9. На выходе 5 в этом такте сигнал не формируется, так как элемент 15 запрета закрыт. По окончании такта коррекции триггер 10 переключается в единичное состояние, так как на его Т-входе присутствует единичный сигнал, поступающий с выхода младшего разряда сдвигового регистра 8. Следовательно, в оставшиеся такты в текущем цикле элемент И 12 будет закрыт, т.е. сигналы будут присутствовать только на выходе 5 блока 4 управления. В ре-г .зультате этого в регистре 1 в каждом такте будет осуществляться только циклический сдвиг информации. Перед началом вьтолнения нового цикла по сигналу на выходе 17 распределителя 16 импульсов триггер 10 устанавливается в нулевое, а триггер 9 - в единичное состояние. I Отличие в вьтолнении каждого пос- ледующего цикла состоит в том, что единица в сдвиговом регистре 8 перед началом его выполнения смещена по отношению к предыдущему циклу, на m разрядов вправо. Это обеспечивает уменьшение числа тактов преобразования в каждом цикуте на m и увеличение на такую же величину числа тактов сдвига. Смещение единицы на m разрядов вправо в каждом цикле осуществляется потому, что число разрядов сдёигового регистра 8 меньше числа тактов в цикле на т. Например, если число тактов в цикле составляет 13, как в рассмотренных числовых примерах, то при m 4 сдвиговый регистр 8 содержит 9 двоичных разрядов. Перед началом .nep-f. вого цикла этот регистр будет иметь состояние 10000000. После вьшолнения 13 сдвигов вправо (в 9 такте единица из младшего iэaзpядa переписывается в старший) получим 000010000, т.е. произошло смещение единицы на 4 разряда вправо. Для построения операционной части предлагаемого устройства требует ся (т + 1)-разрядный сумматор-вычитатель 2, (т + ,1)-разрядный регистр 3 константы и регистр 1, содержащий km разрядов. Можно считать, что сложность одного разряда сумматора примерно равна сложности одного раз ряда регистра. Тогда сложность пред лагаемого устройства в условных еди ницах (в числе разрядов регистров и сумматора) можно представить как Кпред (m+1)+(m+1)+km m(k + 2) + 2. С учетом тгго, что m 1о§2р, где р - основание системы счисления в которую осуществляется преобразование, получается iog2p (К + 2) + 2. Операционная часть базового устройства содержит умножитель . на константу, вычитатель и регистр чис ла. Вычитатель имеет два р-ичньк ра ряда. Для построения каждого разряда такого вычитателя требуется примерно 2 двоичных одноразрядньгх сумм торов, т.е. сложность нычитателя в условных единицах составляет пример 4т. Умножитель содержит по крайней мере один сумматор на два р-ичных разряда. Примем его сложность за 4т Регистр числа в базовом устройстве должен иметь- количество разрядов, равное числу цифр в преобразуемом числе, причем кажд,ый разряд имеет длину m logjpj бит, где р - осно вание той системы счисления, в которую осуществляется перевод исходного числа. Таким образом, для базо го устройства получается m(n + 8) 4т + 4ш + nm iogapCCm + 8), . где n - число разрядов преобразуемо числа. 79 8 . Очевидно, что сложность базового устройства увеличивается с увеличением разрядности преобразуемого числа, причем независимо от величины основания исходной системы счисления. В связи с перевод двоичных чисел в р-ичные в базовом устройстве- более эффekтивнo осуществляется через систему счисления с .основанием 2, где S - целое число. Например, при переводе 32-разрядных двоичных чисел в десятичные сложность базового устройства будет составлятьNBq- log2p(n. + 8) .. , . iog2lO(32 + 8) 4-40 160. Если же 32-разрядное двоичное число разбить на триады, то получим 11разрядное число в системе счисления с основанием 8. В этом случае сложность базового устройства определяется так: NBO liogjPLCn + 8) log2lOt(11 + 8) 4,. 19 76.Если перевод 32-разрядных двоичных чисел в 8-разрядные десятичные осуществляется с помощью предлагаемого устройства, т.е. сложность будет определяться так: NnpeA. iog2pC(k + 2) 3 iog,1o(8 + 2) + 2 440 + 2 42. Таким образом, по сравнению с наиболее эффективным вариантом базового устройства предлагаемое устройство при переводе двоичных чисел в деся-. тичные позволяет уменьшить объем оборудования 1,8 раз. В базовом устройстве для изменения основания системы счисления, в которую осуществляется перевод исходных чисел, необходимо заменить блоки умножителя и вычитателя или заменить их внутреннюю организацию. В предлагаемом преобразователе в этом нет необходимости.

Фиг.2

N

N 5

Q

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь @ -ичного позиционного кода в двоичный код | 1983 |

|

SU1115045A1 |

| Преобразователь двоичного кода в двоично-десятичный код | 1978 |

|

SU742923A1 |

| Устройство для нормализации чисел | 1980 |

|

SU953636A1 |

| Устройство для преобразования избыточного двоичного кода в код со смешанным основанием | 1975 |

|

SU618737A1 |

| Устройство для умножения чисел с плавающей запятой | 1985 |

|

SU1280624A1 |

| Устройство для умножения | 1981 |

|

SU1018115A1 |

| Преобразователь кодов | 1973 |

|

SU467343A1 |

| Преобразователь кода системы остаточных классов в позиционный код | 1986 |

|

SU1388997A1 |

| Устройство для извлечения квадратного корня с перестраиваемым основанием системы счисления | 1985 |

|

SU1363204A1 |

| Преобразователь двоичного кода в позиционный код со смешанным основанием | 1980 |

|

SU960792A1 |

ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНОГО КОДА В р-ИЧНЫЙ ПОЗИЦИОННЬЙ КОД, содержащий сдвиговый регистр, сумматор-вычитатель и блок управления, выход сдвига которого соединен с входом управления сдвигом сдвигового регистра,выход старшего разряда которого соединен с входом младшего разряда регистра сдвига, выход записи блока управления соединен с входом управления записью сдвигового регистра, (т + 1) старших разрядов которого (т 3log2p) сое-, динены с первой группой входов сумматора-вычитателя, выходы которого . соединены с входами (т + 1) старших разрядов сдвигового регистра, отличающийся тем, что, с . целью упрощения преобразователя и расширения класса решаемых задач путем обеспечения возможности изменения основания системы счисления, он содер5;сит регистр константы, выходы которого соединены с второй группой входов сумматора-вычитателя, вход задания режима которого соединен с выходом знака блока управления, входкоторого соединен с выходом старшего разряда сдвигового регистра, а блок управления содержит распределитель импульсов, два триггера, два элемента И, два элемента запрета, элемент ИЛИ и сдвиговьй регистр, выход младшего разряда которого подключен к входу его старшего разряда, к информационному входу первого триггера, к первому входу первого элемента И и запрещающему входу первого элемента запрета, выход которого является вьгходом сдвига блока управления, выход записи которого соединен с выходом элемента ИЛИ, первый вход которого соединен с выходом первого элемента (Л И и запрещающим входом второго элемента запрета, выход которого является выходом знака блока управления, вход которого соединен с информационным-входом второго триггера, которого соединен с входом второго элемента запрета, а еднничшлй вход соединен с первьм выходом распреОд делителя импульсов и с нулевым вхоСО СО дом первого триггера, синхровход которого соединен с вторым выходом. распределителя импульсов, с синхровходами второго триггера и сдвигового регистра, с входом первого элемента запрета и с вторым входом .первого элемента И, третий выход распределителя импульсов соединен с первым входом второго элемента И, второй вход которогосоединен с инверсным выходом первого триггера, а выход второго элемента И соединен-с вторым входом элемента ИЛИ.

eo

§

X

| Патент США № 4069478, кл | |||

| Способ отопления гретым воздухом | 1922 |

|

SU340A1 |

| Чугунный экономайзер с вертикально-расположенными трубами с поперечными ребрами | 1911 |

|

SU1978A1 |

| Преобразователь кода в код с большим основанием | 1973 |

|

SU485444A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-06-23—Публикация

1983-05-27—Подача