Изобретение относится к вычислительной технике и может быть использовано для построения преобразователей кодов как правильных и смешанных дробей, так и.целых чисел.5

Цель изобретения - повышение быстродействия преобразователя.

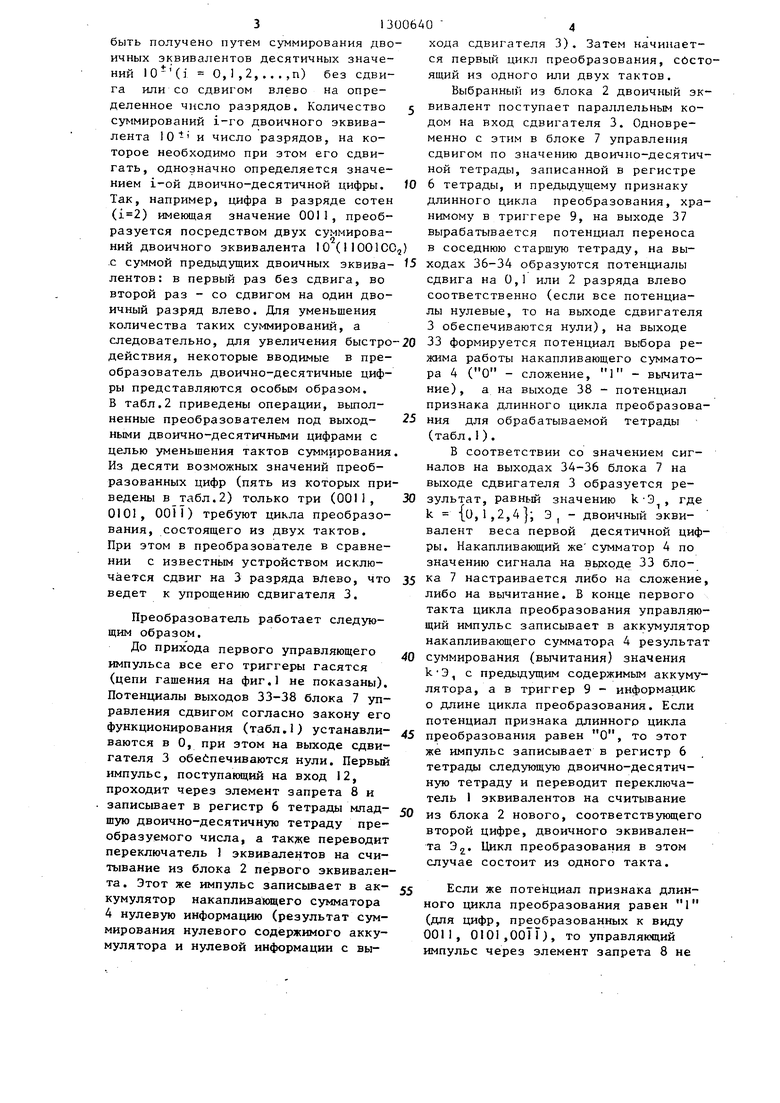

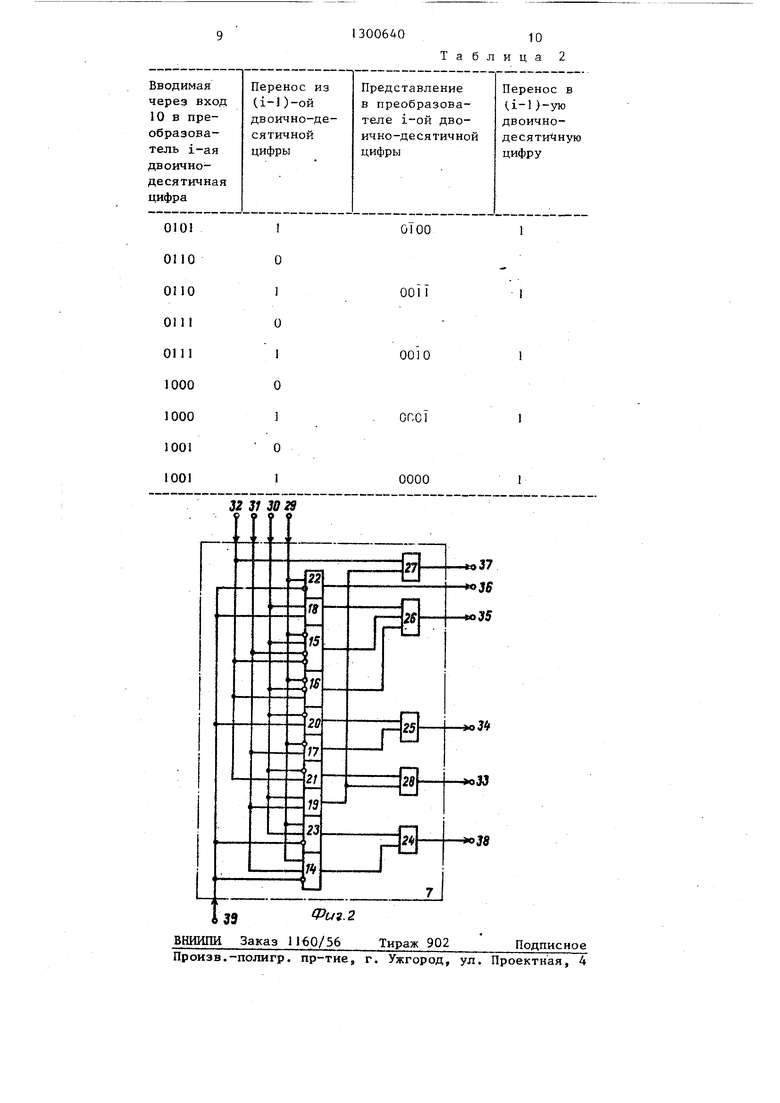

На фиг.1 приведена структурная схема предлагаемого преобразователя двоично-десятичного кода в двоич- fO ный; на фиг,2 - функциональная схема блока управления сдвигом.

Преобразователь двоично-десятичного кода в двоичный содержит (фиг. I) переключатель 1 эквивалентов, блок IS 2 хранения эквивалентов, сдвигатель 3, накапливающий сумматор 4, сумматор 5, регистр 6 тетрады, блок 7 управления сдвигом, элемент запрета 8, триггер 9, информационный 20 вход 10 преобразователя соединен со входами сумматора 5, выход 11 преобразователя является выходом на- капливакнцего сумматора 4, тактовый вход 12 преобразователя соединен с синхровходами накапливающего сумматора 4, триггера 9 и входом элемента запрета 8,

Элементы 8 и 9 с соответствутощими связями образуют блок управления 13,

Блок 7 управления сдвигом содержит (фиг,2) элементы запрета t4-l7, элементы И 18 и 19, элементы запрета 20-23 и элементы ИЛИ 24-28, Информационные входы 29-32 соединены с вхо- 35 дами элементов запрета 14-17 и 20-23 и элементов И 18-19. Выходы элементов ИЛИ 24-28 и элемента запрета 22 являются выходами 33-38 блока управления сдвигом, вход 39 признака длин- 0 ного цикла преобразования которого соединен со входами элементов запрета 14, 20, 22, 23 и элемента И 18.

Переключатель I эквивалентов формирует адреса, по которым расположе- 5 ны двоичные эквиваленты десятичных значений 10(i - целое положительное число) в блоке 2 хранения эквивалентов, и может быть реализован на

25

30

или 2 разряда влево или вырабатывает на выходе нули.Сдвигатель может входить, например в арифметико-логическое устройство ЭВМ, тогда не требуется дополнительное оборудование для его реализации.

Накапливающий сумматор 4 производит суммирование Сдвинутого или переданного транзитом через сдвигатель. 3 двоичного эквивалента с ранее накопленным результатом и запоминает образующуюся при этом сумму в аккумуляторе ,

Сумматор 5 осуществляет суммирование значения переноса из преобразуемой двоично-десятичной цифры, сформированного на выходе блока 7, и значения соседней старшей цифры, поступающей через вход 10 преобразователя,

Регистр 6 тетрады предназначен для запоминания значения двоично-десятичной цифры на время цикла ее преобразования.

Блок 7 управления сдвигом вырабатывает по значениям двоичных разрядов а а а.а преобразуемой двоично- десятичной цифры и по значению призна ка длинного цикла преобразования (ПДЦП) потенциал переноса (П) в сосед нюю старшую десятичную цифру исходного операнда, управляющие потенциалы для сдвигателя 3 (сдвиг на О,1 или 2 двоичных разряда влево), потенциал выбора режима .для накапливающего сумматора 4 (сложение + или вычитание -), а также признак длинного цикла преобразования (ПДЦП) данной двоично-десятичной цифры. Данные, приведенные в табл.1 истинности, полностью описывают закон функционирования блока 7,

Блок I3 управления запоминает значение признака длинного цикла преобразования преобразуемой двоично-десятичной цифры и в случае его равенства единице (случай длинного преобразования) запрещает поступление 1 1пульса с тактового входа 12 преобразователя на синхровходы регистра

двухтактном синхроином двоичном счет- 50 6 тетрады и переключателя I эквивачике,лентов, состояние которых при этом

Блок 2 хранения эквивалентов сохраняется неизменш 1м до завершения

предназначен для хранения двоичных цикла преобразования данной десятичэквиовалентов 10-, количество которых ной цифры,

В основу предлагаемого преобразователя двоично-десятичного кода в двоичный положен следующий принцип. Двоичное значение преобразуемого п- разрядного десятичного числа может

определяется разрлдностью преобразуе- 55 мого десятичного числа.

Сдвигатель 3 осуществляет сдвиг постзшакщего па его вход с выхода блока 2 двоичного эквивалента на О,1

S 0

5 0

5

5

0

или 2 разряда влево или вырабатывает на выходе нули.Сдвигатель может входить, например, в арифметико-логическое устройство ЭВМ, тогда не требуется дополнительное оборудование для его реализации.

Накапливающий сумматор 4 производит суммирование Сдвинутого или переданного транзитом через сдвигатель. 3 двоичного эквивалента с ранее накопленным результатом и запоминает образующуюся при этом сумму в аккумуляторе ,

Сумматор 5 осуществляет суммирование значения переноса из преобразуемой двоично-десятичной цифры, сформированного на выходе блока 7, и значения соседней старшей цифры, поступающей через вход 10 преобразователя,

Регистр 6 тетрады предназначен для запоминания значения двоично-десятичной цифры на время цикла ее преобразования.

Блок 7 управления сдвигом вырабатывает по значениям двоичных разрядов а а а.а преобразуемой двоично- десятичной цифры и по значению признака длинного цикла преобразования (ПДЦП) потенциал переноса (П) в соседнюю старшую десятичную цифру исходного операнда, управляющие потенциалы для сдвигателя 3 (сдвиг на О,1 или 2 двоичных разряда влево), потенциал выбора режима .для накапливающего сумматора 4 (сложение + или вычитание -), а также признак длинного цикла преобразования (ПДЦП) данной двоично-десятичной цифры. Данные, приведенные в табл.1 истинности, полностью описывают закон функционирования блока 7,

Блок I3 управления запоминает значение признака длинного цикла преобразования преобразуемой двоично-десятичной цифры и в случае его равенства единице (случай длинного преобразования) запрещает поступление 1 1пульса с тактового входа 12 преобразователя на синхровходы регистра

31300640 -4

быть получено путем суммирования дво- хода сдвигателя 3). Затем начинаетэквивалентов десятичных значе- ся первый цикл преобразования, состоим ных

НИИ (i 0,1,2,...,п) без сдвига или со сдвигом влево на определенное число разрядов. Количество суммирований i-ro двоичного эквивалента 10- и число разрядов, на которое необходимо при этом его сдвигать, однозначно определяется значением i-ой двоично-десятичной цифры. Так, например, цифра в разряде сотен () имеющая значение ООП, преобящий из одного или двух тактов.

Выбранный из блока 2 двоичный эк5 вивалент поступает параллельным кодом на вход сдвигателя 3. Одновременно с этим в блоке 7 управления сдвигом по значению двоично-десятичной тетрады, записанной в регистре

W

6 тетрады, и предыдущему признаку длинного цикла преобразования, хранимому в триггере 9, на выходе 37 вырабатывается потенциал переноса в соседнюю старшую тетраду, на вы- -с суммой предьщутцих двоичных эквива- t5 ходах 36-34 образуются потенциалы лентов: в первый раз без сдвига, во второй раз - со сдвигом на один двоичный разряд влево. Для уменьщения

разуется посредством двух суммирований двоичного эквивалента lOCllOOlCO,)

сдвига на 0,1 или 2 разряда влево соответственно (если все потенциалы нулевые, то на выходе сдвигателя 3 обеспечиваются нули), на выходе

количества таких суммирований, а

следовательно, для увеличения быстро-20 33 формируется потенциал выбора ре

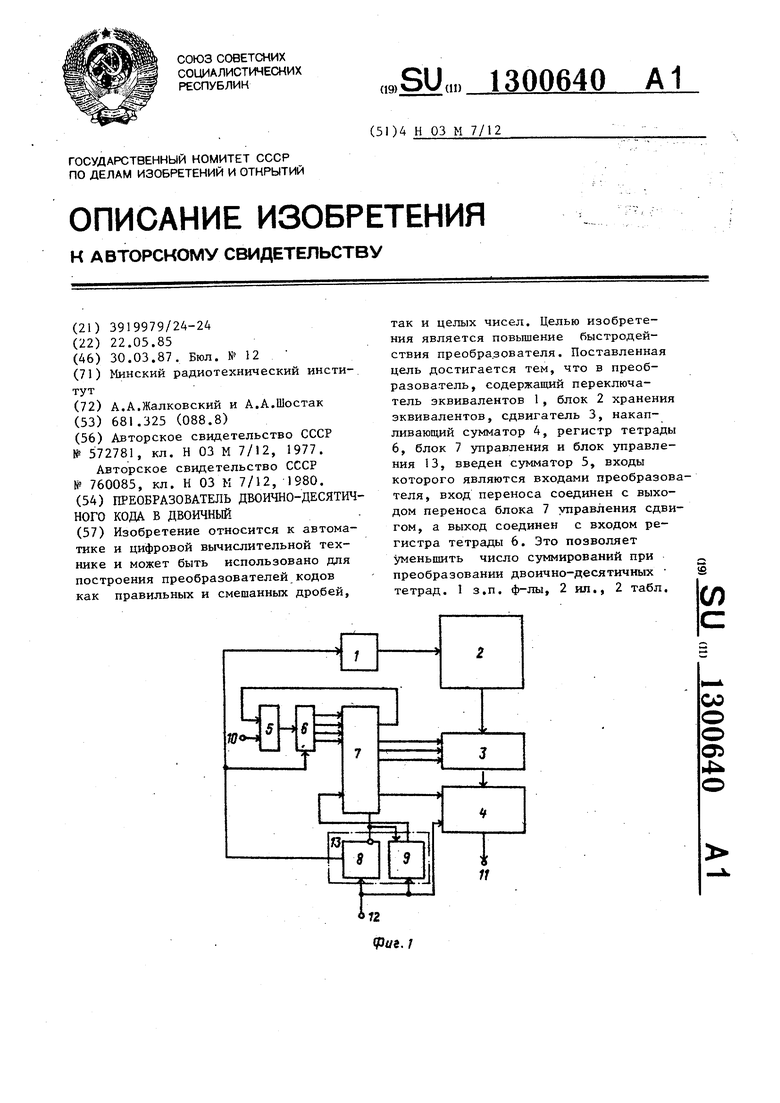

действия, некоторые вводимые в преобразователь двоично-десятичные цифры представляются особым образом. В табл.2 приведены операции, выполненные преобразователем под выходными двоично-десятичными цифрами с целью уменьшения тактов суммирования Из десяти возможных значений преобразованных цифр (пять из которых приведены в табл.2) только три (ООП, 0101, ООП) требуют цикла преобразования, состоящего из двух тактов. При этом в преобразователе в сравнении с известным устройством исключается сдвиг на 3 разряда влево, что ведет к упрощению сдвигателя 3.

Преобразователь работает следующим образом.

До прих ода первого управляющего импульса все его триггеры гасятся (цепи гашения на фиг.1 не показаны). Потенциалы выходов 33-38 блока 7 управления сдвигом согласно закону его функционирования (табл.1) устанавливаются в О, при этом на выходе сдвигателя 3 обеспечиваются нули. Первый импульс, поступающий на вход 12, проходит через элемент запрета 8 и записывает в регистр 6 тетрады младшую двоично-десятичную тетраду преобразуемого числа, а также переводит переключатель 1 эквивалентов на считывание из блока 2 первого эквивалента. Этот же импульс записьшает в аккумулятор накапливающего сумматора 4 нулевую информацию (результат суммирования нулевого содержимого аккумулятора и нулевой информации с выящий из одного или двух тактов.

Выбранный из блока 2 двоичный эквивалент поступает параллельным кодом на вход сдвигателя 3. Одновременно с этим в блоке 7 управления сдвигом по значению двоично-десятичной тетрады, записанной в регистре

6 тетрады, и предыдущему признаку длинного цикла преобразования, хранимому в триггере 9, на выходе 37 вырабатывается потенциал переноса в соседнюю старшую тетраду, на вы- ходах 36-34 образуются потенциалы

6 тетрады, и предыдущему признаку длинного цикла преобразования, хранимому в триггере 9, на выходе 37 вырабатывается потенциал переноса в соседнюю старшую тетраду, на вы- ходах 36-34 образуются потенциалы

сдвига на 0,1 или 2 разряда влево соответственно (если все потенциалы нулевые, то на выходе сдвигателя 3 обеспечиваются нули), на выходе

5

5

жима работы накапливающего сумматора 4 (О - сложение, 1 - вьмита- ние), а на выходе 38 - потенциал признака длинного цикла преобразования для обрабатываемой тетрады (табл.1).

В соответствии со значением сигналов на выходах 34-36 блока 7 на выходе сдвигателя 3 образуется ре- 0 зультат, равный значению k-Э , где

{ д- 0,1,2, Э, - двоичный эквивалент веса первой десятичной цифры. Накапливающий же сумматор 4 по значению сигнала на вькоде 33 блока 7 настраивается либо на сложение, либо на вычитание. В конце первого такта цикла преобразования управляющий импульс записывает в аккумулятор накапливающего сумматора 4 результат 0 суммирования (вычитания) значения kЭ, с предыдущим содержимым аккумулятора, а в триггер 9 - информацию о длине цикла преобразования. Если потенциал признака длинного цикла 5 преобразования равен О, то этот же импульс записывает в регистр 6 тетрады следующую двоично-десятичную тетраду и переводит переключатель 1 эквивалентов на считывание 0 из блока 2 нового, соответствующего второй цифре, двоичного эквивалента Э„. Цикл преобразования в этом

случае состоит из одного такта.

Если же потенциал признака длинного цикла преобразования равен 1 (для цифр, преобразованных к виду ООП, 0101,ООТГ), то управляющий импульс через элемент запрета 8 не

5 1300640

проходит. При этом сохраняются состояния регистра 6 тетрады и переключателя 1 эквивалентов, что делает возможным повторное суммирование (вычитание) во втором такте цикла преоб- 5 разования выбранного эквивалента Э при другом значении параметра k сдвига. В блоке 7 вырабатывается новая комбинация потенциалов (на выходе 38 потенциал в этом случае fO всегда равен О).

Следующий импульс записывает в аккумулятор накапливающего сумматора 4 результат повторного суммирования (вычитания), обнуляет триггер 9 )5 и записывает в регистр 6 тетрады вторую двоично-десятичную тетраду, а также переводит переключатель 1 эквивалентов на считывание из блока 2 соответствующего двоичного эквива- 20 лента Э-. Цикл преобразования состоит в этом случае из двух тактов.

Вслед за первым десятичньш разрядом точно так же за один цикл, состоящий из одного или двух тактов, проис-25 ходит преобразование каждого последующего двоично-десятичного разряда исходного числа. При этом для каждого нового цикла считывается.кз блока 2

ционные входы накапливающего сумм ра соединены с выходами сдвигател информационные входы которого сое нены с выходами блока хранения эк валентов, входы которого соедине с выходами переключателя эквивале тов, отличающийся тем что, с целью повышения быстродейс вия, в него введен сумматор, а б управления содержит триггер и эл мент запрета, выход которого соед нен с синхровходами переключателя эквивалентов и регистра тетрады, формационные входы которого соеди ны с выходами сумматора, вход пер са которого соединен с выходом п реноса блока управления сдвигом, рядные выходы которого соединены входами кода сдвига сдвигателя, и формационные входы сумматора сое нены с информационным входом прео разователя, тактовый вход которог соединен с синхровходами триггера накапливающего сумматора и с прям входом элемента запрета, инверсны Вход которого соединен с выходом признака длинной операции блока у равления сдвигом и с управляющим входом триггера, выход которого с

очередной эквивалент 10- . Так про- 30 единен с входом признака длинной

операции блока управления сдвигом

2. Преобразователь по п.1, о личающийся тем, что в

должается до тех пор, пока не будут преобразованы все двоично-десятичные разряды исходного числа, а в накапливающем сумматоре 4 не сформируется искомое двоичное число, которое пода- 35 блок управления сдвигом содержит ется на выход П преобразователя. два элемента И, восемь элементов Поскольку из самой старшей тетрады возможен перенос, то необходим дополнительный такт для выборки эквивален40

та Э и суммирования его (если перенос равен 1) с ранее накопленным результатом.

запрета и пять элементов ИЛИ, пр чем прямой вход первого, первые мые входы второго и третьего эл ментов запрета, первые инверсны входы четвертого и пятого и инв ный вход шестого элементов запре соединены с информационным входом первого разряда блока управления

Формула изобретения

1. Преобразователь двоично-десятичного кода в двоичный, содержащий переключатель эквивалентов, блок хранения эквивалентов, сдвигатель, накапливающий сумматор, регистр тетрады, блок управления и блок управления сдвигом, информационные входы которого соединены с соответствующими выходами регистра тетрады, выход

выбора режима блока управления сдви- 55 мента запрета, второй прямой вход

гом соединен с управляющим входом сложения-вычитания накапливающего сумматора, выход которого является выходом преобразователя, а информационные входы накапливающего сумматора соединены с выходами сдвигателя, информационные входы которого соединены с выходами блока хранения эквивалентов, входы которого соединены с выходами переключателя эквивален- тов, отличающийся тем, что, с целью повышения быстродействия, в него введен сумматор, а блок управления содержит триггер и элемент запрета, выход которого соединен с синхровходами переключателя эквивалентов и регистра тетрады, информационные входы которого соединены с выходами сумматора, вход переноса которого соединен с выходом переноса блока управления сдвигом, разрядные выходы которого соединены с входами кода сдвига сдвигателя, информационные входы сумматора соединены с информационным входом преобразователя, тактовый вход которого соединен с синхровходами триггера, накапливающего сумматора и с прямым входом элемента запрета, инверсный Вход которого соединен с выходом признака длинной операции блока управления сдвигом и с управляющим входом триггера, выход которого сооперации блока управления сдвигом.

блок управления сдвигом содержит два элемента И, восемь элементов

2. Преобразователь по п.1, отличающийся тем, что в нем

блок управления сдвигом содержит два элемента И, восемь элементов

блок управления сдвигом содержит два элемента И, восемь элементов

запрета и пять элементов ИЛИ, причем прямой вход первого, первые прямые входы второго и третьего элементов запрета, первые инверсные входы четвертого и пятого и инверсный вход шестого элементов запрета соединены с информационным входом первого разряда блока управления

сдвигом, информационный вход второго разряда которого соединен с первыми входами первого и второго элементов И, с вторым прямым входом второго и первым прямым входом четверТого элементов запрета, с инверсными входами седьмого и восьмого элементов запрета, с вторым инверсным входом пятого элемента запрета, второй инверсный вход четвертого элетретьего элемента запрета, второй вход второго элемента И и прямой вход щестого элемента запрета соединены с информационным входом третьего разряда блока управления сдвигом, информационный вход четвертого разряда которого соединен с прямыми вхо- дами пятого и восьмого элементов запрета, с третьим инверсным входом четвертого элемента, запрета и с первым .входом первого элемента ИЛИ, второй вход которого соединен с выходом второго элемента И и с первым входом второго элемента ИЛИ, второй вход ко- торого соединен с выходом восьмого элемента запрета, вход признака длинной операции блока управления сдвигом соединен с инверсными входами первого, второго и третьего элемен- тов запрета, с прямым входом седьмого элемента запрета и с вторым входом первого элемента И, выходы второго и третьего элементов запрета соответственно соединены с первым и

вторьт входами третьего элемента ИЛИ, выход которого является выходом признака длинной операции блока управления сдвигом, выходы шестого и седьмого элементов запрета соединены соответственно с первым и вторым входами четвертого элемента ИЛИ, выход первого элемента И и выходы четвертого и пятого элементов запрета соединены соответственно с первья 1, вторым и третьим входами пятого элемента ИЛИ, выходы четвертого и пятого элементов ИЛИ и выход первого элемента запрета являются выходами соответственно первого, второго и третьего разрядов блока управления сдвигом, выходы первого и второго элементов ИЛИ являются выходами соответственно переноса и выбора режима блока управления сдвигом.

Таблица 1

о 1

о I

о I

о 1

о 1

о о о о

о о о о о о I 1 1 г о о о 1

о о о 1

о I

о J

о о о о о о

Перенос из (1-)-ой двоично-десятичнойцифры

1 о

о 1

о

} о

1

ВНИИПИ Заказ 1160/56 Тираж 902

Произв.-полигр. пр-тие, г. Ужгород, ул. Проектная, 4

Перенос в (.1-1 )-ую двоично- десятичную цифру

0100

001

0010

ОГ,С1

0000

Подписное

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоично-десятичного кода в двоичный | 1985 |

|

SU1283979A1 |

| Преобразователь двоично-десятичногоКОдА B дВОичНый | 1979 |

|

SU798800A1 |

| Преобразователь двоично-десятичных чисел в двоичные | 1976 |

|

SU572781A1 |

| Преобразователь двоичного кода в двоично-десятичный и обратно | 1975 |

|

SU708344A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1984 |

|

SU1221757A1 |

| Преобразователь двоично-десятичной дроби в двоичную дробь | 1979 |

|

SU860053A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1985 |

|

SU1283978A1 |

| Преобразователь двоичнодесятичного кода в двоичный | 1977 |

|

SU656052A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1985 |

|

SU1285604A1 |

| Преобразователь двоичных чисел в двоично-десятичные числа | 1980 |

|

SU941990A1 |

Изобретение относится к автоматике и цифровой вычислительной технике и может быть использовано для построения преобразователей кодов как правильных и смешанных дробей. так и целых чисел. Целью изобретения является повьшение быстродействия преобра.зователя. Поставленная цель достигается тем, что в преобразователь, содержащий переключатель эквивалентов 1, блок 2 хранения эквивалентов, сдвигатель 3, накапливающий сумматор 4, регистр тетрады 6, блок 7 управления и блок управления 13, введен сумматор 5, входы которого являются входами преобразователя, вход переноса соединен с выходом переноса блока 7 управления сдвигом, а выход соединен с входом регистра тетрады 6. Это позволяет уменьшить число суммирований при преобразовании двоично-десятичных тетрад. 1 з.п. ф-лы, 2 ил., 2 табл. ю (Л О5 4

| Преобразователь двоично-десятичных чисел в двоичные | 1976 |

|

SU572781A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Авторское свидетельство СССР № 760085, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-03-30—Публикация

1985-05-22—Подача