вого носа триггера является выходом пере- триггеров являются входами синхрониблока коррекции, R и С -входы зации блока коррекции. 1140)12

| название | год | авторы | номер документа |

|---|---|---|---|

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| Устройство для умножения | 1987 |

|

SU1495785A1 |

| Матричное устройство для умножения | 1985 |

|

SU1267408A1 |

| Преобразователь двоичного кода в двоично-десятично-шестидесятиричный код | 1978 |

|

SU767749A1 |

| Двоично-десятичное арифметико-логическое устройство накапливающего типа | 1981 |

|

SU1024904A1 |

| Арифметическое устройство | 1971 |

|

SU522497A1 |

| Матричное устройство для умножения двоичных и десятичных чисел | 1983 |

|

SU1200282A1 |

| Устройство для вычисления модуля комплексного числа | 1990 |

|

SU1753472A1 |

| СПОСОБ И УСТРОЙСТВО СУММИРОВАНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ ЧИСЕЛ | 2007 |

|

RU2402803C2 |

СУММИРУЮЩЕЕ УСТРОЙСТВО С КОНТРОЛЕМ, содержащее сумматор, регистр, блок коррекции, блок памяти и первый элемент И, причем информационный вход устройства подключен к первому информационному входу сумматора, выход которого связан с входом регистра, выходы регистра соединены с соответствующими информационными входами блока коррекции, выход которого подключен к информационному входу блока памяти, выходы блока памяти связаны с первым входом первого элемента И, второй вход которого соединен с первым управляющим входом сумматора и входом разрешения суммирования устройства, отличающееся тем, что, с целью повьппения достоверности результатов вычислений, в него введены второй и третий элементы И и элементы И.ПИ, причем первый вход второго элемента- И связан с синхронизирующим входом устройства, второй вход второго элемента И соединен с выходом сумматора, первый вход третьего элемента И подключен к входу разрешения контроля устройства. второй вход третьего элемента И связан с выходом блока коррекции, выход третьего элемента И соединен с первым входом элемента ИЛИ, второй вход которого соединен с выходом первого элемента И, выход элемента ИЛИ связан с вторым управляющим входом сумматора, ВЫХ.ОД второго элемента И является выходом устройства, выход переноса соединен с вторым входом блока коррекции, выход переноса блока 1соррекции связан с вторым информационным входом сумматора, блок коррекции содержит элемент 3 И-ИЛИ, два триггера, элемент И и двоичный сумматор, причем первый и второй входы , liepBoro элемента И элемента 3 И-ИЛИ сое(Л динены с соответствующими выходами реС гистра, первый и второй входы второго элемента И элемента 3 И-ИЛИ связаны соответственно с вторым входом первого элемента И элемента ЗИ-ИЛИ и соответствующим выходом регистра, первый и второй входы третьего элемента И элемента ЗИ-ИЛИ подключены к выходу переноса сумматора устройства, выход элемента ЗИ-ИЛИ подключен к р -входу первого триггера, выход которого соединен с первым входом элемента И, второй вход которого является входом корректирующего кода, первый вход двоичного сумматора связан с соответствующим выходом регистра, а второй вход подключен к выходу элемента И, вход переноса двоичного сумматора соединен с выходом второго триггер;.. В -вход которого связан с первьп-: ЬЬЕХОДОМ двоичного сумматора, второй выход которого является выходом суммы блока коррекции, выход пер

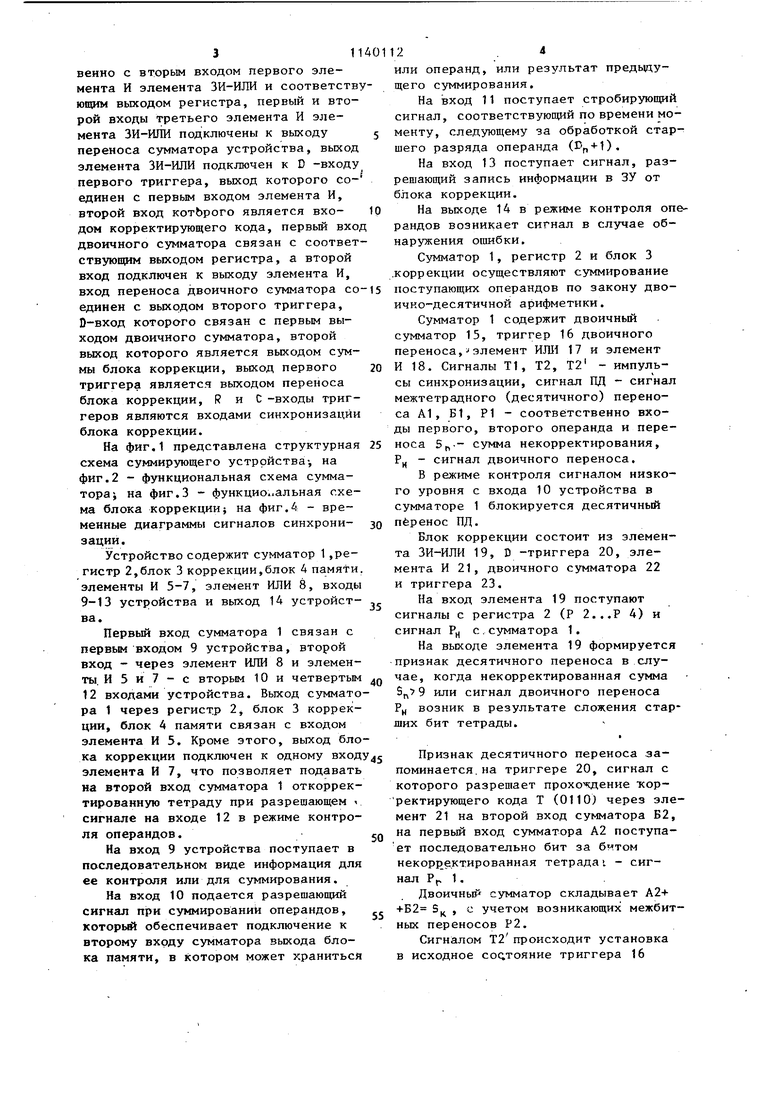

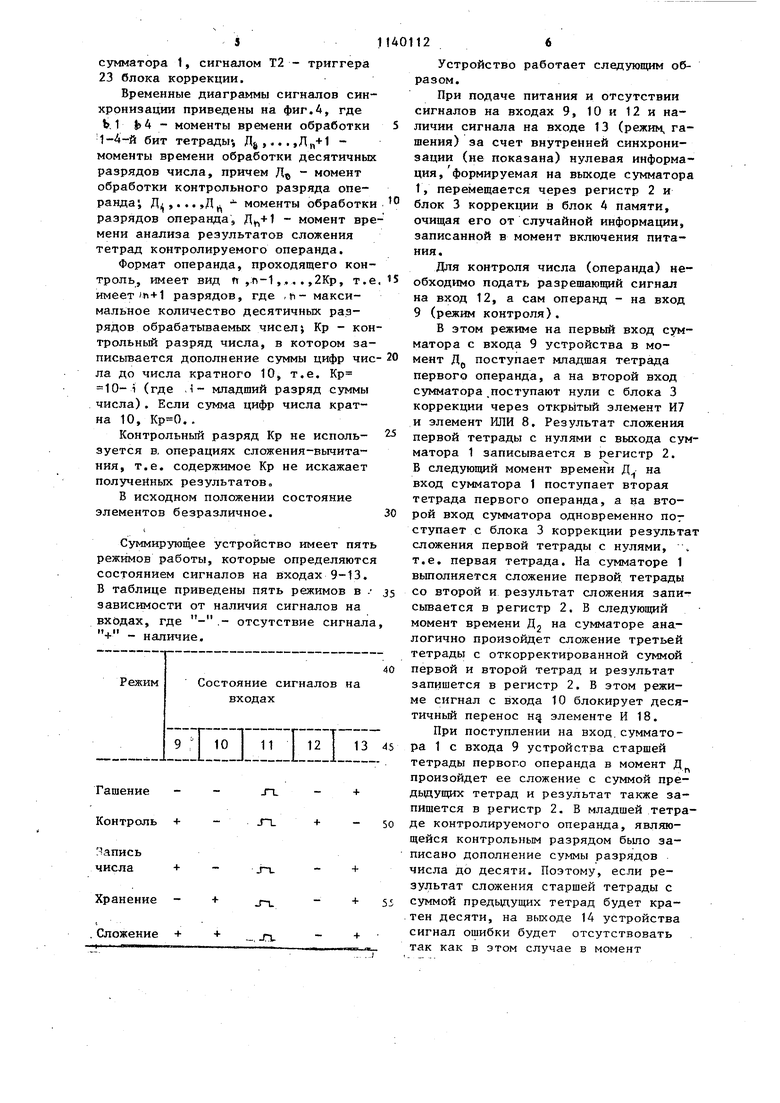

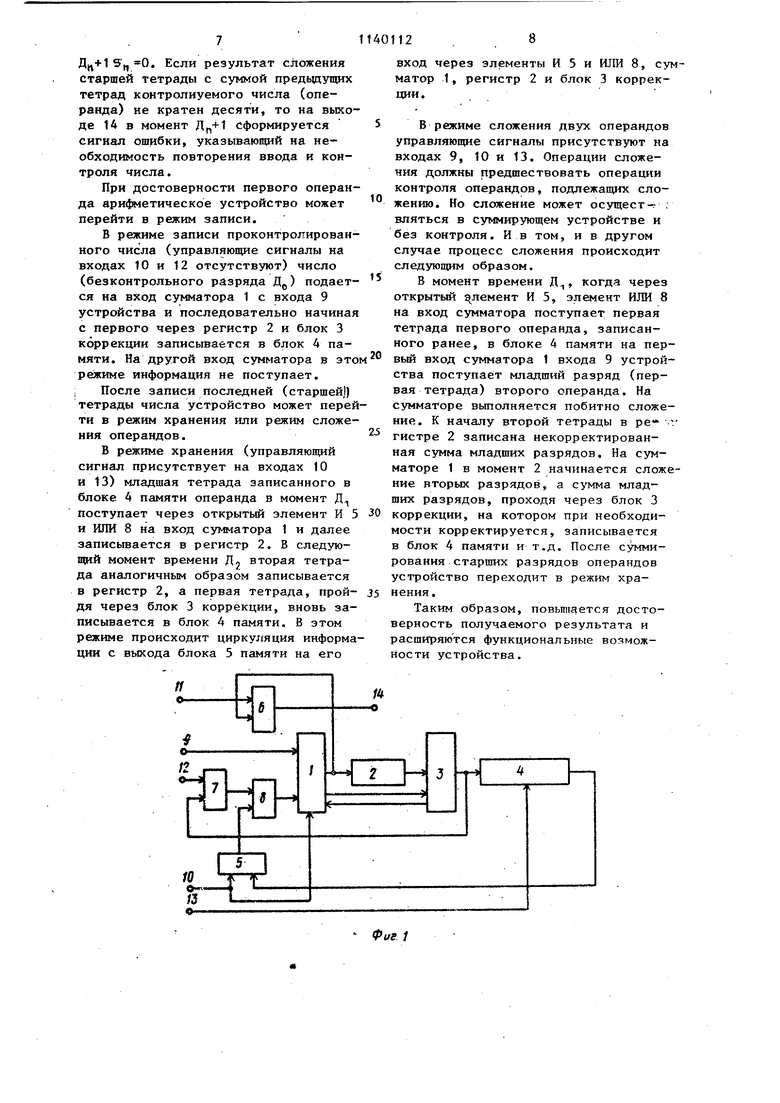

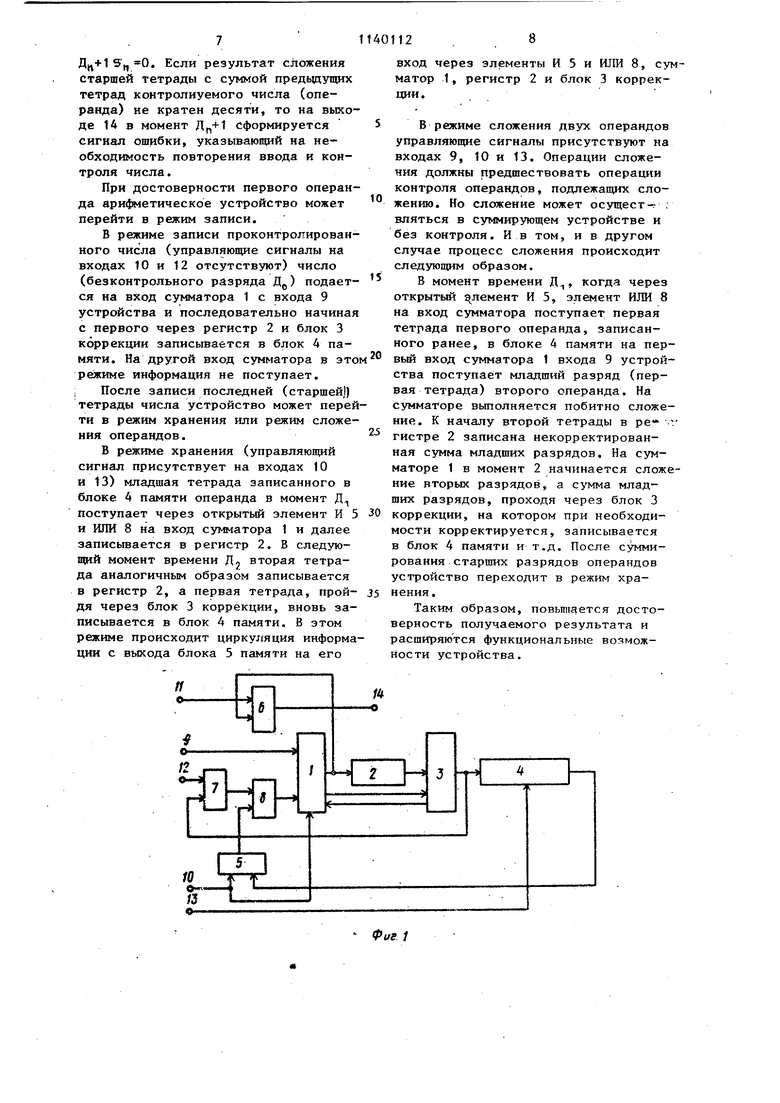

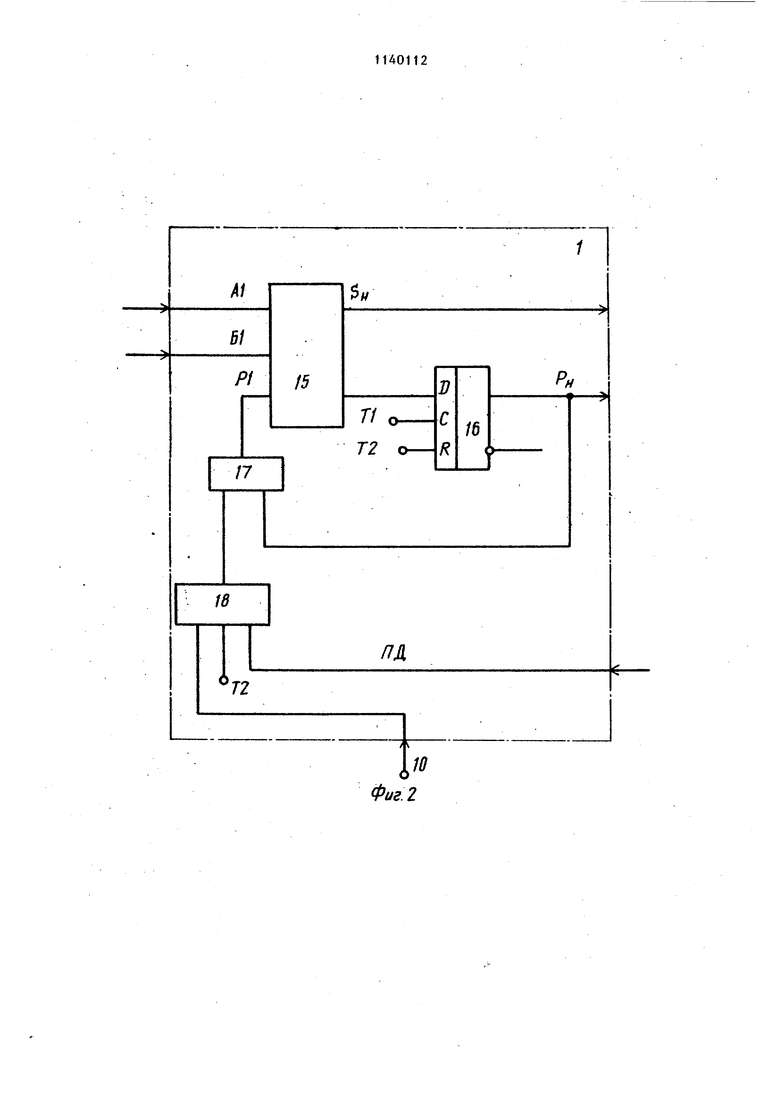

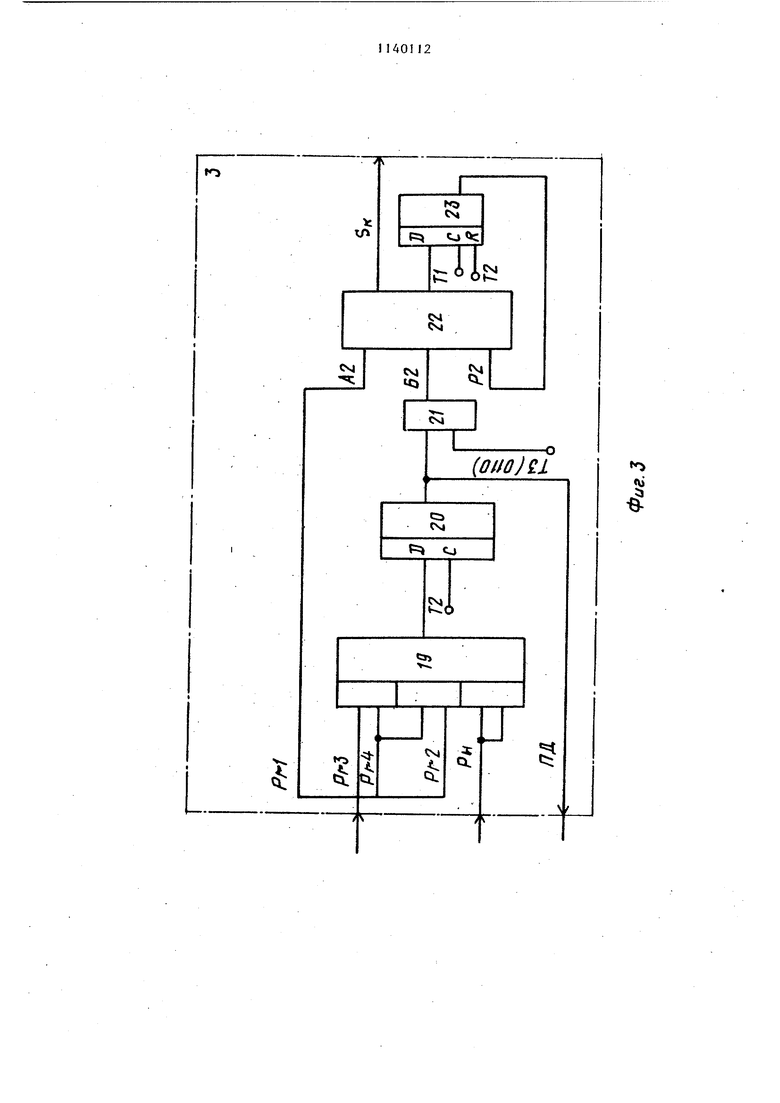

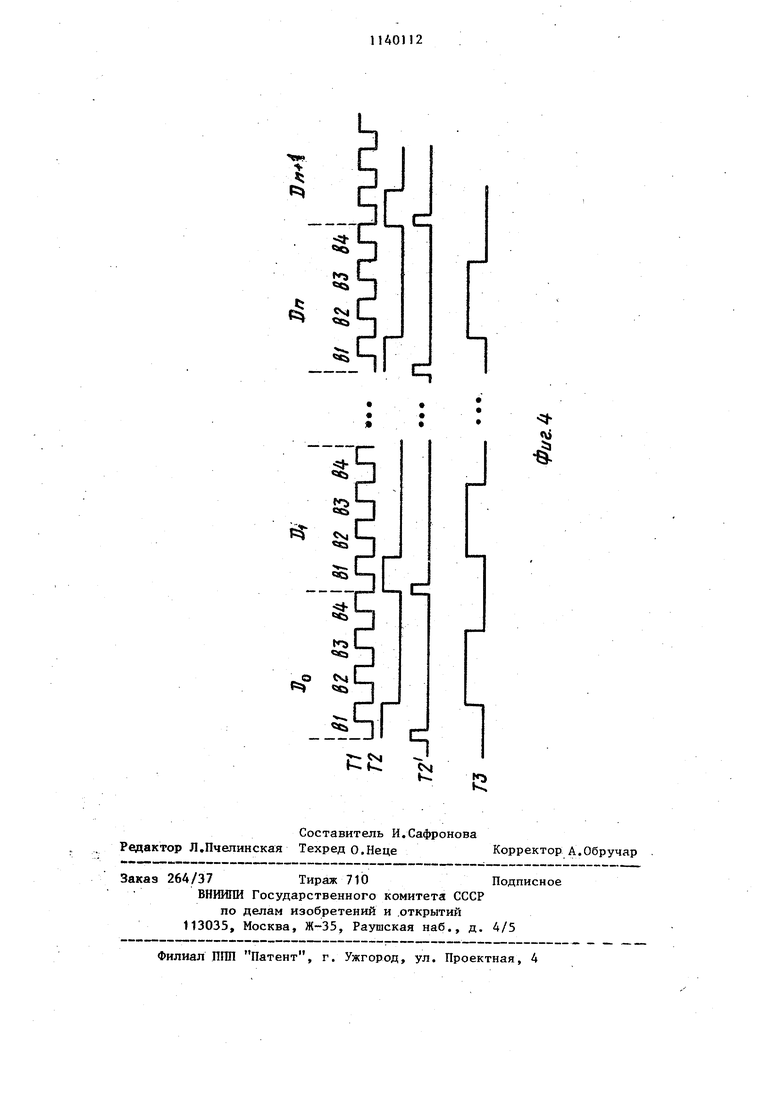

Изобретение относится к вычислительной технике, в частности к электронным клавишньм вычислительным машинам, и может быть/испоЛьзовано в регистраторах и концентраторах инфор мации, работающих с числами в двоично-десятичной системе счисления. Известно арифметическое устройство, содержащее сумматор, регистр кор рекции, схему коррекции, многоразрадный регистр, триггер управления, схемы И и ШЩ и управляюище цепи ll Недостатком указанного устройства является наличие достаточно большого количества функциональных узлов. Наиболее близким к предлагаемому является арифметическое устройство, содержащее регистр результата из h тетрад, сумматор, блок коррекции и злемент И, причем один вход устройст ва черев сумматор, первую тетраду регистра, блок коррекции и регистр результата связан с первьм входом элемента И, подключенный к второму входу сумматора, второй вход элемента И связан с вторым входом устройства. При выполнении арифметических операций на входы сумматора последовательно поступают тетрады операндов начиная с младшей, с выхода сумматора не корректированная сумма через регистр поступает на вход блока коррекции, где корректируется, а затем записьгаается в регистр результата, выполняющего роль запоминающего устройства. При отсутствии входной информации хранение записанной информации осуществляется за счет циркуляции информации с выхода регистра результата через злемент И на вход сумматора 2. Недостатком устройства является TO, что информация, поступающая на вход, не подвергается контролю, что может привести к недостоверности получаемых результатов вычислений. Цель изобретения - повышение достоверности результатов вычислений путем введения операции контроля операндов. Поставленная цель достигается тем, что в суммирующее устройство с контролем, содержащее сумматор, регистр, блок коррекции, блок памяти и первый элемент И, причем информационный вход устройства подключен к первому информационному входу сумматора, выход которого связан с входом регистра, выходы регистра соединены с соответствующими информационными входами блока коррекции, выход которого подключен к информационному входу блока памяти, выходы блока памяти связаны с первым входом первого элемента И, второй вход которого соединен с первьм управляющим входом сз мматора и входом разрешения суммирования устройства, введены второй и третий элементы И и элемент ИЛИ, причем первый вход второго элемента И связан синхронизирующим входом .устройства, второй вход второго элемента И соединен с выходом сумматора, первый вход третьего элемента И подключен к входу разрешения контроля устройства, второй вход третьего элемента И связан с вькрдом блока коррекции, выход третьего элемента И соединен с первым входом элемента ИЛИ, второй вход которого соединен с выходом первого элемента И, выход, элемента ИЛИ связан е вторым управляющим входом сумматора, выход второго элемента И является выходом устройства, выход переноса сумматора соединен с вторым входом блока коррекции, выход переноса блока коррекции связан с вторым информационным входом сумматора, блок коррекции содержит элемент ЗИ-ИЛИ, два триггера, элемент И и двоичньй сумматор, причем первый и Второй входы первого элемента И элемента ЗИ-ИПИ соединены с соответствующими выходами регистра, первьй и второй входы второго элемента И элемента ЗИ-ИЛИ связаны соответст31венно с вторым входом первого элемента И элемента ЗИ-ИЛИ и соответств ющим выходом регистра, первый и второй входы третьего элемента И элемента ЗИ-ИЛИ подключены к выходу переноса сумматора устройства, выход элемента ЗИ-ИЛИ подключен к D -входу первого триггера, выход которого соединен с первым входом элемента И, второй вход которого является входом корректирующего кода, первый вхо двоичного сумматора связан с соответ ствующим выходом регистра, а второй вход подключен к выходу элемента И, вход переноса двоичного сумматора со единен с выходом второго триггера, D-ВХОД которого связан с первым выходом двоичного сумматора, второй выход которого является выходом суммы блока коррекции, выход первого триггера является выходом переноса блока коррекции, R и С-входы триггеров являются входами синхронизации блока коррекции. На фиг.1 представлена структурная схема суммирующего устройства-, на фиг.2 - функциональная схема сумматора j на фиг.З - функциональная схема блока коррекции; на фиг.4 - временные диаграммы сигналов синхронизации. Устройство содержит сумматор 1 ,регистр 2,блок 3 коррекции,блок 4 памяти элементы И 5-7, элемент ИЛИ 8, входы 9-13 устройства и выход 14 устройства. Первый вход сумматора 1 связан с первьмВХОДОМ 9 устройства, второй вход - через элемент ИЛИ 8 и элементы. И 5 и 7 - с вторым 10 и четвертым 12 входами устройства. Выход суммато ра 1 через регистр 2, блок 3 коррекции, блок 4 памяти связан с входом элемента И 5. Кроме этого, выход бло ка коррекции подключен к одному вход элемента И 7, что позволяет подавать на второй вход сумматора 1 откорректированную тетраду при разрешающем i сигнале на входе 12 в режиме контроля операндов. На вход 9 устройства поступает в последовательном виде информация для ее контроля или для суммирования. На вход 10 подается разрешающий сигнал при суммировании операндов, которьй обеспечивает подключение к второму входу сумматора выхода блока памяти, в котором может храниться 12. 4 или операнд, или результат предьиущего суммирования. На вход 11 поступает стробирующий сигнал, соответствующий по времени моменту, следующему за обработкой старшего разряда операнда (). На вход 13 поступает сигнал, разрешающий запись информации в ЗУ от блока коррекции. На вькоде 14 в режиме контроля операндов возникает сигнал в случае обнаружения ошибки. Сумматор 1, регистр 2 и блок 3 .коррекции осуществляют суммирование поступающих операндов по закону двоично-десятичной арифметики. Сумматор 1 содержит двоичный сумматор 15, триггер 16 двоичного переноса,элемент ИЛИ 17 и элемент И 18. Сигналы Т1, Т2, Т2 - импульсы синхронизации, сигнал ПД - сигнал межтетрадного (десятичного) переноса А1 , Б1, Р1 - соответственно входы первого, второго операнда и переноса 5р.- сумма некорректирования, Рц - сигнал двоичного переноса. В режиме контроля сигналом низкого уровня с входа 10 устройства в сумматоре 1 блокируется десятичный перенос ПД. Блок коррекции состоит из элемента ЗИ-ИЛИ 19, D -триггера 20, элемента И 21, двоичного сумматора 22 и триггера 23. На вход элемента 19 поступают сигналы с регистра 2 (Р 2...Р 4) и сигнал Рц с,сумматора 1. На выходе элемента 19 формируется признак десятичного переноса в случае, когда некорректированная сумма S 9 или сигнал двоичного переноса Р„ возник в результате сложения старших бит тетрады. Признак десятичного переноса запоминается, на триггере 20, сигнал с которого разрешает прохождение тсорректирующего кода Т (0110) через элемент 21 на второй вход сумматора Б2, на первый вход сумматора А2 поступает последовательно бит за битом некорректированная тетрада. - си1- нал Р(, 1. Двоичный сумматор складывает А2+ +Б2 5 , е учетом возникающих межбитных переносов Р2. Сигналом Т2 происходит установка в исходное состояние триггера 16 сумматора 1 сигналом Т2 - триггера 23 блока коррекции. Временные диаграммы сигналов син хронизации приведены на фиг.4, где Ь, 1 fc4 - моменты времени обработки 1-4-й бит тетрады, Д ,... , моменты времени обработки десятичны разрядов числа, причем Л - момент обработки контрольного разряда операнда; Д ,. .. ,Д - моменты обработк разрядов операнда, - момент вр мени анализа результатов сложения тетрад контролируемого операнда. Формат операнда, проходящего кон троль, имеет вид п ,.п-1,,, . ,2Кр, т. имеет п+1 разрядов, где , ti - максимальное количество десятичных разрядов обрабатываемых чисел) Кр - ко трольньй разряд числа, в котором за писывается дополнение суммы цифр чи ла до числа кратного 10, т.е. Кр 10-1 (где .1- младший разряд суммы числа). Если сумма цифр числа кратна 10, ., Контрольный разряд Кр не используется в, операциях сложения-вычитания, т.е. содержимое Кр не искажает получейных результатов, В исходном положении состояние элементов безразличное. Суммирующее устройство имеет пят режимов работы, которые определяютс состоянием сигналов на входах 9-13. В таблице приведены пять режимов в зависимости от наличия сигналов на входах, где - .- отсутствие сигнал + - наличие. ГашениеКонтроль-IЯаписьчисла+ Хранение.Сложение+ Устройство работает следующим образом. При подаче питания и отсутствии сигналов на входах 9, 10 и 12 и наличии сигнала на входе 13 (режим, гашения) за счет внутренней синхронизации (не показана) нулевая информация, формируемая на выходе сумматора 1, перемещается через регистр 2 и блок 3 коррекции в блок 4 памяти, очищая его от случайной информации, записанной в момент включения питания. Для контроля числа (операнда) необходимо подать разрешающий сигнал на вход 12, а сам операнд - на вход 9 (режим контроля). В этом режиме на первый вход сумматора с входа 9 устройства в момент Др поступает младшая тетрада первого операнда, а на второй вход сумматора поступают нули с блока 3 коррекции через открытый элемент И7 и элемент ИЛИ 8. Результат сложения первой тетрады с нулями с выхода сумматора 1 записывается в регистр 2. В следующий момент времени Д на вход сумматора 1 поступает вторая тетрада первого операнда, а на второй вход сумматора одновременно пог ступает с блока 3 коррекции результат сложения первой тетрады с нулями, т.е. первая тетрада. На сумматоре 1 вьшолняется сложение первой тетрады со второй и результат сложения записывается в регистр 2, В следующий момент времени Ц на сумматоре аналогично произойдет сложение третьей тетрады с откорректированной суммой первой и второй тетрад и результат запишется в регистр 2. В этом режиме сигнал с входа 10 блокирует десятичный перенос нд элементе И 18. При поступлении на вход.сумматора 1 с входа 9 устройства старшей тетрады первого операнда в момент Д произойдет ее сложение с суммой предьдущих тетрад и результат также запишется в регистр 2. В младшей тетраде контролируемого операнда, являющейся контрольным разрядом было записано дополнение суммы разрядов числа до десяти. Поэтому, если результат сложения старшей тетрады с суммой предьщущих тетрад будет кратен десяти, на выходе 14 устройства сигнал ошибки будет отсутствовать так как в этом случае в момент ДJ +15„ 0. Если результат сложения старшей тетрады с суммой предыдущих тетрад контролиуемого числа (операнда) не кратен десяти, то на выхо де Н в момент Дг,+ 1 сформируется сигнал ошибки, указывающий на необходимость повторения ввода и контроля числа. При достоверности первого операн да арифметическое устройство может перейти в режим записи. В режиме записи проконтролирован ного числа (управляю1цие сигналы на входах 10 и 12 отсутствуют) число (безконтрольного разряда Д) подается на вход сумматора 1 с входа 9 устройства и последовательно начиная с первого через регистр 2 и блок 3 коррекции записывается в блок 4 памяти. На другой вход сумматора в это режиме информация не поступает, i После записи последней (старшей) тетрады числа устройство может перей ти в режим хранения или режим сложения операндов. В режиме хранения (управляющий сигнал присутствует на входах 10 и 13) младшая тетрада записанного в блоке 4 памяти операнда в момент Д поступает через открытый элемент И 5 и ИЛИ 8 на вход сумматора 1 и далее записьшается в регистр 2. В следующий момент времени Д, вторая тетрада аналогичным образом записывается в регистр 2, а первая тетрада, пройдя через блок 3 коррекции, вновь записывается в блок 4 памяти. В этом режиме происходит циркуляция информа ции с выхода блока 5 памяти на его

ft оЫ

tArJ

1Q в«1ГТ

/3 о- вход через элементы И 5 и ИЛИ 8, сумматор 1, регистр 2 и блок 3 коррекции. В режиме сложения дв5ос операндов управляющие сигналы присутствуют на входах 9, 10 и 13. Операции сложения должны предшествовать операции контроля операндов, подлежащих сложению. Но сложение может осущест-г ; вляться в суммирующем устройстве и без контроля. Ив том, и в другом случае процесс сложения происходит следующим образом. В момент времени Д, когда через открытый элемент И 5, элемент ИЖ 8 на вход сумматора поступает первая тетрада первого операнда, записанного ранее, в блоке 4 памяти на первый вход сумматора 1 входа 9 устройства поступает младший разряд (первая тетрада) второго операнда. На сумматоре выполняется побитно сложение. К началу второй тетрады в ре -v гистре 2 записана некорректированная сумма младших разрядов. На сумматоре 1 в момент 2 начинается сложение вторых разрядов, а сумма младших разрядов, проходя через блок 3 коррекции, на котором при необходимости корректируется, записывается в блок 4 памяти и т.д. После суммирования старших разрядов операндов устройство переходит в режим хранения. Таким образом, повьпнг ется достоерность получаемого результата и асширяются функциональные возможости устройства.

А1

61 Pi

/5

J)

Т1 Т2

16

10

о

Фиг: 2

CM

L

5 См

tJV

U

Cvj

s

CV4

«:

(QtfO)i

to

Ci

CM

f CJ

и

«4

a

i

.

Р5|

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Арифметическое устройство | 1973 |

|

SU454549A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Арифметическое устройство | 1979 |

|

SU798822A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-02-15—Публикация

1983-10-04—Подача