ИЛИ, первый вход которсзго подсоедине к выходу второгоэлемента ИЛИ, первый, второй и третий входы которого соединены соответственно с первым, вторым и третьим выходами двоичного счетчика, четвертый выход которого подключен к второму входу первого элемента ИЛИ и первому входу третьего элемента ИЛИ, выход которого соед нен с входом сброса триггера, вход установки которого подключен к второму входу элемента ИЛИ-НЕ, выходу второго элемента И и выходу управления вычитанием блока управления, вхо признака которого соединен с третьим входом второго элемента И, четвертый вхОл которого соединен с первым входом третьего и четвертого элементов и с входом положительного знака блока управления, вход отрицательного Знака которого подключен к первому 7ХОДУ Ьйтого элемента И, второй вход коюрого соединен с выходом триггера и цторым входом четвертого элемента И, третий вход которого соединен с третьим входом пятого элемента И, первым входом двоичного счетчика, первым входом шестого элемента И и первым входом седьмого элемента И, второй вход которого соединен с первым входом первого элемента ИЛИ, выход которого соединен с вторым входом шестого элемента И, «ыxojc котоpoi|o через первый элемент задержки соединен с выходом управления сдвиго на бит блока управления, выход управ ления сдвигом на тетраду которого 73 соединен с выходом четвертого элемента ИЛИ, первый вход которого через , второй элемент задержки подключен к пятому выходу двоичного счетчика и второму входу третьего элемента И, выход которого соединен с первым входом пятого элемента ИЛИ, выход которого через третий элемент задержки сое:динен с вторым входом двоичного счетчика, шестой выход которого соединен с вторым входом первого элемента И, выход которого соединен с первым входом шестого элемента ИЛИ, второй вход которого соединенс выходом восьмого элемента И, первый вход которого соединен с выходом генератора импульсов, а второй вход с выходом элемента ИЛИ-НЕ, второй вход которого подключен к третьему входу шестого элемента ИЛИ, выход . которого соединен с первым входом двоичного счетчика, седьмой выход которого подключен к второму входу четвертого элемента ИЛИ и второму входу пятого элемента ИЛИ, выход которого соединен с выходом управления приемом в регистр делителя блока управления, выход управления преобразованием которого соединен с выходом седьмого элемента И, а выход управления установкой - с выходом седьмого элемента ИЛИ, первый вход которого подключен к второму входу третьего ; , элемента ИЛИ и выходу четвертого элемента И, а второй вход - через четвертый элемент задержки к выходу пятого элемента И.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления п-разрядных десятичных чисел | 1976 |

|

SU742933A1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| Устройство для деления п-разрядныхдЕСяТичНыХ чиСЕл | 1979 |

|

SU807282A1 |

| Устройство для деления десятичных чисел | 1976 |

|

SU744562A1 |

| Устройство для деления десятичных чисел | 1990 |

|

SU1774328A1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| ПОСЛЕДОВАТЕЛЬНЫЙ ДЕЛИТЕЛЬ ТРОИЧНЫХ ЦЕЛЫХ ЧИСЕЛ | 2023 |

|

RU2810609C1 |

| Арифметическое устройство | 1971 |

|

SU522497A1 |

| Устройство для обработки данных | 1985 |

|

SU1287146A1 |

| УСТРОЙСТВО ПРЕОБРАЗОВАНИЯ ИЗ ДЕСЯТИЧНОЙ СИСТЕМЫ СЧИСЛЕНИЯ В ДВОИЧНУЮ | 2003 |

|

RU2248094C2 |

УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ ДЕ ЯТЖНЫХ ЧИСЕЛ, содержащее регистр частотного, регистр делителя, десятичный сумматор, регистр хранения, блок управления, содержащий первый, второй, третий,, четвертый, пятый, . шестой и седьмой элементы И, генера- тор тактовых импульсов, двоичный счетчик; первый, второй и третий элементы задержки, триггер причем информационный выход регистра делителя соединен с информационным входом десятичного сумматора, выход регистра хранения соединен с информационным входом регистра делителя, выход:управления вычитанием блока управления соединен с входом вычитания десятич- .. ного сумматора, вход сложения которого подсоединен к выходу управления сложением блока управления, вход по-, ложительного и отрицательного знаков .которого подкл19чен соответственно к выходам положительного и отрицательного знаков десятичного сумматора, выход управления установкой блока управления соединен с входом установки в 1 младшего бита регистра частного, вход сдвига на бит младшей тетрады которого соединен с в&1ходом управления сдвигом на бит блока управления, выход управления преобразованием которого соединен с входом сдвига регистра делителя, вход приема которого подключен к выходу управления приемом блока управления, отличающееся тем, что, с целью повышения быстродействия, в него введена схема сравнения, причем первый вход схемы сравнения соединен с информационным выходом трех старших тетрад десятичного сумматора, вход сдвига на тетраду которого соединен с входом сдвига на тетраду регистра частного, вход установки (Л девяти младшей тетрады которого подключен к выходу управления сложением блока управления, вход признака которого подсоединен к выходу признака схемы сравнения, второй вход которой соединен с информационным выходом трех старших тетрад регистра дели|(а теля, вход сдвига на тетраду деся00 тичного сумматора соединен с выходом ;: управления сдвигом на тетраду блока -vl управления, а в блок управления ввеСАЭ дены восьмой элемент И, элемент за- держки, элемент ИЛИ-НЕ, делитель частоты, первый, второй, третий, четвертый, пятый, шестой, седьмой элементы ИЛИ, причем первый вход элемента ИЛИ-НЕ соединен с выходом управления сложением блока управления и с выходом первого элемента И, первый вход которого подключен к выходу делителя частоты и первому .входу второго элемента И, второй вход которого соединен с выходом первого элемента

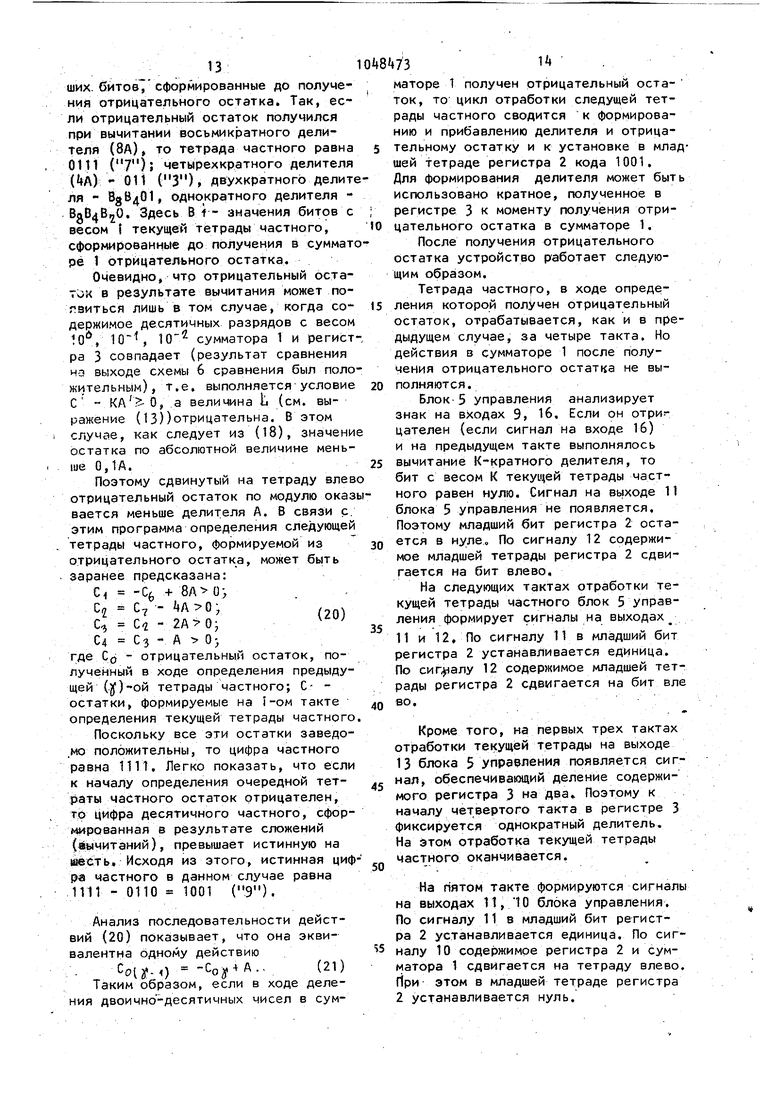

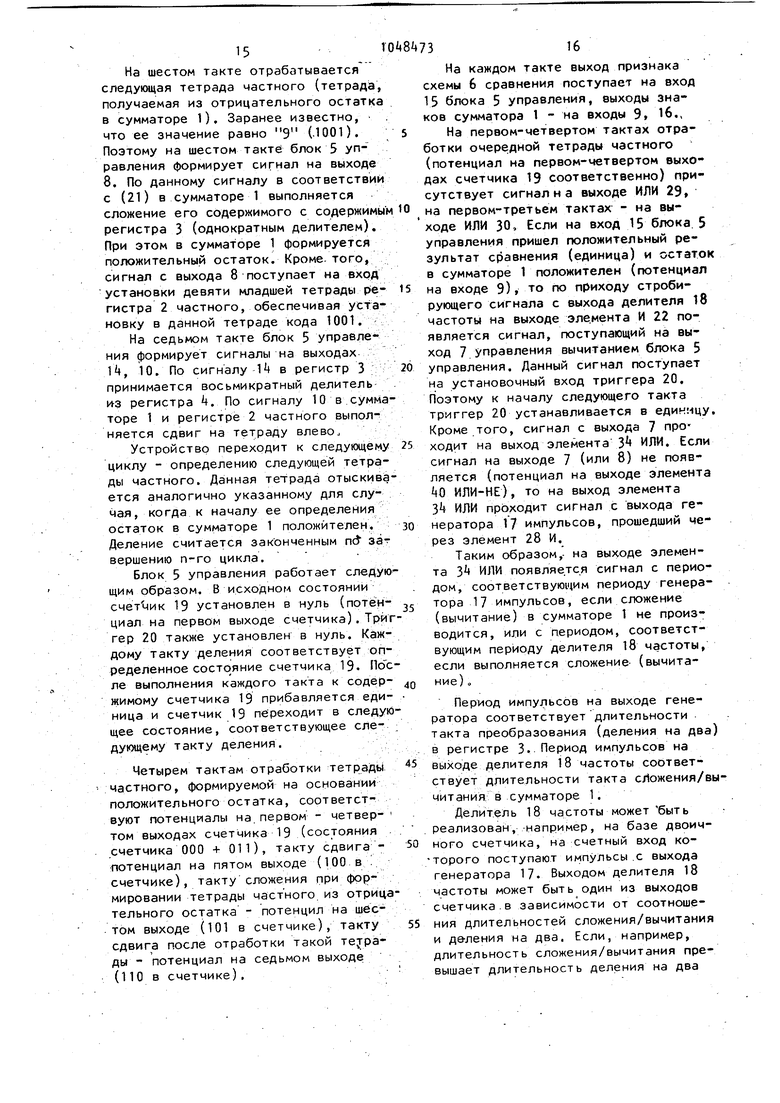

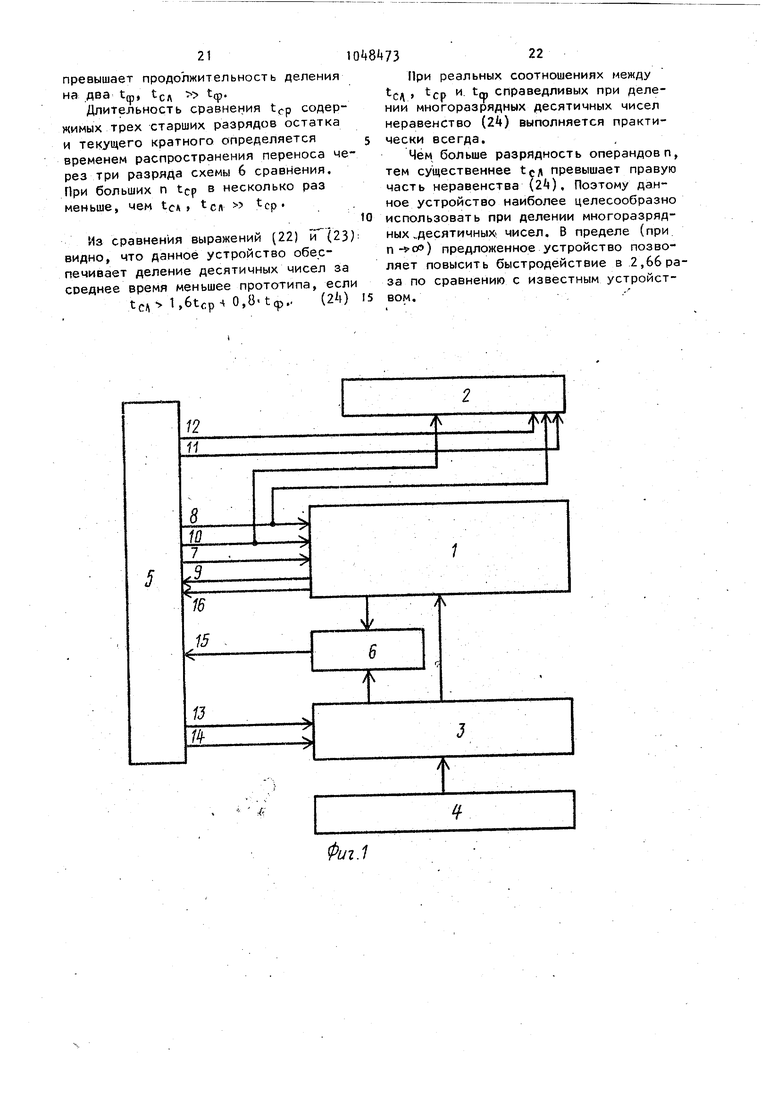

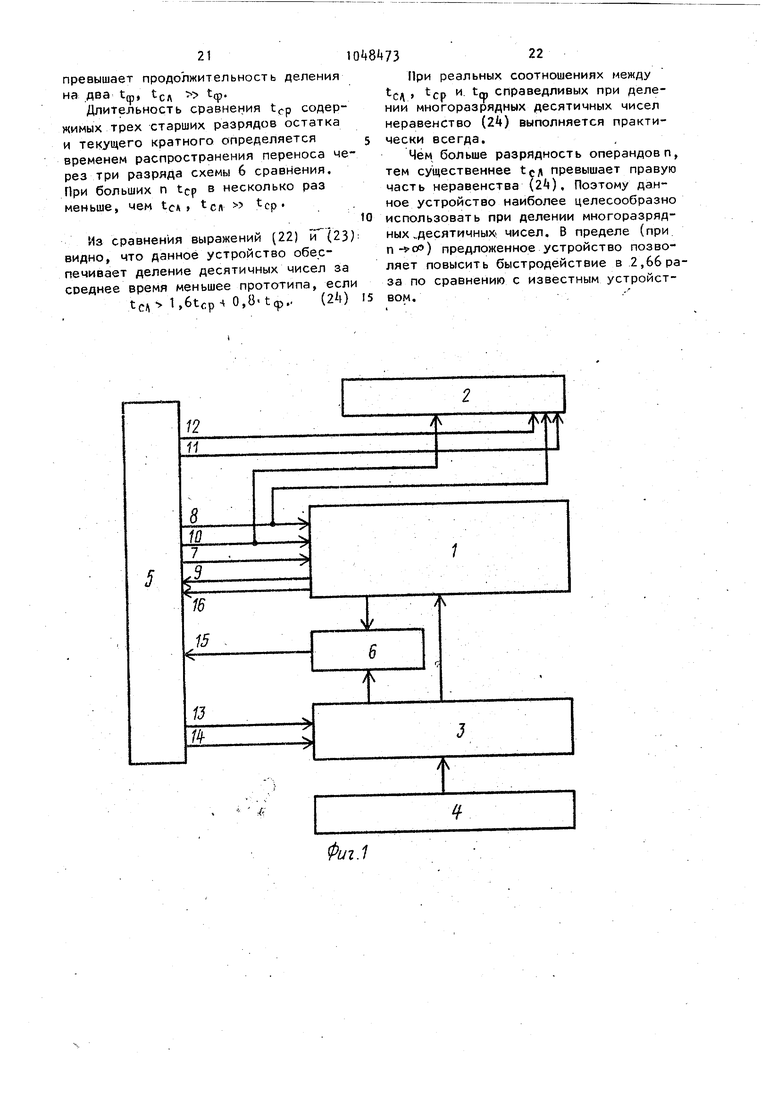

Изобретение относится к области вычислительной техники и предназначено для деления десятичных чисел, представленных кодом 8-4-2-1. Устройство целесообразно применять в быстродействующих вычислителях, работающих с многоразрядными десятичными операндами.

Известно устройство для деления п-разрядных десятичных чисел, содержащее десятичный сумматор, регистр частного, регистр-преобразователь делителя, регистр восьмикратного делителя и блок управления l .

Недостатком данного устройства являются большие затраты оборудования (разрядность сумматора, регистрапреобразователя делителя, регистра восьмикратного делителя соответствует удвоенной разрядности десятичных операндов).

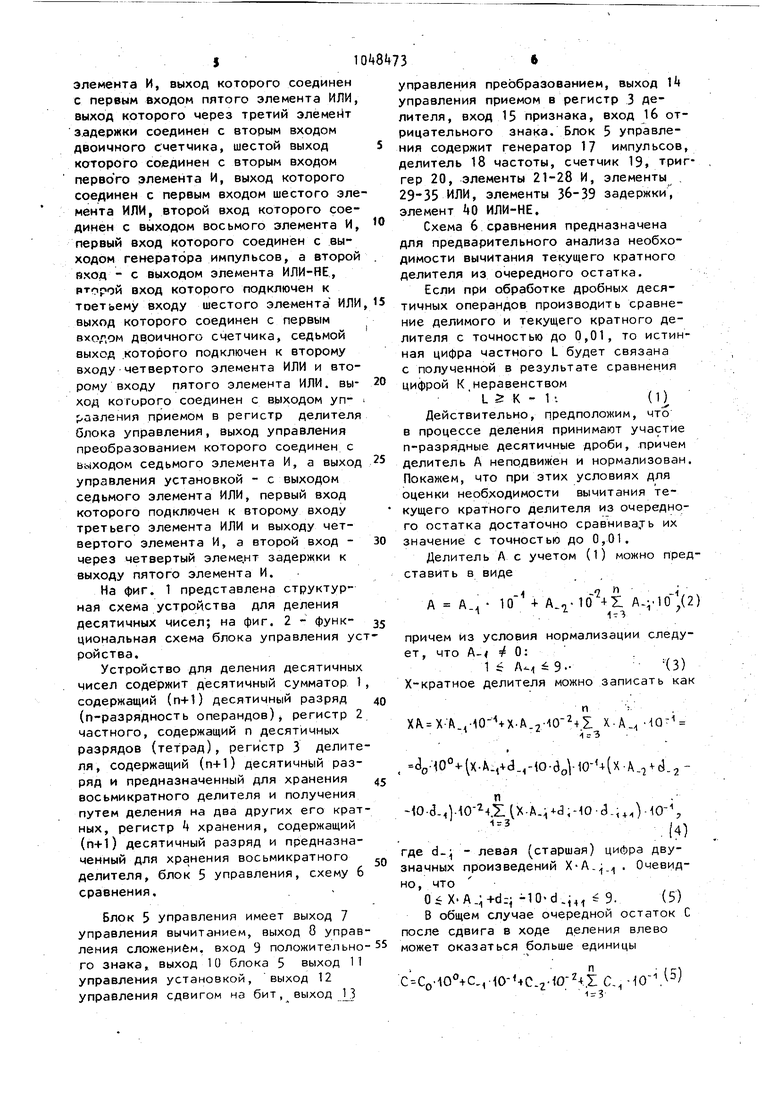

Наиболее близким по технической сущности к изобретению является устройство для деления п-разрядных десятичных чисел, содержащее десятичный сумматор, регистр частного, регистр делителя, регистр хранения, блок управления, содержащий первый. 3 Btopoft, третий, четвертый, пятый, шестой и седьмой элементы И, генератор тактовых импульсов, двоичный счетчик, первый, второй и третий элементы задержки, триггер, причем информационный выход регистра делителя соединен с информационным входом дё;сятичного сумматора, ВЫХОД регистра хранения соединен с информационным входом регистра делителя, выход управления вычитанием блока.управления соединен с входом вычитания десятичного сумматора, вход сложения которого подсоединен к выходу управления сложением блока управления, вход положительного и отрицательного знаков которого подключен соответственно к , выходам положительного и отрицательно го знака десятичного сумматора, выход управления установкой управления соединен с входом установки в единицу младшего бита регистра чйсТ ного, вход сдвига на бит младшей тетрады которого соединен с выходом управления сдвигом на бит блока управления, выход управления преобразованием которого соединен с входом сдвига регистра делителя, вход приема которого подключен к выходу управления приемом управления. Данное уст.РОЙство отрабатывает частное путем последовательного определения значе ний битов в двоично-десятичном представлении десятичных цифр частно- t2l. . К недостаткам устройства можно отнести низкое быстродействие: ДЛя на хождения каждой десятичной цифры частного требуется четыре такта (сложения) вычитания, Цель изобретения - повышение быстродействия устройства для деления десятичных чисел. Поставленная цель достигается тем, что в устройство введена схема сравнения, причем первый вход схемы сравнения соединен с информационным выходом трех старших тетрад десятичного сумматора, вход сдвига на тетраду которого соединен с входом сдвига на тетраду регистра частного, вход установки девяти младшей тетрады которого подключен к выходу управления сложением блока управления, вход приз нака которого подсоединен к. выходу признака схемы сравнения, второй вход которого соединен с информационным выходом трех старших тетрад регистра 73 делителя, вход сдвига на-тетраду десятичного сумматору соединен с выходом управления сдвигом на тетраду блока управления, а в блок управления введены восьмой элемент И, элемент задержки, элемент ИЛИ-НЕ, делитель частоты, первый, второй, третий, четвертый, пятый, шестой, седьмой элементы ИЛИ, причем первый вход элемента ИЛИ-НЕ соединен с выходом управления сложением блока управления и с выходом первого элемента И, первый вход которого подключен к выходу делителя частоты и первому входу второго элемента И, второй вход которого соединен с выходом первого элемента ИЛИ, первый вход которого подсоединен к ВЫХОДУ второго элемента ИЛИ, первый, второй, третий входы которого соединены соответственно с первым, вторым и третьим выходами двоичного счетчика,.четвертый выход которого подключен к второму входу первого элемента ИЛИ и первому входу третьего элемента.ИЛИ, выход которого соединен с входом сброса, триггера, вход установки которого подключен к второму входу элемента ИЛИ-НЕ, выходу второго элемента И и выходу управления вычитанием блока управления, вход признака которого соединен с, третьим входом второго элемента И, четвертый вход которого соединен с первыми входами третьего и четвертого элементов И и с входом положительного знака блока управления, вход отрицательного знака которого подключен к первому входу пятого элемента И, второй вход которого соединен с выходом триггера и вторым входом четвертого элемента И, третий вход которого соединен с третьим входом пятого элемента И, первым входом двоичИого счетчика, первь|м входом шестого элемента И и первым входом седьмого элемента И, второй вход которого соединен с первым входом первого элемента ИЛИ, выход которого соединен с вторым входом шестого элемента И, выход которого через первый элемент.задержки соединен с выходом управления сдвигом на бит блока управления, выход управления сдвигом на тетраду которого соединей с выходом четвертого элемента ИЛИ, первый вход которого через второй элемент задержки подключен к пятому выходу двоичного счетчика и второму входу третьего элемента И, выход которого соединен с первым входом пятого элемента ИЛИ выход которого через третий элемейт задержки соединен с вторым входом двоичного счетчика, шестой выход которого соединен с вторым входом первого элемента И, выход которого соединен с первым входом шестого эле мента ИЛИ, второй вход которого соединен с выходом восьмого элемента И первый вход которого соединен с выходом генератора импульсов, а второй вход - с выходом элемента ИЛИ-НЕ, рторой вход которого подключен к третьему входу шестого элемента ИЛИ выход которого соединен с первым входом двоичного счетчика, седьмой выход .которого подключен к второму входу четвертого элемента ИЛИ и второму входу пятого элемента ИЛИ. выход которого соединен с выходом упразления приемом в регистр делителя блока управления, выход управления преобразованием которого соединен с выходом седьмого элемента И, а выход управления установкой - с выходом седьмого элемента ИЛИ, первый вход которого подключен к второму входу третьего элемента ИЛИ и выходу четвертого элемента И, а второй вход через четвертый элеме.нт задержки к выходу пятого элемента И. На фиг. 1 представлена структурная схема устройства для деления десятичных чисел; на фиг. 2 - функциональная схема блока управления ус ройства. Устройство для деления десятичных чисел содержит десятичный сумматор 1 содержащий (п+1) десятичный разряд (п-разрядность операндов) регистр 2 частного, содержащий п десятичных разрядов (тетрад), регистр 3 делите ля, содержащий (пч-1) десятичный разряд и предназначенный для хранения восьмикратного делителя и получения путем деления на два других его крат ных, регистр 4 хранения, содержащий (n+l) десятичный разряд и предназначенный для хранения восьмикратного делителя, блок 5 управления, схему сравнения. Блок 5 управления имеет выход 7 управления вычитанием, выход О управ ления сложением, вход 9 положительно го знака,, выход 10 блока 5 выход 11 управления установкой, выход 12 управления сдвигом на бит, выход 13 управления преобразованием, выход И управления приемом в регистр 3 делителя, вход 15 признака, вход 16 отрицательного знака. Блок 5 управления содержит генератор 17 импульсов, делитель 18 частоты, счетчик 19, триггер 20, элементы 21-28 И, элементы 29-35 ИЛИ, элементы 36-39 задержки, элемент 0 ИЛИ-НЕ. Схема 6 сравнения предназначена для предварительного анализа необходимости вычитания текущего кратного делителя из очередного остатка. Если при обработке дробных десятичных операндов производить сравнение делимого и текущего кратного делителя с точностью до 0,01, то истинная цифра частного L будет связана с полученной в результате сравнения цифрой К неравенством L S К - 1 -. (U Действительно, предположим, что в процессе деления принимают участие п-разрядные десятичные дроби, .причем делитель А неподвижен и нормализован. Покажем, что при этих условиях для оценки необходимости вычитания текущего кратного делителя из очередного остатка достаточно сравнива.,ть их значение с точностью до 0,01. Делитель Л с учетом (1) можно представить в виде 4- А .-10 - А.-.10(2) . ,1т причем из условия нормализации следует, что А- 40: 1 i 69- ЧЗ) Х-кратное делителя можно записать как .д-10ЧХА.2-10 1 Х-АН 10- 3o- 0°- lX-AM- d.,-iO-aoVw(x-A-7 -2ИО.а.,).10-ЧХ1Х-Д.;,сЗ,-10-а,,,).Ю-% . :.(4) де d- - левая (старшая) цифра двуОчевидначных произведении о, что .A.+d.- -10-d.j, 9. В общем случае очередной остаток С осле сдвига в ходе деления влево ожет оказаться больше единицы Со10 С,,..,1 С.. ЧО .7 . Обозначим через А, ХА и С представления чисел А, ХА и С с точность ДО 0,01: A A.4 IOVA.2-(, KA-do-IO (,+d.,HO-ao)HO-H (к.А-2- -2-10-()-10 С Co10° C..(0-ЧC-г 0 Предположим, что при сравнении старших разрядов остатка и старших разрядов текущего К-кратного делител (с точностью до 0,01) схема саюомивовала поизняк тот. чтп Г. кд Сформировала признак того, что С Кю В этом случае выполняется соотношени с К- А + z, Щ .где К - цифра частного, полученная в результате сравнения старших разря дов;, Z - остаток от вычитания из старших разрядов предыдущего остатка С величины КА, причем 0 Z А;(9) Истинная цифра частного L соответствует выражению С L A-vZ,- (10) где Z - истинный остаток от вычита-: ния кратного делителя LA из предыдущего остатка С, причем О Z :t А - 10- (11) Остаток ROT.вычитания кратного дели Леля КА.ИЗ предьщущего остатка С, исходя из (k), (6), (7), (8), представляется как .+.1. , . .Чоб, (12) o6 |:Ic-4K- -i a.iHo 3.u,lio-. (t3) . Исходя ИЗ (9) и (12), справедливо соотношение Z R -о/г , откуда R2- 0. Как следует из (13) I « . : . .U-ft.+d.;-W-d.;,,VlO-(15) С учетом Л5)chpaвeдливo S- 10 - 10 или, как следует из (2) и (3)j cimin - 0,1А + 10- На основании (1)и (17) R - О.ГА +10 738 Исходя из выражений (10) и (12), истинная цифра частного L связана с цифрой К, полученной в результате сравнения старших разрядов остатка и текущего кратного делителя, равенст вом LA КА4 R-Z , которое на основании (18) и(11) приводится к неравенству - 0,1Ai го (К-1)А - (0,1А - 2-ЧО) (15) Поскольку величина 0,1 А - 2.-10 заведомо меньше А, а L и К могут принимать только целые значения, то / (19) сводится к;виду (1). Устройство (см. фиг. 1) обрабатывает десятичную информацию, представленную кодом 8-4-2-1. Деление п-разрядных чисел -в yqTройстве выполняется за п циклов. На каждом цикле определяется значение очередного десятичного разряда (тетрады) двоично-десятичного частного. Деление выполняется методом без восстановления остатков с неподвижным делителем и сдвигом остатков влево. Устройство работает следующим образом. В исходном состоянии в младших п тетрадах сумматора 1 находится делимое, в регистре 3 и регистре 4 восьмикратный делитель (однократный делитель должен быть нормализован) старший десятичный разряд сумматора 1 и регистра 2 установлены в нуль. Счетчик 19 и триггер 20 блока 5 уп- равления также установлены в нуль. На первом цикле определяется старший десятичный разряд (тетрада) частного. При определении каждой тетрады частного может возникнуть две ситуации. Все остатки, формируемые в сумматоре 1 в ходе определения текущей тетрады частного, положительны. В этом случае значение десятичной цифры частного определяется за четыре . такта. На каждом такте отыскивается значение очередного бита в двоичнодесятичном представлении тетрады частного.. В ходе определения текущей тетрады частного на одном из тактов вычитания в сумматоре 1 образовался отрицательный остаток о В этом случае количество тактов, необходимое для нахождения текущей цифры частного, соответствует моменту получения от-/ 9 рицательного остатка, а для отработ ки следующей тетрады частного требу ется один такт сложения отрицательного остатка с делителем„ Рассмотрим работу устройства в каждой из этих ситуаций. Пусть при определении текущей де сятичной цифры частного все остатки формируемые в сумматоре 1, положительны. В этом случае устройство ра ботает следующим образом. На первом такте цккла схема срав нения 6 анализирует значение содержимого старших десятичных разрядов (разряда с весом целых 10 и двух разрядов с весом и 10 ) сумматора 1 (очередного остатка) и регистра 3 (восьмикратного делителя). При отрицательном результате сравнения (старшие разряды остатка мень I.e восьмикратного делителя) на выходе схемы сравнения 6 присутствует нуль. В этом случае, как следует из (1), текущая десятичная цифра частного меньше восьми (1000), т.е. бит ее двоично-десятичного представления (в коде ) с весом 8 равен нулю. В этом случае вычитание восьмикратного делителя, хранящегося в регистре 3, не производится. Блок 5 управления формирует сигналы на выходах 13 и 12. По сигналу 13 в регистре 3 выполняется деление его содержимого на два. Поэтому к концу данного такта в регистре 3 фиксируется четырехкратный делитель. По. сигналу 12 выполняется сдвиг содержимого младшей тетрады регистра 2 частного на один бит в сторону старших разрядов. В этом случае длительность такта определяется длитель ностью операции деления на два в регистре 3. Если же результат сравнения на выходе схемы 6 сравнения положителен (старшие разряды остатка больше или старшим разрядам восьмикратног делителя), то как следует из (1), те кущая десятичная цифра частного равна 7 (0111), 8 (1000) или 9 (1001), в этом случае блок управления 5 формирует сигнал на выходе 7, по которому в сумматоре 1 из его содержимого вычитается содержимое регистра 3. Одновременно по сигналу 13 блока 5 управления в регистре 3 выполняется деление его содержимого на два (к концу такта в нем фиксируется 7310 четырехкратный делитель), а по сигналу 12 в младшей тетраде гистра 2 производится сдвиг на один бит влевоо В младший бит регистра 2 при этом заносится нуль. В этом случае длительность такта определяется длительностью операции вычитания в сумматоре 1, Знак результата вычитания поступает на входы знака 9 и 16 блока управления 5. На втором такте блок управления 5 анализирует знак очередного остатка, сформированного в сумматоре 1. Если. знак на его входе 9 положителен и на предыдущем такте выполнялось вычитание, то, следовательно, предыдущий остаток был больше восьмикратного делителя, т.е. текущая цифра частного равна 8 (1000) или 9 (1001), а ее бит с весом 8 равен единице. Поэтому блок 5 управления формирует сигнал нд выходе 11, по которому младший бит регистра 2 частного устанавливается в единицу. Одновременно схема 6 сравнения анализирует содержимое трех старших тетрад сумматора 1 (очередного остатка), и регистра 3 (четырехкратного делителя). При отрицательном результате сравнения бит с весом А текущей тетрады частного равен нулю. Вычитание четырехкратного делителя из очередного остатка не производится. Блок 5 управления формирует сигналы на выходах 13 и 12. По сигналу 13 в регистре 3 выполняется деление его содержимого на два (к концу такта в нем фиксируется двухкратный делитель). По сигналу 12 производится сдвиг содержимого младшей тетрады регистра частного на один бит в сторону старших разрядов. В младший бит регистра 2 при этом заносится нуль. При положительном результате сравнения (единица на выходе схемы 6 сравнения), как следует из (1), текущая десятичная цифра частного равна 3 (0011), 4 (0100), 5 (0101), 6 (ОНО) или 7 (0111). В этом случае блок .5 управления гюмимо сигна лов на выходах 13 и 12 формирует сигна-л на выходе 7, по которому в сумматоре 1 из его содержимого вычитается содержимое регистра 3. Знак результата вычитания поступает на входы знака 9, 16 блока ij управления. Третий такт выполняется аналогично второму. Блок 5 управления анализирует знак остатка, поступающий на его входы 9, 16. Если он положителен (вход 9) и на предыдущем такте выпол нялось вычитание, то, следовательно, предыдущий остаток был больше четырехкратного делителя, т.е. бит с весом 4 текущей тетрады частного равен единице. Поэтому блок 5 управления формирует сигнал на выходе 11, по которому младший бит регистра 2 частного устанавливается в единицу. Одновременно схема 6 сравнения анализирует содержимое старших разрядов остатка и регистра 3 (двухкрат ного делителя). При отрицательном результате сравнения вычитание двухкратного делителя из очередного остатка не производится. Блок 5 управл ния формирует сигналы на выходах 13 и 12. По сигналу 13 в регистре 3 выполняется деление его содержимого на два (к концу такта в нем формируется однократный делитель). По сигналу 12 содержимое младшей тетрады регистра 2 сдвигается на один бит в сторону старших разрядов. При положительном результате срав нения (признак на выходе схемы 6 сравнения равен единице), как следует из (1) значение в двух младших битах текущей тетрады частного равно 01, 10 или 11. В этом случае помимо сигналов на выходах 13 и 12 блок 5 управления формирует сигнал на выходе 7. По.этому сигналу в сумматоре 1 из его содержимого вычитается содержимое регистра 3 (двухкратный делитель) . Знак результата вычитания поступа ет на входы знака 9, 16 блока 5 управления. Четвертый такт выполняется аналогично. Блок 5 управления анализирует знак на входах 9, 16. Если он положителен и на предыдущем такте выполнялось вычитание, то предыдущий остаток был больше двухкратного делителя, т.е. бит с весом 2 текущей тетрады частного равен единице. Поэтому по сигналу на выходе 11 блока управления младший бит регистра 2 устанавливается в единицу. Одновременно схема 6 анализирует старшие разряды остатка и однократного делителя. При положительном результате сравнения блок 5 управления формирует сигнал на выходе 7, по кот рому в сумматоре 1 из его содержимог вычитается содержимое регистра 3 (однократный делитель). В это же время появляется сигнал на выходе 12, по которому содержимое младшей тетрады регистра 2 сдвигается на один бит влево. Сигнал на выходе блока 5 управления на четвертом такте не формируется. Поэтому к концу данного такта в регистре 3 сохраняется однократный делитель. На этом цикл определения значения текущей тетрады частного оканчивается. На пятом такте блок 5 управления анализирует знак на входах 9, 16. Если сигнал поступил на вход 9 и на предыдущем такте выполнялось вычитание, то, следовательно, бит с весом 1 текущей тетрады частного равен единице. Поэтому на выходе 11 блока 5 управления появляется сигнал, по которому младший бит регистра 2 устанавливается в единицу. Таким образом, в младшей тетраде регистра 2 сформировалось значение тетрады частного в коде 8-4-2-1. По сигналу на выходе 10 блока 5 управления содержимое регистра 2 частного и сумматора 1 сдвигается на тетраду в сторону старших разрядов. При этом в младшей тетраде регистра 2 устанавливается нуль. Одновременно, если на вход 9 блока 5 управления пришел сигнал, то появляется сигнал на выходе . По этому сигналу в регистр 3 принимается восьмикратный делитель из регистра , Устройство начинает отработку следущей тетрады частного. Рассмотрим теперь работу устройства для случая, когда при определении текущей тетрады частного в результате одного из тактов вычитания в сумматоре 1 образовался отрицательный остаток(до этого момента такая тетрада отрабатывалась аналогично). В этом случае нет необходимости в дальнейшем определении битов текущей тетрады частного. Как следует из (1), если при вычитании К-кратного делителя в сумматоре 1 получился отрицательный остаток, то текущий бит данной тетрады частного равен нулю, а последующая группа из битов данной тетрады равна 11...1(К-1). При определении значения данной тетрады частного следует учесть значение ее стар13ших. битое, сформированные до получения отрицательного остатка. Так, если отрицательный остаток получился при вычитании восьмикратного делителя (8А), то тетрада частного равна 0111 (7); четырехкратного делителя () - Oil (3), двухкратного делит ля - , однократного делителя Здесь В f- значения битов с весом f текущей тетрады частного, сформированные до получения в суммат ре 1 отрицательного остатка. Очевидно, что отрицательный остаток в результате вычитания может появиться лишь в том случае, когда содержимое десятичных разрядов с весом 0, , сумматора 1 и регист ра 3 совпадает (результат сравнения из выходе схемы 6 сравнения был поло жительным) , т.е. выполняется условие С КА5-0, а величина L (см. выражение (13))отри14ательна. В этом случае, как следует из (18), значени остатка по абсолютной величине меньше 0,1 А. Поэтому сдвинутый на тетраду влев отрицательный остаток по модулю оказ вается меньше делителя А. В связи с. этим программа определения следующей тетрады частного, формируемой из отрицательного остатка, может бь|ть заранее предсказана: С -С + 8А 0 Сг с, - i., . Ц 0-2 - Сд Сз - А 0} где С0 - отрицательный остаток, полученный в ходе определения предыдущей (у)-ой тетрады частного; С- остатки, формируемые на i-ом такте определения текущей тетрады частного Поскольку все эти остатки заведо.мо положительны, то цифра частного равна nil. Легко показать, что если к началу определения очередной тетраты частного остаток отрицателен, то цифра десятичного частного, сформированная в результате сложений {вычитаний), превышает истинную на . Исходя из этого, истинная цифра частного в данном случае равна 1111 - 0110 1001 (9). Анализ последовательности действий (20) показывает, что она эквивалентна одному действию Col2j.4) А., Таким образом, если в ходе деления двоично-десятичных чисел в сум4УЗIматоре 1 получен отрицательный остаток, то цикл отработки следущей тетрады частного сводится к формированию и прибавлению делителя и отрицательному остатку и к установке в младшей тетраде регистра 2 кода 1001. Для формирования делителя может быть использовано кратное, полученное в регистре 3 к моменту получения отрицательного остатка в сумматоре 1. После получения отрицательного остатка устройство работает следующим образом. Тетрада частного, в ходе определения которой получен отрицательный остаток, отрабатывается, как и в предыдущем случае, за четыре такта. Но действия в сумматоре 1 после получения отрицательного остатка не выполняются. Блок5 управления анализирует знак на входах 9, 16. Если он отри цателен (если сигнал на входе 16) и на предыдущем такте выполнялось вычитание К-кратного делителя, то бит с весом К текущей тетрады частного равен нулю. Сигнал на выходе 11 блока 5 управления не появляется. Поэтому младший бит регистра 2 остается в нуле, По сигналу 12 содержимое младшей тетрады регистра 2 сдвигается на бит влево. На следующих тактах отработки текущей тетрады частного блок 5 управления формирует сигналы на выходах 11 и 12, По сигналу 11 в младший бит регистра 2 устанавливается единица. По сигналу 12 содержимое младшей тетрады регистра 2 сдвигается на бит вле ®° Kpoмe того, на первых трех тактах отработки текущей тетрады на выходе 13 блока 5 управления появляется сигнал, обеспечивающий деление содержимого регистра 3 на два.. Поэтому к началу четвертого такта в регистре 3 фиксируется однократный делитель. На этом отработка текущей тетрады частного оканчивается. На пятом такте формируются сигналы на выходах 11, 10 блока управления. По сигналу 11 в младший бит регистра 2 устанавливается единица. По сигналу 10 содержимое регистра 2 и сумматора 1 сдвигается на тетраду влево. При этом в младшей тетраде регистра 2 устанавливается нуль. 15 На шестом такте отрабатывается следующая тетрада частного (тетрада, получаемая из отрицательного остатка в сумматоре 1), Заранее известно, что ее значение равно 9 (.1001). Поэтому на шестом такте блок 5 управления формирует сигнал на выходе 8. По данному сигналу в соответствии с (21) в сумматоре 1 выполняется сложение его содержимого с содержимы регистра 3 (однократным делителем). При этом в сумматоре 1 формируется положительный остаток. Кроме, того, сигнал с выхода 8 поступает на вход установки девяти младшей тетрады pieгистра 2 частного, обеспечивая установку в данной тетраде кода 1001. На седьмом такте блок 5 управления формирует сигналы на выходах , 10. По сигналу в регистр 3 принимается восьмикратный делитель W3 регистра k. По сигналу 10 в сумма торе 1 и регистре 2 частного выполняется сдвиг на тетраду влево. Устройство переходит к следующему циклу - определению следующей тетрады частного. Данная тетрада отыскивй ется аналогично указанному для случая, когда к началу ее определения остаток в сумматоре 1 положителен, Деление считается законченным п завершению п-го цикла. Блок 5 управления работает следую щим образом. В исходном состоянии счетчик 19 установлен в нуль (потенциал на первом выходе счетчика). Триг гер 20 также установлен в нуль. Каждому такту деления соответствует определенное состо яние счетчика 19. Пос ле выполнения каждого такта к содержимому счетчика 19 прибавляется единица и счетчик 19 переходит в следую щее состояние, соответствующее еледующему такту деления. Четырем тактам отработки тетрадь частного, формируемой на основании положительного остатка, соответствуют потенциалы на.первом - четвертом выходах счетчика 19 (состояния счетчика 000 + 011), такту сдвига лотенциал на пятом выходе (100 в . счетчике), такту сложения при формировании тетрады частного из отрицательного остатка - потенция на шестом выходе (101 в счетчике), такту сдвига после отработки такой те рады - потенциал на седьмом выходе (110 в счетчике). 73 На каждом такте выход признака схемы 6 сравнения поступает на вход 15 блока 5 управления, выходы знаков сумматора 1 - на входы 9, 16,, На первом-четвертом тактах отработки очередной тетрады частного (потенциал на первом-четвертом выходах счетчика 19 соответственно) присутствует сигнална выходе ИЛИ 29, на первом-третьем тактах - на выходе ИЛИ 30, Если на вход 15 блока. 5 управления пришел положительный результат сравнения (единица) и остаток в сумматоре 1 положителен (потенциал на входе 9), то по приходу стробирующего сигнала с выхода делителя 18 частоты на выходе эле.мента И 22 появляется сигнал, поступающий на выход 7 управления вычитанием блока Б управления. Данный сигнал поступает на установочный вход триггера 20. Поэтому к началу следующего такта триггер 20 устанавливается в единицу. Кроме того, сигнал с выхода 7 проходит на выход элемента З ИЛИ. Если сигнал на выходе 7 (или 8) не появляется (потенциал на выходе элемента kO ИЛИ-НЕ), то на выход элемента 3 ИЛИ проходит сигнал с выхода генератора 17 импульсов, прошедший через элемент 28 И. Таким образом,- на выходе элемента 3 ИЛИ появляется сигнал с периодом, соответствующим периоду генератора 17 импульсов, если сгюжение (вычитание) в сумматоре 1 не производится, или с периодом, соответствующим периоду делителя 18 частоты, если выполняется сложение- (вычитание) „ Период импульсов на выходе генератора соответствует длительности такта преобразования (деления на два) в регистре 3. Период импульсов на выходе делителя 18 частоты соответствует длительности такта сЛожения/вычитания в сумматоре 1. Делитель 18 частоты может быть реализован, например, на базе двоичного счетчика, на счетный вход которого поступают импульсы .с выхода генератора 17. Выходом делителя 18 частоты может быть один из выходов счетчика.в зависимости от соотношения длительностей сложения/вычитания деления на два, Если, например, лительность сложения/вычитания превышает длительность деления на два в два раза, выходом делителя частоты будет выход счетчика с весом 1, в четыре раза - выход счетчика с весом 2 и т.д. Если остаток в сумматоре 1 положи телен (потенциал на входе 9 блока 5 управления) и триггер 20 установлен в единицу (на предыдущем такте выпол нялось вычитание), то стробирующий сигнал с выхода элемента 3 ИЛИ проходит через элемент 2 И и элемент 35 ИЛИ, обеспечивая появление сигнала на выходе 11. блока 5 управления, по которому младший бит регистра 2 устанавливается в единицу. Одновременно сигнал с выхода элемента , пройдя через элемент 31 ИЛИ, сбрасывает триггер 20 в нуль. - , , Кроме того, на каждом из первых трех тактов отработки тетрады (потен циаль на первых трех выходах счетчика 13) стробирующий сигнал с выхода ИЛИ 3 проходит через И 27 на выход t3 блока управления. Сигнал с выхоЛ.а 13 обеспечивает деление на два со держимого perHctpa 3. На каждом из четырех тактов отработки тетрады частного, формируемой из положительного остатка (потенциал на первом-четвертом выходах счетчика стробирующий сигнал с выхода элемента ИЛИ проходит через элемент 26 и элемент Зб на выход 12 блока 5 Управления. По сигналу 12 осуществляет ся сдвиг содержимого младшей тетрады регистра 2 влево на один бит. Длительность задержки на элементе Зб со ответствует времени установки младшего бита регистра 2 в единицу по сигналу 11 Одновременно стробирующий сигнал с выхода элемента 3 ИЛИ поступает на счетный вход счетчика 19 и обеспечивает прибавление единицы к его содержимому. ..-f: , После, отработки четырех тактов onределения текущей тетрады частного счетчик 19 переходит в состояние 100 (потенциал на его пятом выходе). Если на вход 9 блока 5 управления пришел сигнал и триггер 23 установлен в единицу (на предыдущем такте в сум маторе 1 выполнялось вычитание); то стробирующий импульс с выхода элемента 3 ИЛИ проходит через элемент г и и элемент 35 ИЛИ, появляясь на выходе 11 блока 5 управления. Дан ный сигнал устанавливает младший бит регистра 2 в единицу. Кроме того, задержанный на элементе 37 потенциал с пятого выхода счетчика 19 походит через элемент 32 ИЛИ и появляется на выходе 10 блока 5 управление По сигналу 10 осуществляется сдвиг содержимого регистра 2 и сумматора 1 в сторону старших разрядов на тетраду. Если в результате отработки текущей Тетрады частного остаток в сумматоре 1 положителен, то потенциал с пятого выхода счетчика 19 проходит через элемент 23 И и элемент 33 ИЛИ, обеспечивая формирование сигнала на выходе 1 блока 5 управления, По данному сигналу в регистр 3 принимается восьмикратный делитель из регистра k. Кроме того, сигнал с выхода k, задержавшись на элементе задержки 38 (длительность задержки определяется временем приёма в регистр 3), поступает на вход установки нуля.счетчика 19 и сбрасывает его в нуль. В результате появляется потенциал на первом выходе счетчика 19. Начинается отработка следующей тетрады частного, Если же в ходе отработки текущей тетрады частного на одном из тактов вычитания в сумматоре 1 образовался отрицательный остаток, то блок 5 управления начинает работать следующим образом. Если на вход 16 блока 5 управления поступит сигнал, то элемент 22 И закрыт, сигнал на выходе 7 не появляется. Поэтому на выходе элемента 3 Или формируются стробирующие импульсы с частотой импульсов генератора 17. На первых трех тактах отработки текущей тетрады аналогично указанному импульсы с выхода элемента 3 ИЛИ проходят через элемент 27 И и появляются на выходе 13 блока 5 управления, обеспечивая деление содержимого регистра 3 на два. К на%ii ViU v l.ri«ri Il I V/ Л, t Л J «lU Ul. 14 ч,алу четвертого такта (потенциал на четвертом выходе счетчика 19) в регистре 3 фиксируется однократный делитель. Кроме того, в результате выполнения вычитания триггер 20 устанавливаётсчя в единицу. (1оэтому стробируЮщие импульсы с выхода элемента 3 ИЛИ проходят через элемент 25 И и, задержавшись на элементе 39, через элемент 35 ИЛИ. Длительность задержку на элементе 39 определяется продолжительностью такта деления на два. Поэтому не следующем после получения отрицательного остатка такте н& вына выходе 11 сигнал не появляется,, младший бит регистра 3 остается в нуп.е. На последующих тактах отработки текущей тетрады на выходе элемента 39 и элемента 35 ИЛИ появляются сигналы обеспечивающие установку младшего бит. регистра 2 в единицу. На четвертом такте сигнал с четвертого выхода счетчика 19 проходит через элемент 31 ИЛИ на вход уетано,в ки ууля триггера 20; Поэтому к концу выполнения четвертого такта триггер 20 сбрасывается в нуль. В связи с этим на выходе 1t последним появляет .ся сигнал, сформированный элeмeнтof 25 И на четвертом такте (на выходе элемента 39 задержки и элемента 35 ИЛИ он появляется на пятом такте) 8 результате выполнения четвертого такта сметчик 19 переходит в состояние 100 (потенциал на его пятом выходе). На пятом такте формируется сигнал на выходе 10 блока 5 управления, по которому в регистре 2 и сумматоре 1 выполняется сдвиг на тетрад влево. При отрицательном остатке в сумматоре 1 (нуль на входе 9), эле- менты 23 И и 33.ИЛИ не. срабатывают, сигнал на выходе 1 блока 5 управления не формируется. Поэтому в регист ре 3 к началу отработки следующей тетрады частного сохраняется код од нократного Делителя, а, на вход установки нуля счетчика 19 сигнал не при ходит. В результате, по стробирующему импульсу с выхода элемента 3 ИЛИ счетчик 19 переходит в состояние 101 (потенциал на его шестом выходе). На шестом такте -по приходу синхросигнала с выхода делителя 18 частоты срабатывает элемент 21 И. Сигнал с его выхода поступает на выход блока 5 управления, обеспечивая сложение в сумматоре 1 его содержимого с содержимым регистра 3 (делителем). Кроме того, сигнал с выхода 8 поступает на вход установки девяти младшей тетрады регистра 2. В последней устанавливается код 100К Одновремен но сигнал с выхода элемента 21 И про ходит через элемент З ИЛИ на счетны вход счетчика 19. Поэтому счетчик 19 переходит в состояние 110 (потенциал на его седьмом выходе), На седьмом такте срабатывают элементы 32, 33 ИЛИ. Сигнал с выхода эл мента 32 ИЛИ поступает на выход 10 блока 5 управления и обеспечивает сдвиг содержимого регистра 2, и сумматора 1 на тетраду влево. Сигнал с выхода элемента 33 ИЛИ поступает на выход 1 блока 5 управления, и через элемент 38 задержки - на вход убтановки нуля счетчика 19. Поэтому в регистр 3 принимается восьмикратный делитель из регистра , а счетчик 19 сбрасывается в нуль. Таким образом, блок 5 управления переходит к отработке следующей тетрады частного. Аналогично в предлагаемом устройстве может быть выполнено деление целых десятичных чисел. При этом восьмикратный делитель в регистре необходимо располагать так, чтобы старшая десятичная цифра однократного делителя занимала в нем вторую тетраду. Предварительное пdлyчeниe восьмикратного делителя может быть выполнено различными способами. Одним из них является получение десятикратного делителя путем сдвига делителя на один десятичный разряд влево с последую1цим двухкратным вычитанием делителя из полученной после сдвига величины. . Данное устройство обеспечивает выпол(71ение.деления п-разрядных десятичных чисел за среднее время, не превышающее величины Тл- n(, 4-.2tn,+ 1 ,5t(,A ) + - 01едЛ(22) + 1п -длительность сравнения согде-держимых трех старших разрядов остатка и текущего кратного делителя; -длительность формирования кратного делителя, используемого на следующем такте - деления на два в регистре 3) ; -длительность двоично-десятичного сложения в сумматоре 1 ; длительность сдвига в регистре 2 частного и в сумматоре 1. среднее время деления десятичных чисел в прототипе составляет величину Tg ij-n-tcA (n-1)-tc.e (23) Деление на два в регистре 3 выполняется без распространения переносов. 1оэтому при больших разрядностях операндов длительность десятичного сложения tcV, как правило, в несколько раз 211 превышает продолжительность деления на два 1ф, tcft 1ф. Длительность сравнения t(p содержимых трех старших разрядов остатка и текущего кратного определяется временем распространения переноса через три разряда схемы 6 сравнения. При больших п tcp в несколько раз меньше, чем ten, tj tcp. Из сравнения выражений (22) и (23) видно, что данное устройство обеспечивает деление десятичных чисел за среднее время меньшее прототипа, если (tcA- 1,6tcp4 0,8.t

л

11

JL /

Фиг.1

/ч

A/S

/ч 473 При реальных соотношениях между с/ ср и. to, справедливых при делении многоразрядных десятичных чисел неравенство (24) выполняется практически всегда. Чем больше разрядность операндов п, тем существеннее tfK превышает правую часть неравенства (2). Поэтому данное устройство наиболее целесообразно использовать при делении многоразрядных .десятичных чисел. В пределе (при n-sco) предложенное устройство позволяет повысить быстродействие в 2,66 раза по сравнению с известным устройством.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Карцев М.А | |||

| Арифметика цифровых машин | |||

| М., Наука, 1969, с | |||

| Телескоп | 1920 |

|

SU525A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для деления п-разрядныхдЕСяТичНыХ чиСЕл | 1979 |

|

SU807282A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1983-10-15—Публикация

1982-04-28—Подача