Предлатаемое устройство относится к области вычислительной техники и может быть применено в устройствах защиты дина.мически распределенной памяти цифровых вычислительных машин.

Известны устройства для защиты памяти, содержащие регистры, дешифраторы и логические схемы.

Недостатком известных устройств является потеря времени при каждом обращении к памяти, обусловленная необходимостью проверки адреса на условие нарушения защиты.

Предлагаемое устройство отличается от известных тем, что в нем выходы базовых регистров соединены с первым в.ходом регистра адреса оперативной памяти, второй вход которого соединен с первым выходом адресной части регистра команд, второй выход которой соединен со входом базовой части адреса, выходы которого соединены со вторыми входами базовых регистров. Первый вход базовых регистров соединен с первым выходом оперативной памяти, первый выход регистра адреса оперативной памяти соединен с первым входом дещифратора адреса оперативной памяти, второй вход которого соединен с выходом клапана обращения. Первый вход последнего соединен с выходом клапана блокировки защиты, а второй вход подключен к шине обращения к оперативной памяти.

Первый вход клапана блокировки защиты соединен с щиной блокировки защиты управляющей области, а его второй вход соединен с первым выходом схемы «ИЛИ, входы которой соединены с выходами дешифратора защищенных страниц. Вход этого дешифратора соединен со вторым выходом регистра адреса оперативной памяти. Второй выход схемы «ИЛИ соединен с первым входом клапана нарушения защиты, второй вход которого соединен с выходом схемы «НЕ, вход которой связан с шиной блокировки защиты управляющей области. Выход дешифратора адреса оперативной памяти соединен со входом оперативной памяти, второй выход которой соединен со входом адресной части регистра команд. Это позволяет устранить недостатки прототипа.

Это позволяет избежать потери времени на проверку нарушения защиты при обращениях к памяти.

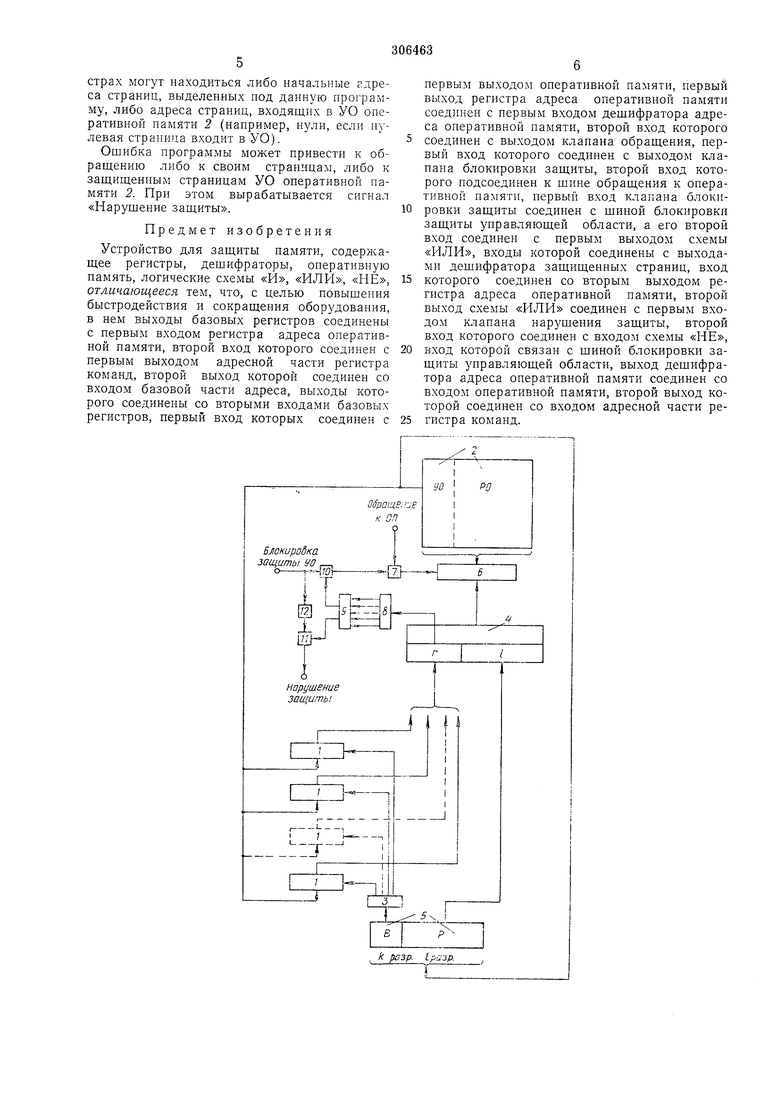

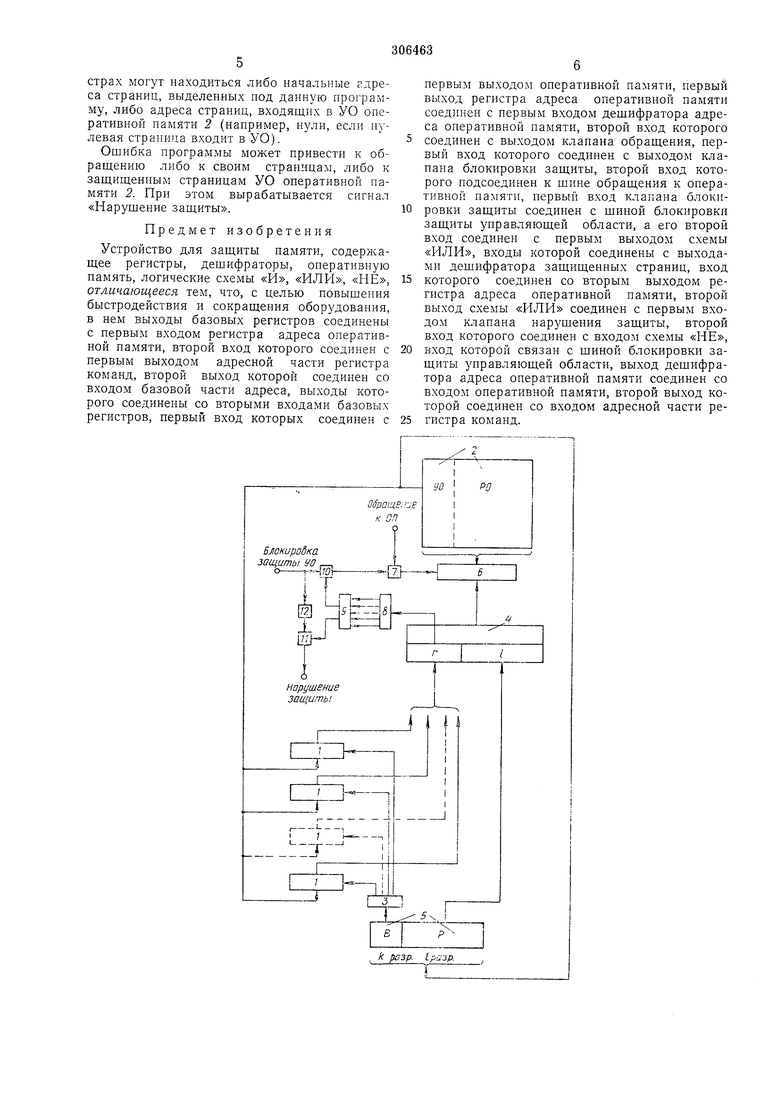

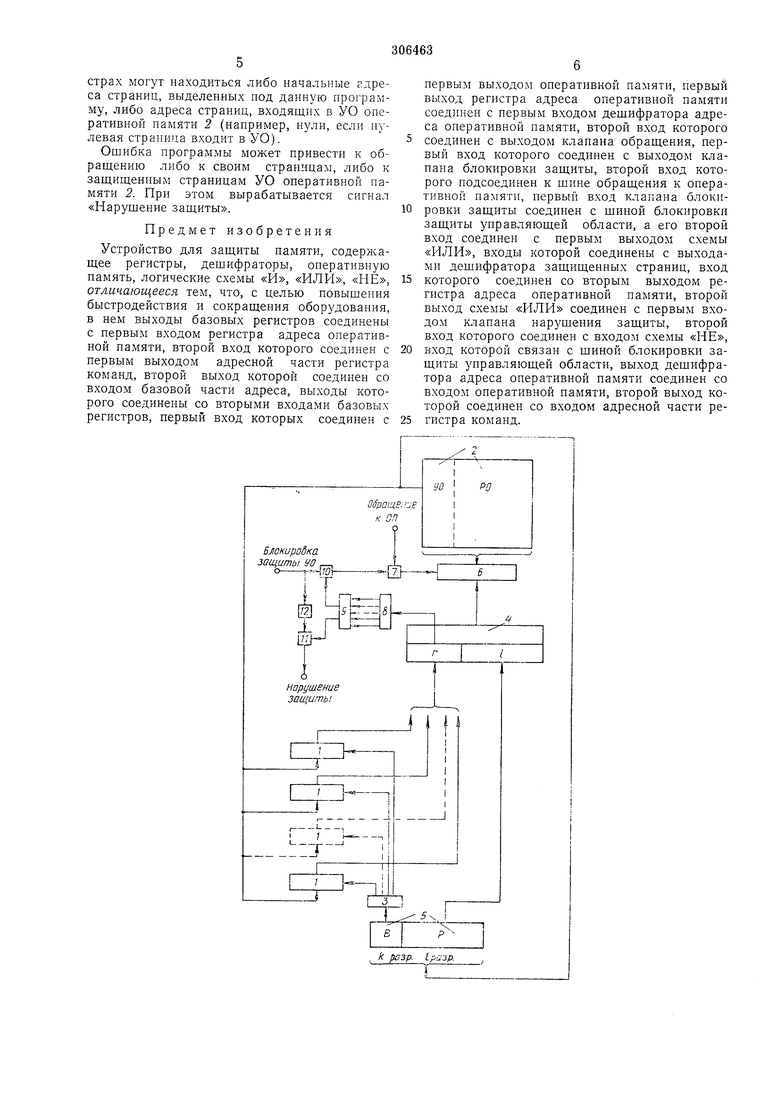

На чертеже приведена функциональная схема устройства.

Базовые регистры / предназначены для хранения начальных адресов страниц памяти, связаны по первому входу с управляющей областью (УО) оперативной памяти 2, по второму входу - с 2 выходами дешифратора базовой части адреса 3, а по выходу - со старшими разрядами регистра адреса оперативной памяти (РгАОП) 4. Адресная часть регистра команд 5 предназначена для хранения условных адресов и по входу связана с рабочей областью (РО) oneративной памяти 2; по первому выходу смещение Р (младшие / разрядов) связано с младшими разрядами регистра 4, а по второму выходу базовая часть В (старшие k разрядов) связана с дешифратором базовой части адреса 3. Дешифратор базовой части адреса 3 предназначен для выбора базового регистра 1, номер которого записан в базовой части адреса В регистра 5, и по входу связан с частью В регистра 5, а по выходу с базовыми регистрами 1. Регистр 4 предназначен для образования физического адреса с дальнейшим обраш,ением по этому адресу, и но первому входу старшие г разрядов связаны с базовыми регистрами /, по второму входу младшие / разрядов-с частью Р регистра 5. По первому выходу регистр 4 связан с дешифратором адреса оперативной памяти 6, а но второму выходу старшие г разрядов связаны с дешифратором заш,иш,енных страниц. Дешифратор адреса оперативной памяти 6 предназначен для выбора ячейки памяти, номер которой записан в регистре 4 и по первому входу связан с регистром 4, по второму входу - с клапаном обращения 7, а по выходу - с оперативной памятью 2. Дешифратор 8 защищенных страниц на т выходов предназначен для выбора страниц, входящих в защищенную УО памяти 2 и по входу связан со старшими разрядами регистра 4, а по выходу - со схемой «ИЛИ 9. Схема «ИЛИ 9 на т входов предназначена для выработки сигнала о наличии в регистре адресов, входящих в УО оперативной памяти 2, и по входу связана с дешифратором 8, по первому выходу - с клапаном (двухвходовая схема «И) блокировки защиты 10, а по второму выходу - с клапаном нарушения защиты 11. Клапан блокировки защиты JO, предназначен для выработки разрешения обращения к УО оперативной памяти 2 при подаче сигнала «Блокировка защиты УО и по первому входу связан с сигналом «Блокировка защиты УО, по второму входу - с выходом схемы «ИЛИ 9, а по выходу - с клапаном обращения 7. Клапан обращения 7 предназначен для выработки обращения к оперативной памяти при подаче сигнала «Обращение к ОП, если не нарушена защита, и по первому входу связан с клапаном блокировки защиты 10, но второму входу - с сигналом «Обращение к ОП, а по выходу - с дешифратором адреса оперативной памяти 6. ИЛИ 9, по второму входу - со схемой НЕ 12, а по выходу - с системой прерываия машины, куда подается сигнал «Нарушеие защиты. Схема «НЕ 12 предназначена для инвертиования сигнала «Блокировка защиты, но ходу связана с сигналом «Блокировка заиты, а по выходу - с клапаном парушеия защиты 11. Оперативная память 2, которая состоит из правляющей (УО), и рабочей (РО) облатей, предназначена для хранения управляющих и рабочих программ и по входу свяана с дешифратором 6. По первому выходу О связана с базовыми регистрами /, а по второму выходу РО - с адресной частью регистра команд. Устройство работает следуюшим образом. Перед началом решения данной программы в базовые регистры / программа-диспетчер, записанная в УО оперативной памяти 2, запосит начальные адреса страниц, отведенных решаемой программе. В ходе решения программы в дешифратор 3 заносятся условные адреса, по которым нужно произвести обращение к памяти. Проиндексированный условный адрес Ay-|5.2 + / + (J)lmod2 - :5-2 + P где (I) - содержимое индекс-регистра с помером I. По значению В дешифратор базовой части 3 выбирает один из 2- базовых регистров RB. Физический адрес Аф образуется в регистре 4, в старшие г разрядов которого засылается содержимое выбранного базового регистра Rs, а в младшие / разрядов - смещение Р из регистра 5. Лф + Я , где Гв - содержимое базового регистра К УО оперативной памяти 2, содержащей целое число страниц, можно произвести обращепие, если подается сигнал «Блокировка защиты. Если в регистре находится адрес, входящий в одну из страпиц УО, дешифратор 8 вырабатывает сигн.ал, который, пройдя через схему «ИЛИ 9, поступает на вход клапанов 10 и 11. Если подап сигнал «Блокировка защиты (при работе управляющих программ и в пекоторых других специальных случаях), сигнал «Обращение к ОП, пройдя через клапан 7 производит обращение по адресу в регистр 4. При этом сигнал «Нарушение защиты не вырабатывается, так как на вход клапана 11 сигнал «Блокировка защиты УО подается через схему «НЕ 12. Если же сигнала «Блокировка защиты УО нет, обращение к памяти не происходит (заперты клапаны 10 и 7) и клапан 11 вырабатывает сигнал «Нарушение защиты, так как на выходе схемы «НЕ 12 есть сигнал. Защита намяти осуществляется благодаря соблюдению следующего условия: в базовых регистрах могут находиться либо начальные адреса страниц, выделенных под данную программу, либо адреса страниц, входящих в УО оперативной памяти 2 (например, нули, если i левая страница входит в УО).

Ошибка программы может привести к обращению либо к своим страницам, либо к защищенным страницам УО оперативной памяти 2. При этом вырабатывается спгнал «Нарущение защиты.

Предмет изобретения

Устройство для защиты памяти, содержащее регистры, дешифраторы, оперативную память, логические схемы «И, «ИЛИ, «ИЕ, отличающееся тем, что, с целью новышения быстродействия и сокращения оборудования, в нем выходы базовых регистров соединены с первым входом регистра адреса оперативной памяти, второй вход которого соединен с первым выходом адресной части регистра команд, второй выход которой соединен со входом базовой части адреса, выходы которого соединены со вторыми входами базовых регистров, первый вход которых соединен с

первым выходом оперативной памяти, первый выход регистра адреса оперативной памяти соединен с первым входом дешифратора адреса оперативной памяти, второй вход которого соединен с выходом клапана обращения, первый вход которого соединен с выходом клапана блокировки защиты, второй вход которого подсоединен к шине обращения к оперативной памяти, первый вход клапана блокировки защиты соединен с шиной блокировки защиты управляющей области, а его второй вход соединен с первым выходом схемы «ИЛИ, входы которой соединены с выходами дешифратора защищенных страниц, вход которого соединен со вторым выходом регистра адреса оперативной памяти, второй выход схемы «ИЛИ соединен с первым входом клапана нарушения защиты, второй вход которого соединен с входом схемы «НЕ, вход которой связан с шиной блокировки защиты управляющей области, выход дешифратора адреса оперативной памяти соединен со входом оперативной памяти, второй выход которой соединен со входом адресной части регистра команд.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления оперативной памятью | 1985 |

|

SU1291992A1 |

| Устройство для динамического преобразования адресов | 1980 |

|

SU903878A1 |

| Запоминающее устройство | 1988 |

|

SU1608746A1 |

| Устройство адресации оперативной памяти | 1986 |

|

SU1417004A1 |

| Параллельный процессор | 1985 |

|

SU1315989A1 |

| Устройство для управления виртуальной памятью | 1980 |

|

SU955076A1 |

| Вычислительная система | 1977 |

|

SU692400A1 |

| Устройство для контроля хода программ | 1984 |

|

SU1191912A1 |

| Электронная вычислительная машина для ускоренной обработки запросов прерываний | 1988 |

|

SU1621029A1 |

| Процессор для выполнения математических операций | 1986 |

|

SU1381533A1 |

Даты

1971-01-01—Публикация