Изобретение относится к вычислительной технике и может быть использовано при построении надежных микропроцессорных устройств, нечувствительных к сбоям программы. $

Цель изобретения - повышение достовернрсти контроля хода программы.

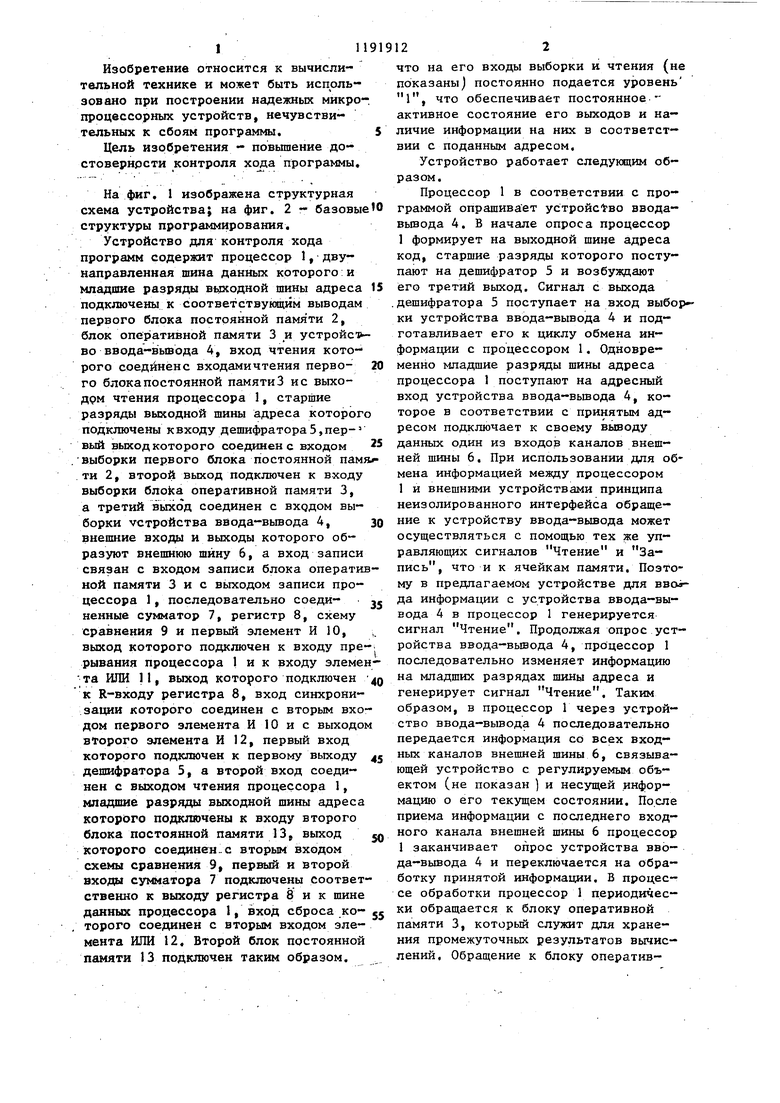

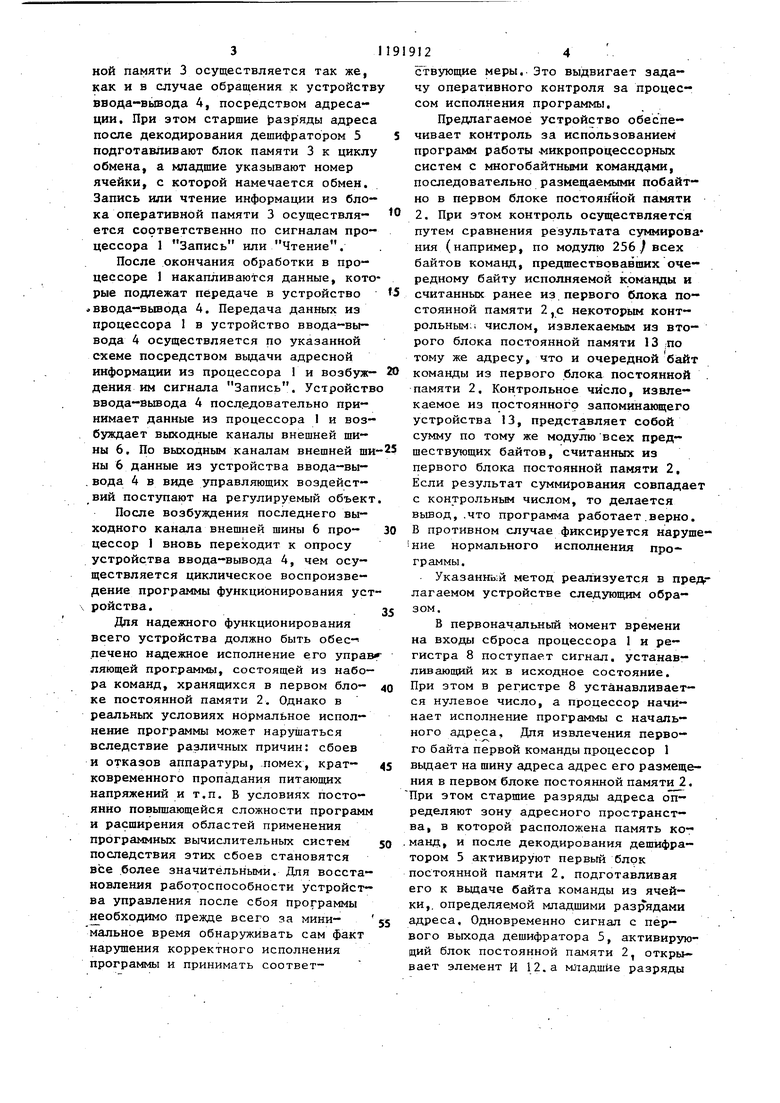

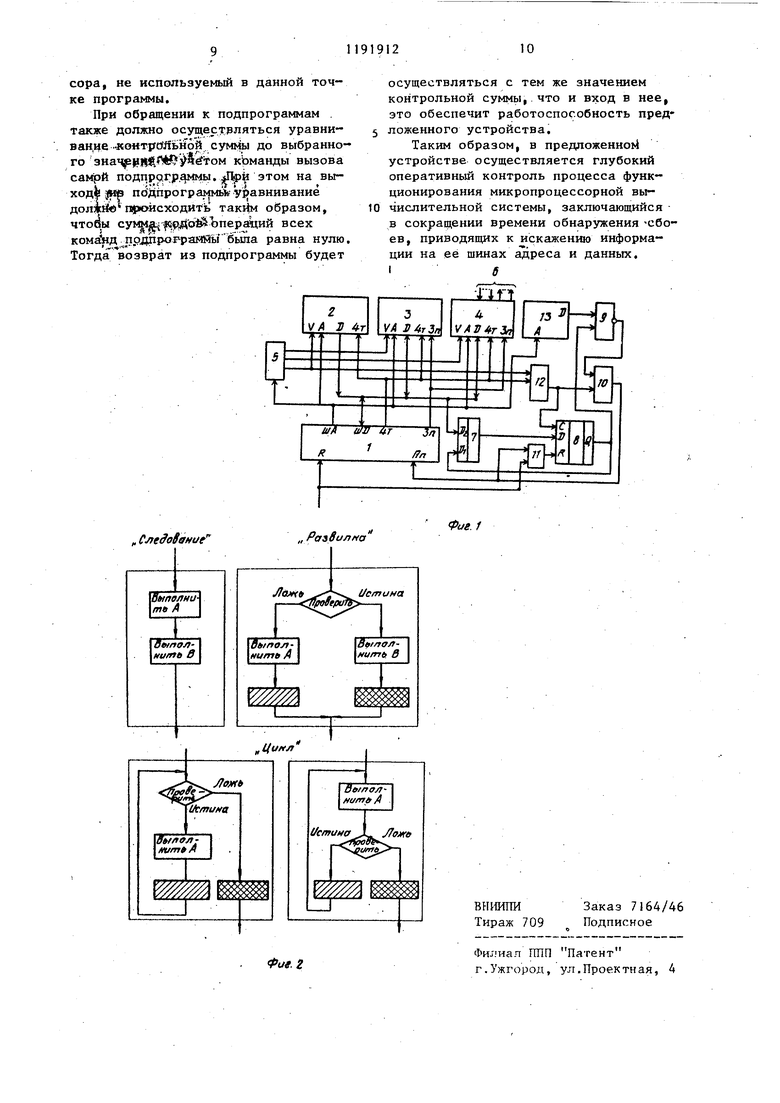

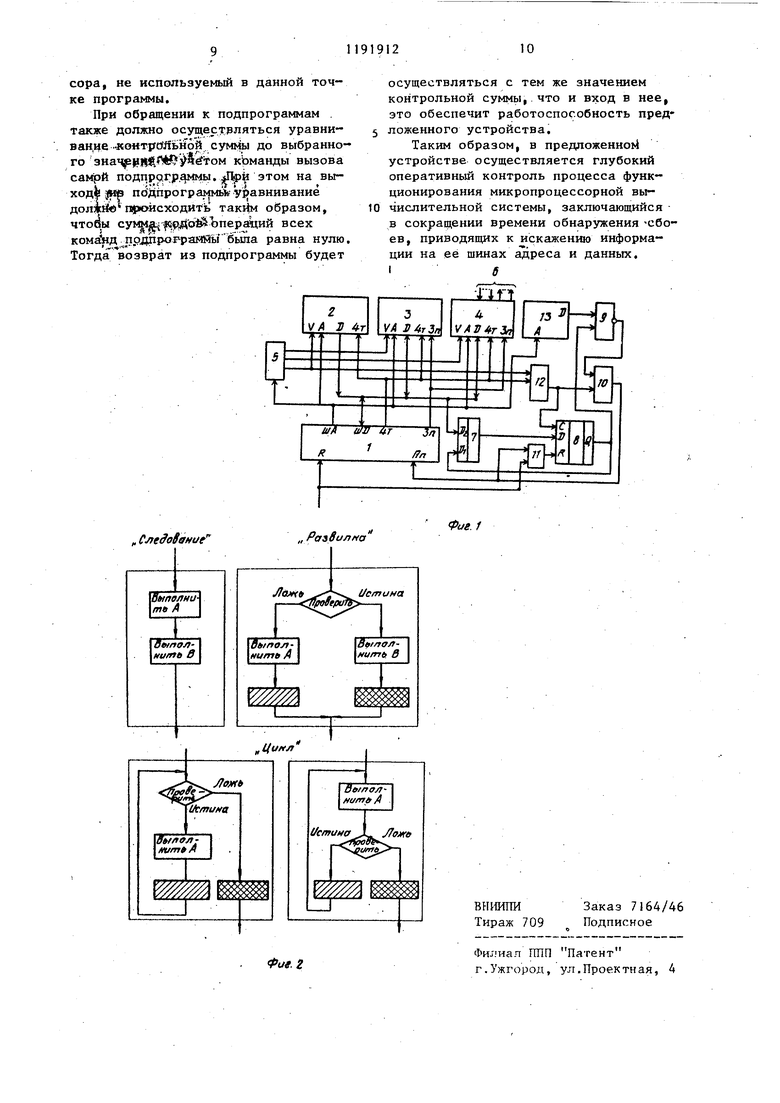

На фиг. 1 изображена структурная схема устройства; на фиг. 2 - базовыеО структуры программирования.

Устройство для контроля хода программ содержит процессор 1, двунаправленная шина данных которого:и младшие разряды выходной шины адреса 15 подключены к соответствующим выводам первого блока постоянной памяти 2, блок оперативной памяти 3 и устройст во ввода-вьтода 4, вход чтения которого соедйненс входамичтения перво- 20 го блока постоянной памяти 3 и с выходрм чтения процессора 1, старшие разряды выходной шины адреса которого подключены к входу дешифратора 5, пер- вый выход которого соединена входом 25 Выборки первого блока постоянной 2, второй выход подключен к входу выборки бло4са оперативной памяти 3, а третий выход соединен с вхддом выборки устройства ввода-вывода 4, ЗО внешние входы и выходы которого образуют внешнюю шину 6, а вход записи связан с входом записи блока оперативной памяти 3 и с выходом записи процессора 1, последовательно соеди- j ненные сумматор 7, регистр 8, схему сравнения 9 и первый элемент И 10, ,. выход которого подключен к входу прерывания процессора 1 и к входу элемен- та ИЛИ П, выход которого подключен /40 к R-входу регистра 8, вход синхронизации которого соединен с вторым входом первого элемента И 10 и с выходок второго элемента И 12, первый вход которого подключен к первому выходу 45 дешифратора 5, а второй вход соединен с выходом чтения процессора 1, младшие разряды выходной шины адреса которого подключены к входу второго блока постоянной памяти 13, выход которого соединен-С вторым входом схемы сравнения 9, первый и второй входы сумматора 7 подключены соответственно к выходу регистра 8 и к шине данных процессора 1, вход сброса которого соединен с вторым входом элемента ИЛИ 12. Второй блок постоянной памяти 13 подключен таким образом.

что на его входы выборки и чтения (не показаны) постоянно подается уровень

что обеспечивает постоянное

активное состояние его выходов и наличие информации на них в соответствии с поданным адресом.

Устройство работает следующим образом.

Процессор 1 в соответствии с программой опрашивает устройство вводавьшода 4. В начале опроса процессор 1 формирует на выходной шине адреса код, старшие разряды которого поступают на дешифратор 5 и возбуждают его третий выход. Сигнал с выхода .дешифратора 5 поступает на вход выбо ки устройства ввода-вывода 4 и подготавливает его к циклу обмена информации с процессором 1. Одновременно младшие разряды шины адреса процессора 1 поступают на адресный вход устройства ввода-вьшода 4, которое в соответствии с принятым адресом подключает к своему выводу данных один из входов каналов внешней шины 6. При использовании для обмена информацией между процессором 1 и внешними устройствами принципа неизолированного интерфейса обращение к устройству ввода-вывода может осуществляться с помощью тех же управляющих сигналов Чтение и Запись, что и к ячейкам памяти. Поэтому в предлагаемом устройстве для ввода информа1;ии с устройства ввода-вывода 4 в процессор 1 генерируется сигнал Чтение. Продолжая опрос устройства ввода-вьшода 4, процессор 1 последовательно изменяет информацию на младших разрядах шины адреса и генерирует сигнал Чтение. Таким образом, в процессор 1 через устройство ввода-вьшода 4 последовательно передается информация со всех входных каналов внепшей шины 6, связывающей устройство с регулируемым объектом (не показан и несущей информацию о его текущем состоянии. По.сле приема информации с последнего входного канала внешней шины 6 процессор 1 заканчивает опрос устройства ввода-вывода 4 и переключается на обработку принятой информации. В процессе обработки процессор 1 периодически обращается к блоку оперативной памяти 3, которьй служит для хранения промежуточных результатов вычислений. Обращение к блоку оператив31191

ной памяти 3 осуществляется так же, как и в случае обращения к устройству ввода-вывода 4, посредством адресации. При этом старшие разряды адреса после декодирования дешифратором 5 5 подготавливают блок памяти 3 к циклу обмена, а младшие указывают номер ячейки, с которой намечается обмен. Запись или чтение информации из блока оперативной памяти 3 осуществля- ется соответственно по сигналам процессора 1 Запись или Чтение.

После окончания обработки в процессоре 1 накапливаются данные, которые подлежат передаче в устройство 5

ввода-вывода 4. Передача данных из процессора 1 в устройство ввода-вывода 4 осуществляется по указанной схеме посредством выдачи адресной информации из процессора 1 и возбуж- 20 дения им сигнала Запись. Устройство ввода-вывода 4 последовательно принимает данные из процессора 1 и возбуждает выходные каналы внешней щины 6. По выходным каналам внешней ши-25 ны 6 данные из устройства ввода-вы-

вода 4 в виде управляющих воздействий поступают на регулируемый объект.

После возбуждения последнего выходного канала внешней шины 6 про- 30 цессор 1 вновь переходит к опросу устройства ввода-вывода 4, чем осуществляется циклическое воспроизведение программы функционирования устройства.3

Для надежного функционирования всего устройства должно быть обес- печено надежное исполнение его управ ляющей программь, состоящей из набора команд, хранящихся в первом бло- 40 ке постоянной памяти 2. Однако в реальных условиях нормальное исполнение программы может нарушаться вследствие различных причин: сбоев и отказов аппаратуры, .помех, крат- 45 ковременного пропадания питающих напряжений и т.п. В условиях постоянно повышающейся сложности программ и расширения областей применения программных вычислительных систем 50 последствия этих сбоев становятся все более значительными. Для восстановления работоспособности устройства управления после сбоя программы необходимо прежде всего за мини- 55 мальное время обнаруживать сам факт нарушения корректного исполнения программы и принимать соответ9124

сГтвующие меры.. Это выдвигает задачу оперативного контроля за процессом исполнения программы.

Предлагаемое устройство обеспечивает контроль за использованием программ работы микропроцессорных систем с многобайтными командами, последовательно размещаемыми побайтно в первом блоке постоянной памяти 2. При этом контроль осуществляется путем сравнения результата суммирова ния (например, по модулю 256/ всех байтов команд, предшествовавших очередному байту исполняемой команды и считанных ранее из первого блока постоянной памяти 2,с некоторым контрольным; числом, извлекаемым из второго блока постоянной памяти 13 .по тому же адресу, что и очередной байт команды из первого блока постоянной памяти 2. Контрольное число, извлекаемое из постоянного запоминающего устройства 13, представляет собой сумму по тому же модулю всех предшествующих байтов, считанных из первого блока постоянной памяти 2, Если результат суммирования совпадае с контрольньм числом, то делается вьшод, .что программа работает.верно, В противном случае фиксируется наруш ние нормального исполнения программы.

Указаннь;й метод реализуется в пре лагаемом устройстве следующим образом.

В первоначальный момент времени на входы сброса процессора 1 и регистра 8 поступает сигнал, устанав- ливающий их в исходное состояние. При этом в регистре 8 устанавливается нулевое число, а процессор начинает исполнение программы с начального адреса. Для извлечения первого байта первой команды процессор 1 выдает на шину адреса адрес его размещения в первом блоке постоянной памяти 2.

При этом старшие разряды адреса определяют зону адресного пространства, в которой расположена память ко-

.манд, и после декодирования дешифратором 5 активируют первый блрк постоянной памяти 2. подготавливая его к вьщаче байта команды из ячейки,, определяемой младшими разрядами адреса. Одновременно сигнал с первого выхода дешифратора 5, активирующий блок постоянной памяти 2, открывает элемент И 12. а младшие разряды

адреса поступают на второе постоянное запоминающее устройство 13, что обеспечивает появление на его выходе первого контрольного числа, равного нулю. Схема сравнения 9 сравнивает контрольное число с числом, находящимся в регистре 8, и вследствие их равенства формирует сигнал, запирающий элемент И 10. Для приема байта команды из блока постоянной памяти 2 процессор генерирует сигнал Чтение, что вызывает появление считываемого байта команды на шине данных и его занесение в процессор. Одновременно сигнал Чтение проходит через открытый элемент И 12 и не про ходит через закрытый элемент И 10, При этом байт команды, находящийся на шине данных, суммируется сумматором 7 с числом, находящимся в регистре 8, В момент окончания сигнала Чтение на выходе элемента И 12 формируется сигнал, записывающий результат суммирования с выхода сумматора

7в регистр 8, в котором он запоминается до следующего цикла чтения очередного байта команды из блока постоянной памяти 2. При записи в регистр 8 нового значения равенство чисел на входах схемы сравнения нарушается и она вьщает сигнал, отпиракиций элемент И 10. Но так как в это время сигнал на втором его входе уже отсутствует, то это не приводит к формированию сигнала на выходе этого элемента И 10. В дальнейшем при правильной работе программы принцип действия устройства совершенно иденти чен указанному. Для чтения очередного байта из блока постоянной памяти 2 процессор снова формирует на младшихразрядах адреса адрес ячeйкиJ в которой он находится. При этом

из постоянного запоминающего устройства 13 по этому адресу считывается новое значение контрольного числа, совпадающего с состоянием регистра

8в этот момент времени, что обеспечивает закрывание элемента И 10

.и т.д. Таким образом, при правильной работе программы на выходе элемента И 10, т.е. на входе прерывания процессора, никогда не появится сигнал прерывания, свидетельствующий о сбое программы. При обращении процессора 1 к блоку оперативной памяти 3 или устройству ввода-вывода 4 элемент И 12 останется закрытым выходным

сигналом с дешифратора 5, так как адресная зона, отведенная этим устройствам, при использовании принципа неизолированного интерфейса не совпадает с адресной зоной, отведенной блоку постоянной памяти 2.

Нарушение нормального хода программы может быть вызвано, например, сбоем счетчика команд в процессоре или отказом адресных линий в шине ад peca,j4To приводит к искажению информации на шине адреса и нарушению последовательности выбора команд ли бо к отказу ячеек блока постоянной памяти 2, или отказу линий связи в шине данных, это приводит к чтению неверных кодов команд из блока постоянной памяти 2. однако предлагаемое устройство обеспечивает выявление подобных нарушений нормального хода прграммы. Действительно, при искажении информации на адресной шине из постоянного запоминающего устройства 1 будет извлечено контрольное слово, не соответствующее верному состоянию регистра 8. При искажении информации на шине данных состояние регистра 8 не будет соответствовать верному кон трольному слову на выходе постоянного запоминающего устройства 13. Однако в обоих случаях схема срав- нения 9 зафиксирует неравенство чисе на ее входах и откроет элемент И 10. В результате этого сигнал с выхода элемента И 12, появляющийся при обращении к постоянному запоминающему устройству 2, пройдет через открытый элемент И 10 на вход прерьшания процессора. При этом процессор пе- рейдет на программу обработки прерывания, которая определит соответствующие меры защиты от возникшего нарушения нормального хода программы. В простейшем случае-управляющая программа может быть запущена с начального адреса. Переход на программу обработки прерьшания при поступ- лении запроса прерывания обеспечивается подачей напряжения +12 В на вывод системного контроллера, т.е. на выход подтверждения прерывания.

Таким образом, в предлагаемом устройстве реализуется контроль за правильностью работы программы. При нарушениях ее нормального исполнения вызванного сбоем или нарушением информации на адресной шине, либо искажением кодов команд программы.

контроль оперативно выявляет это и осуществляется быстрый перезапуск устройства. В результате этого функции программы либо восстанавливаются за минимальный промежуток времени что позволяет сохранить высокое качество управления регулируемым объектом, либо минимизируются последствия сбоев в случае их абсолютной недопустимости.

Однако использование предлагаемого устройства для контроля функционирования микропроцессорной системы налагает некоторые ограничения- на ее программирование. Без учета этих ограничений в предложенном устройстве обеспечивается контроль лишь линейных участков программы. Линейный участок программы при широко распространенном структурном подходе к программированию(Хьюз Дж. Мичтом Дж. Структурный подход к программированию. М.: Мир, 1980 )называется базовой структурой Следование. Однако этой структуры недостаточно, чтобы-

представить даже самые простые практические программы. Логическая структура любой сколь угодно сложной программы может быть выражена комбинацией трех базовых структур: указанной структуры Следование, Развилка и Цикл. Все эти базовые структуры приведены на фиг. 2. При этом структура Цикл может иметь

две разновидности.. Каждая базовая структура программы имеет один йход и один выход. Однако внутри базовых структур Развилка и Цикл осуществляется ветвление : вычислительного процесса с последующим объединением ветвей. Объединение ветвей программы осуществляется обращением по од ному и тому же адресу после прихода ветвей программы. Суммы кодов операций, находящихся в различных ветвях, в общем случае не совпадают. В результате этого при объединении ветвей программы без принятия дополнительных мер предложенное устройство зафиксирует сбой программы, хотя такового и нет. Для исключения, этого явления необходимо искусственно выравнивать суммы кодов операций перед каждым .объединением ветвей. Это легко обеспечивается путем размещения перед каждой точкой объединения ветвей дополнительных управляющих команд, не имеющих функционального зна-

чения с точки зрения процесса решения задачи, решаемой микропроцессорной системой. Эти команды изображены .на фиг. 2 заштрихованными прямоугольниками, причем их различная штриховка подчеркивает различное значение (уравнивание сумм кодов операций может осуществляться до нулевого значения ), При этом вход в каждую базо0вую структуру программы и выход иэ нее будет происходить с нулевым значением контролируемойсуммы, т.е.нулевым состоянием регистра 8. Недостатком уравнивания до нулевых зна5чений контролируемой суммы является то, что сбои программы, приводящие к пропуску целого. количества ее базовых структур, не будут обнйру- жены.

0

Дпя обнаружения таких сбоев значения контрольной суммы кодов операций при выходе из различных базовых структур должны быть различны. Проще всего это значение контрольной

5 суммы сопоставить с номером базовой структуры в полной логической структуре программы. При этом в базовой структуре Цикл в зацикливающей ветви программы уравнивание должно

0 осуществляться довходного значения контрольной суммы, т.е. номера предыдущей базовой структуры, а в выходной ветви - до выходного значения контрольной суммы, т.е. номера выпол5ненной базовой структуры.

В простейшем случае уравнивание контрольной суммы может быть реализовано одной единственной командой, в качестве которой в системе, исполь0зующей многобайтные команды, удобно использовать команды с непосредственной адресацией. Учитывая, что суммирование кодов операций осуществляется по некоторому модулю во вто5ром байте команды, считываемой из блока постоянной памяти 2, всегда можно указать число, дополняющее контрольную сумму до заданного значения. Определение величины урав0нивающего числа может осуществлять ся либо программистом в процессе разработки программы, либо автоматически с помощью программы ассемблера при трансляции разработанной

5 рабочей программы в объектную программу. При этом в качестве объекта воздействия уравнивающей команды дол жен. выбираться регистр микропроцес-

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля программ | 1986 |

|

SU1332323A1 |

| Устройство для контроля хода программ | 1988 |

|

SU1545223A1 |

| Устройство для контроля микропроцессорной системы | 1987 |

|

SU1474650A2 |

| Устройство для контроля микропроцессора | 1989 |

|

SU1693610A2 |

| Устройство для обмена информацией | 1987 |

|

SU1497619A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1988 |

|

SU1529236A1 |

| Внешнее устройство управления | 1978 |

|

SU736100A1 |

| Устройство для контроля хода программ | 1987 |

|

SU1481775A1 |

| Устройство для контроля выполнения программ | 1987 |

|

SU1434439A1 |

| СПОСОБ ПОВЫШЕНИЯ НАДЕЖНОСТИ МИКРОЭВМ | 2015 |

|

RU2615314C1 |

УСТРОЙСТЮ ДЛЯ КОНТРОЛЯ ХОДА ПРОГРАММ, содержащее первый блок постоянной памяти, блок оперативной памяти и дешифратор, причем выход первого блока постоянной памяти, вход и выход блока оперативной памяти через двунаправленную шину данных соединены с информационным входом выходом устройства, входы чтения первого блока постоянной памяти и блока оперативной памяти соединены с вхогдом чтения устройства, группа адресных входов устройства соединена с группой входов дешифратора, с группами адресных входов первого блока постоянной памяти и блока оперативной памяти, первый и второй выходы дешифратора соединены с входами обращения соответственно первого блока постоянной памяти и блока оперативной памяти, вход записи устройства соединен с входом записи блока оперативной памяти, отличающееся тем, что, с целью повьшгения достоверности контроля хода программы, в устройство введены сумматор, регистр, схема сравнения, первый и второй элементы И, элемент ИЛИ и второй блок постоянной памяти, причем информационный вход устройства соединен с входом первого операнда сумматора, выход которого соединен- с информационным входом регистра, группа адресных входов устройства соединена с адресным входом второго блока постоянной памяти, информационный выход которого сое§ динен с первым входом схемы сравнения, выход которой соединен с первым входом первого элемента И, первый выход дешифратора и вход чтения устройства соединены соответственно S с первым и вторым входами второго и элемента И, выход которого соедиИен с тактовым входом регистра и с вто- . рым входом первого элемента И, выгсо со ход которого является выходом ошибки устройства и соединен с первым входом элемента ИЛИ, вход начальной уста5 новки устройства соединен с вторым входом элемента ИЛИ, выход которого соединен с входом сброса регистра, информационный выход регистра соединен с вторым входом схемы сравнения и с входом второго операнда сумматора.

| Устройство для контроля хода программ | 1980 |

|

SU894713A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| ЗАКЛЕПОЧНОЕ СОЕДИНЕНИЕ | 1989 |

|

RU2035633C1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для видения на расстоянии | 1915 |

|

SU1982A1 |

Авторы

Даты

1985-11-15—Публикация

1984-05-16—Подача