4

Изобретение относится к вычисли- терьной технике и может быть использовано в ЭВМ с оперативной памятью, объем которой больше области адреса- ЦИИ операндов в системе команд.

, Цель изобретения - повышение быстродействия устройства.при обращении к разным блок .-т памяти,

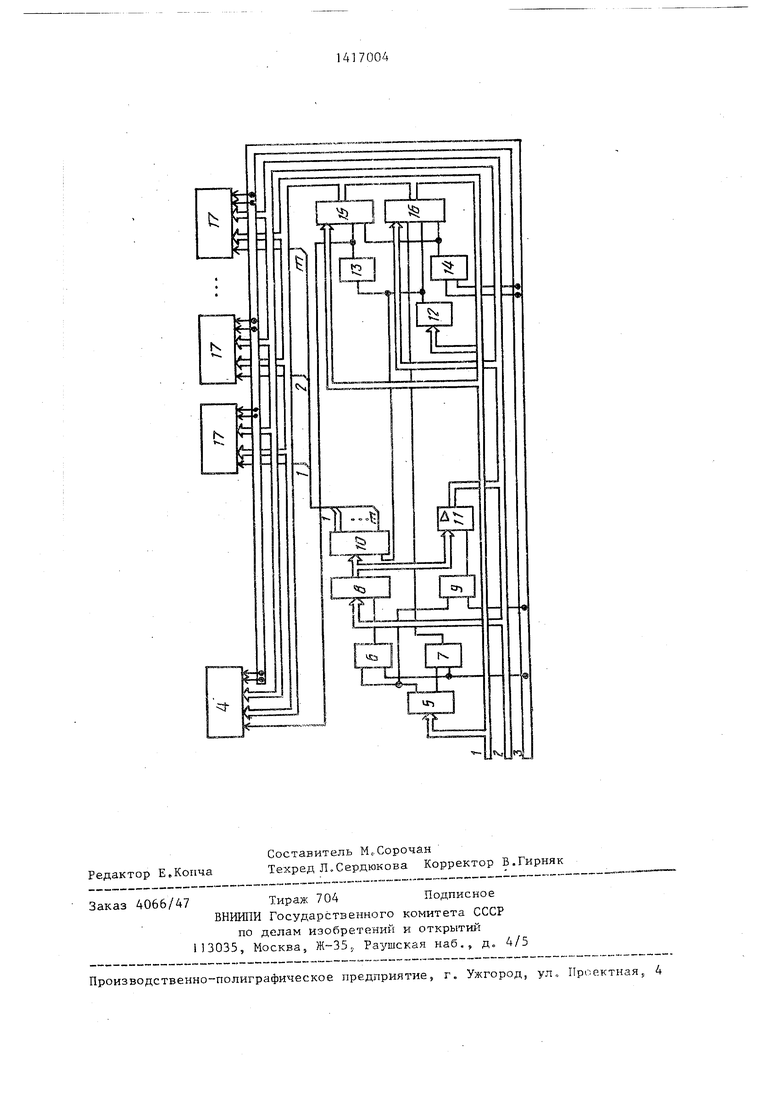

На чертеже приведена функциональ- ная схема устройства.

I Устройство состоит иэ шины 1 адре- с|а, шины 2 данных, шины. 3 управления, б1лока 4 памяти программ, дешифратора 5, элементов И 6 и 7, регистра 8, э лемента И 9, дешифратора 10, блока И |анальных передатчиков, элемента И 12, элемента НЕ 13, элемента ИЛИ J4, регистров 15 и 16, блоков 17 памяти данных.

: Младшие разряды шины 1 адреса ттод- Цлючены к младшим разрядам адресных входов блока 4 памяти программ и блоков 17 памяти дайных, а также дешифратору 5. Старшие разряды шины 1 адреса подключены к информационным входам регистра 15 и входам элемента И 12, выход которого подключен к входам выбор . ки регистра 16, дешифратора 10 и -через элемент НЕ 13 к входу выборки регистра 15 и входу выборки блока 4 памяти программ. Шина 2 данных под ключена к информационным входам регистров 8 и J6, блокам 4 и 37 памяти и выходам блока JJ канальных передат- чиков.

Шина 3 управления состоит из нескольких разрядов. Разряд ввод шины 3 подключен к одному из входов элемента И 9. .Разряд вывод шины 3 управле- НИН подключен к входам элементов И 6 и 7.

Разряды ввод и вывод шины 3 управления подсоединены соответственно к входам чтения и записи блока 4 памя- ти программ, блоков 17 памяти, а также к входам элемента ИЛИ 14, выход которого подключен к входам выборки регистров 16 и 15.

Устройство работает следуюш,им образом.

Устройство позволяет осуш,ествлять адресацию ячеек памяти путем его предварительного программирования, т,е„ указания номера блока памяти и страницы внутри блока, к которой производится обращение. Обраш.вние к блоку 4 памяти программ производится

без предварительного программирования устройства.

Номер блока и номер страницы запоминается соответственно в регистрах 8 и 16. Выбор этих регистров осуществляется путем присвоения им условных собственных номеров в системе внешних устройств ЭВМ,, использующей данное устройство адресации. Номер поступает по .шине 1 адреса на дешифратор 5 который опознает собственный номер регистра 8 или .16 и разрешает прохождение через элемент И 6 или 7 импульса записи, поступаюш,его по линии вывод шины 3 управления, на вход записи регистра 8 или 16. Этим импульсом соответственно записываются поступаю- ш,ие по шине 2 данных номер блока в регистр 8 или номер страницы в регистр 16. Выборка соответствующего блока 17 памяти осуществляется при помощи дешифратора 10.

Блок 11 канальных передатчиков с трехстабильным выходом, управляемый сигнал Ввод выдает в шину данных информацию с регистра В при необходимости контроля его состояния.

Многостабильные регистры 15 и 16 включены таким образом, -что при подаче сигналов выборки на их входы выборки регистр 15 разрешает прохождение сигнала с информационных входов на выходы, а на выход регистра 16 поступает информация, записанная в него ранее.

Количество страниц в каждом из блоков памяти определяется количеством старших разрядов .шины 1 адреса, заведенных на регистр 15 и элемент И 12. Например, если к ним подключено два разряда, то каждый из блоков 17 памяти разбит на четыре страницы .

Устройство работает следующим образом.

Л р и м е р. Пусть каждый из блоков 17 памя ти имеет 64 К байт памяти и разбит на; 4 страни: . памяти, т,е, для адресации страницы используются два старших разряда шины адреса. Блок 4 памяти программ имеет 48 К байт памяти. Поле адресации условно делится на две зоны: первая составляет 48 К байт, вторая - остальные V 6 К б аи т .

Если адрес требуемой Я11ейки находится в пределах nepBoii зоны, т.е. хотя бы один из двух старших р.чзрядов кода адреса равен нулю, запрещающий потенциал подается на стробирую- щий вход дешифратора 10 и этим запрещается выборка блока 17 памяти. Раз- решающий потенциал с выхода элемента НЕ 3 подается на вход выборки блока 4 памяти и на вход выборки регистра 15, на второй вход выборки которого через элемент ИЛИ 14 поступает сиг нал с разрядов вывод или ввод шины 3 управления. В этом случае разрешается прямое прохождение информации с входа регистра 15 на его выход. ким образом, два старших разряда По- ступают на адресные входы блоков 4 и 17 памяти .через регистр J5, мдад- шие - по шине , а доступ разрешен к блоку 4 памяти программ.

Когда адрес ячейки находится во второй зоне адресного поля, то два старших разряда кода адреса равны единице и разрешаюш;ий потенциал на выходе элемента И 12 разрешает прохождение сигнала выборки через дешифра- тор 10 на вход выборки соответствующего блока 17 памяти, одновременно поступая на второй вход выборки регистра 16. В таком режиме осуществляется выдача на выходы регистра запи- санных в него двух разрядов (номера страницы). Таким образом, на адресных входах блоков 4 и 17 памяти формируется адрес, старшие разряды которого определяются значением, записанным в регистре 16, а младшие поступают не-, посредственно с шины 1 адреса.

Регистр 15 И блок 4 памяти отключаются от шины 1 адреса путем подачи запирающего сигнала с выхода инвер- тора 13.

Адресация поля блока 4 памяти программ осуществляется непосредственно, а поля внутри страницы памяти - кос- венно при помощи младших разрядов. Старшие разряды должны быть всегда равными единице.

Формула изобретения

Устройство адресации оперативной памяти, содержащее два дешифратора, два элемента И, первый регистр, выходы которого соединены с информацион- ными входами первого дешифратора,выходы которого образуют группу выходов выбора блоков памяти устройства, группа входов второго дешифратора соединена с двухнаправленной адресной шиной устройства, первый выход второго дешифратора соединен с первыми входами первого и второго элементов И, вторые входы которых соединены соответственно с вxoдa ш Вывод и Ввод устройства, первого элемента И соединен с входом записи первого регистра, отличающееся тем, что, с целью повышения быстродействия устройства при обращениях к разным блокам памяти, в Него введены второй и третий регистры, элемент НЕ, элемент ИЛИ, третий и четвертый элементы И, блок канальных передатчиков, информационные входы которого соединены с группой выходов первого регистра, а группа выходов соединена с двухнаправленной шиной данных устройства, выход второго элемента И соединен с управляюш 1м входом блока канальных передатчиков, информационные входы второго регистра соединены с группой старших разрядов адресной шины устройства, второй выход второго дешифратора соединен с первым входом третьего элемента И, которого соединен с входом записи второго регистра, вход Вывод устройства соединен с вторым входом третьего элемента И и первым входом элемента ИЛИ, выход которого соединен с входами выбора второго и третьего регистров, группа старших разрядов шины адреса соединена с входами четвертого элемента И, выход которого соединен с входом разрешения выбора второго регистра стробирующим входом второго дешифратора и входом элемента НЕ, выход которого соединен с входом разрешения выбора третьего регистра и является выходом выбора блока памяти программь устройства ,вхид Ввод устройства соединен с вторым входом элемента ИШ двухнаправленная шина данных устройства соединена с информационными входами первого и второго регистров, выходы второг о и третьего регистров поразрядно объединены через монтажное ИЛИ и образуют двухна- направленную адресную шину старших разрядов блоков памяти устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с произвольной выборкой | 1988 |

|

SU1548790A1 |

| Запоминающее устройство | 1989 |

|

SU1695382A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ПАМЯТЬЮ | 1991 |

|

RU2010318C1 |

| Формирователь импульсных последовательностей для контроля запоминающих модулей на цилиндрических магнитных доменах | 1987 |

|

SU1513514A1 |

| МИКРОЭВМ | 1994 |

|

RU2108619C1 |

| Параллельный процессор | 1985 |

|

SU1315989A1 |

| МИКРОПРОЦЕССОРНАЯ СИСТЕМА УПРАВЛЕНИЯ ТЕХНОЛОГИЧЕСКИМИ ПРОЦЕССАМИ | 1991 |

|

RU2012035C1 |

| Устройство для сопряжения процессора с многоблочной памятью | 1987 |

|

SU1432538A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ БУФЕРНОЙ ПАМЯТЬЮ | 1990 |

|

RU2010317C1 |

| Микропроцессор | 1985 |

|

SU1330634A1 |

Изобретение относится к вычислк тельной технике и может быть использовано в ЭВМ с оперативной памятью, объем которой больше области адресации операндов в системе команд. Цель изобретения - повышение быстродействия устройства при обращении к разным блокам памяти. Устройство адресации оперативной памяти содержит три регистра, два дешифратора, четыре элемента И, элемент ИЛИ, элемент НЕ, блок канальных передатчиков. Повышение быстродействия устройства обеспечивается автоматическим перепрограммированием адресов номеров блоков памяти при чередующемся обращении к различным блокам памяти. 1 ил. с

| Патент Великобритании № 2073225, кл | |||

| G, 06 F 13/00, 198J | |||

| Устройство адресации оперативной памяти | 1981 |

|

SU999054A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-08-15—Публикация

1986-06-16—Подача