Изобретение относится к вычислительной технике и может быть использовано при построении различных устройств дискретной переработки информации на элементах с непосредственнымИ связями.

Известны устройства на элементах с непосредственными связями, состоящие из основного и вспомогательного триггеров, в которых для защиты триггеров от срабатывания из-за наводимых на их логических входах импульсных помех осуществляется стробирование управляющих схем при приеме и передаче информации.

Однако в известных устройствах напряжения помех, действующие в течение импульса выделения информации, могут накладываться на входной сигнал, что снижает помехоустойчивость устройства.

Цель изобретения - повыщение помехоустойчивости триггерного устройства и во время действия импульса выделения информации.

Для этого выход в нем инвертора, вход которого подключен к логической схеме, соединен с первым входом первой управляющей схемы «И вспомогательного триггера, второй вход которой подключен к третьему выходу блока синхронизации. Вход второй управляюо1ей схемы «И вспомогательного триггера соединен со вторым выходом блока синхронизации. Первый выход блока синхронизации подключен к одному из входов схемы «И, выход которой соединен со входом обнуления основного триггера, и к одному из входов схемы «И, выход которой соединен со входом установки основного триггера.

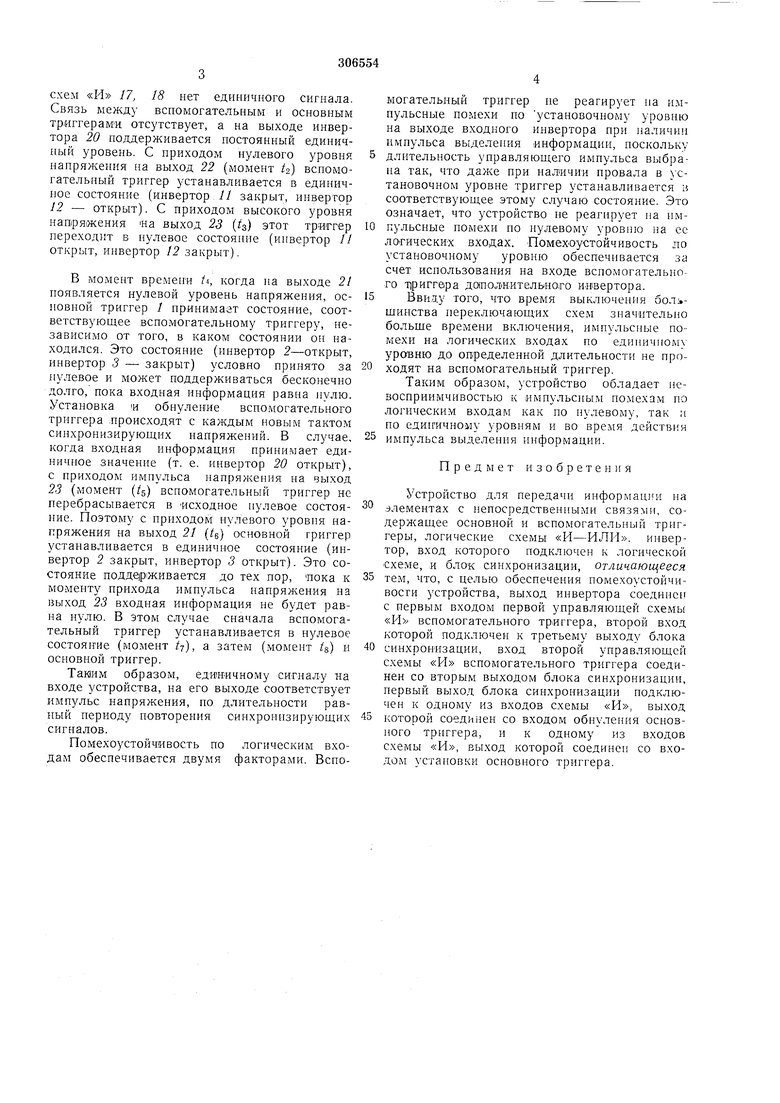

На фиг. 1 приведена структурная схема устройства; на фиг. 2 - диаграммы напряжений на выходах соответствующих узлов. Устройство для передачи информации содержит основной триггер 1, включающий в себя инверторы 2, 3, логические схемы «И 4-7 и логические схемы «ИЛИ 5, 9; вспомогательный триггер 0, включающий в себя инверторы 11, 12, логические схемы «И 13-15 и логическую схему «ИЛИ 16. Входная логическая схема состоит из схем «И 17, 18, схем «ИЛИ 19 и входного инвертора 20. Блок управляющих БУ синхронизирующих напряжений имеет для управлгшия связью между основным и вспомогательным триггерами выход для предварительной установки вспомогательного триггера выход 22 и для выделения входной информации с входного 1ннвертора выход 23.

Высокий положительный уровень условно принят за установочный (единичный), а низкий положительный уровень - за нулевой. В исходном состоянии (i) входная информация равна нулю, т. е. на выходе ни одной из

схем «И П, 18 нет единичного сигнала. Связь между вспомогательным и основным триггерами отсутствует, а на выходе инвертора 20 поддерживается постоянный единичный уровень. С приходом нулевого уровня напряжения на выход 22 (момент tz вспомогательный триггер устанавливается в единичное состояние (инвертор // закрыт, инвертор 12 - открыт). С приходом высокого уровня нап1ря1жения «а выход 23 (tz) этот триггер переходит в нулевое состояние (инвертор // открыт, инвертор /2 закрыт).

В момент времени /4, когда на выходе 21 появляется нулевой уровень напряжения, основной триггер / нринимагт состояние, соответствуюгцее вспомогательному триггеру, независимо от того, в каком состоянии он находился. Это состояние (инвертор 2-открыт, инвертор 3 - закрыт) условно принято за нулевое и может поддерживаться бесконечно долго, пока входная информация равна нулю. Установка и обнуление вспомогательного триггера .происходят с каледым новым тактом синхронизирующих напряжений. В случае, когда входная информация принимает единичное значение (т. е. инвертор 20 открыт), с приходом имиульса напряжения на выход 23 (момент (/s) вспомогательный триггер не перебрасывается в исходное нулевое состояние. Поэтому с приходом нулевого уровня напряжения на выход 21 (/б) основной григгер устанавливается в единичное состояние (инвертор 2 закрыт, инвертор 3 открыт). Это состояние подде|рживается до тех нор, пока к моменту прихода импульса напряжения на выход 23 входная информация не будет равна нулю. В этом случае сначала всномогательный триггер устанавливается в нулевое состояние (момент t), а затем (момент i) и основной триггер.

Таким образом, единичному сигналу на входе устройства, на его выходе соответствует импульс напряжения, по длительности равный периоду повторения синхронизирующих сигналов.

Помехоустойчивость но логическим входам обеспечивается двумя факторами. Всномогательный триггер не реагирует на импульсные помехи по установочному уровню на выходе входного инвертора при наличии импульса выделепия информации, поскольку

длительность управляющего импульса выбрана так, что даже при нал1ичии провала в установочном уровне триггер устанавливается и соответствующее этому случаю состояние. Это 03Ha4aet, что устройство не реагнрует на пмпульсные помехи ио нулевому уровню на ее логических входах. Помехоустойчивость ло установочному уровню обеспечивается за счет использования на входе вспомогательного т|риггбра Д01пол1нительного инвертора.

Ввиду того, что время выключения бол щинства иереключающих схем значительно больще времени включения, импульсные помехи на логических входах по единичном) уровню до определенной длительности не проходят на вспомогательный триггер.

Таким образом, устройство обладает невосприимчивостью к импульсным помехам по логическим входам как по нулевому, так м по единичному уровням и во время действия

импульса выделеиия информации.

Предмет изобретения

Устройство для передачи информации на

элементах с непосредственными связями, содерл ащее основной и вспомогательный триггеры, логические схемы «И-ИЛИ, инвертор, вход которого нодключен к логической схеме, и блок синхронизации, отличающееся

тем, что, с целью обеспечения помехоустойчивости устройства, выход инвертора соединен с первым входом первой управляющей схемы «И вспомогательного тр|Иггера, второй вход которой подключен к третьему выходу блока

синхронизации, вход второй управляющей схемы «И вспомогательного триггера соединен со вторым выходом блока синхронизации, первый выход блока синхронизации иодключен к одному из входов схемы «И, выход

которой соединен со входом обнуления основного триггера, и к одному из входов схемы «И, выход которой соединен со входом установки основного триггера.

влод1 Влод2 fuf. I

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство временной задержки | 1987 |

|

SU1431053A1 |

| Распределитель импульсов | 1980 |

|

SU919085A2 |

| Двоичный каскад на потенциальных элементах | 1970 |

|

SU514419A1 |

| Распределитель импульсов | 1980 |

|

SU869041A2 |

| ЭНЕРГОНЕЗАВИСИМАЯ ЯЧЕЙКА ПАМЯТИ | 1992 |

|

RU2030094C1 |

| Интегратор | 1988 |

|

SU1728871A1 |

| Измеритель коротких интервалов времени | 1980 |

|

SU930222A2 |

| Коммутатор для сложных цифровых вычислительных систем | 1972 |

|

SU517158A1 |

| Селектор импульсов по длительности | 1984 |

|

SU1226631A1 |

| Д-ТРИГГЕР С ЗАДЕРЖКОЙ | 1973 |

|

SU396832A1 |

Авторы

Даты

1971-01-01—Публикация