Изобретение относится к области вычислительной техники и автоматики.

Известны аналого-щифравые преобразователи (АЦП), содержащие дифференциальный усилитель, блок пороговых элементов, регистр состояний пороговых устройств, сумматор, преобразователь код-аналог, блок управления. В таких преобразователях величина ступени компенсирующего напряжения пропорциональна ириращению преобразуемого напряжения за время такта. Выбор значений порогов срабатывания пороговых элементов и их количество определяет как допустимую скорость f/.x изменения, так и динамическую погрешность.

Все известные АЦП накладывают ограничения на скорость изменения входного сигнала, которые вызваны тем. что компенсация вводится с учетом величины разбала-нса в момент опроса. Увеличение скорости Ux приводит к существенному увеличению величины разбалаяса в момент опроса. Поэтому для уменьщения динамической погрешностн необходимо значительно увеличить число .пороговых элементов.

Целью изобретения является уменьшение динаМИческой погрещ ости (увеличение динамической точности) следящих АЦП путем ведения процесса компенсации с учетом скорости изменения входной величины без увеличения числа пороговых элементов и при сохранении такта преобразования.

Эта задача решается с помощью двойного опроса состояний пороговых элементов с

заданным интервалом времени, выделения кода дифференциала входного сигнала и соответствующих логических операций, приводящих к тому, что величина ступеней компенсирующего напр:яжения выдается с таки.м

расчетом, чтобы величина разбаланса в момент опроса была минимально возможной и не накапливалась за время такта. KjpOMe того, перед выдачей результата преобразования осуществляется коррекция динамической погрещности.

Предложенное устройство отличается от известных тем, что содержит дополнительный, регистр, вычитатель кодов и клапаны, причем входы основного и дополнительного регистров

соединены с выходом дешифратора через клапаны, а выходы - подключены ко входу вычитателя, выходы которого соединены со Бхода ми сумматора. Другие входы сумматора подключены к выходу основного регистра.

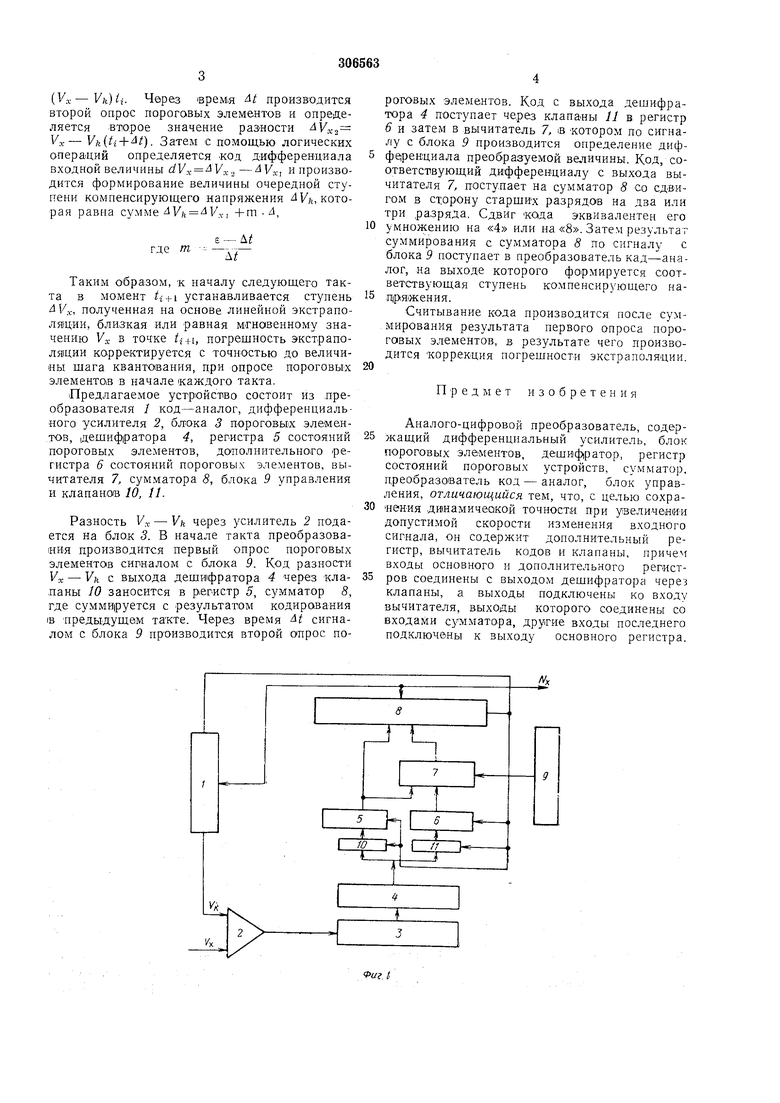

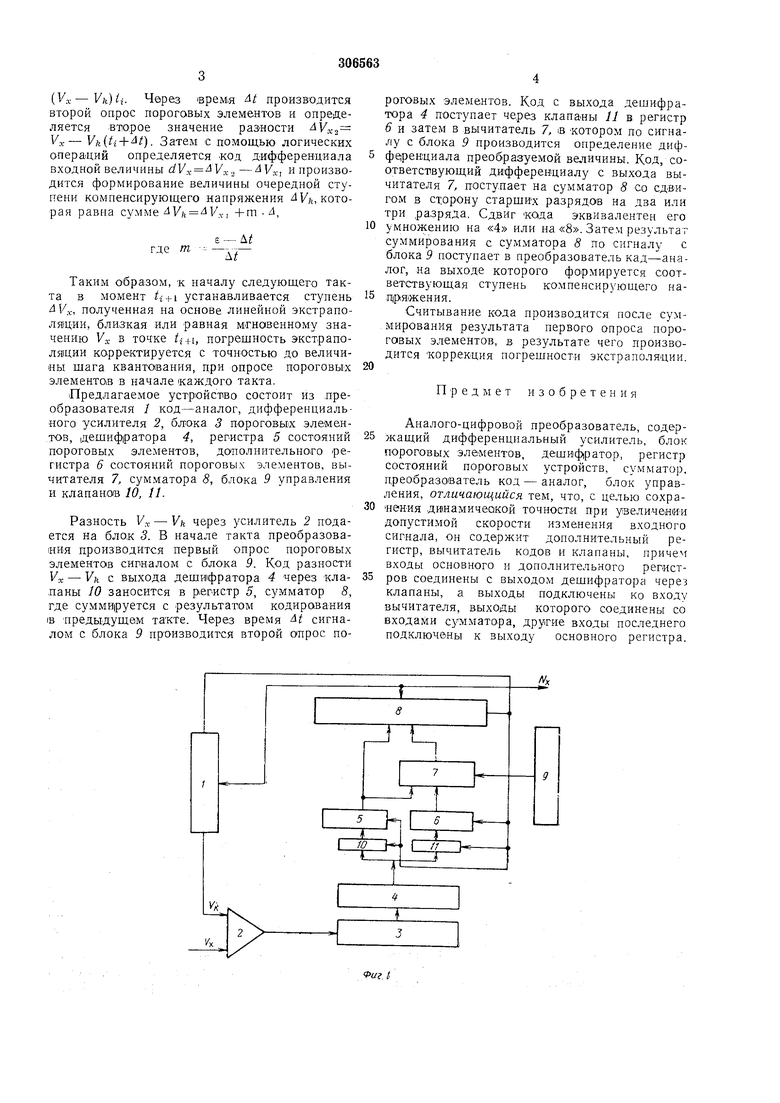

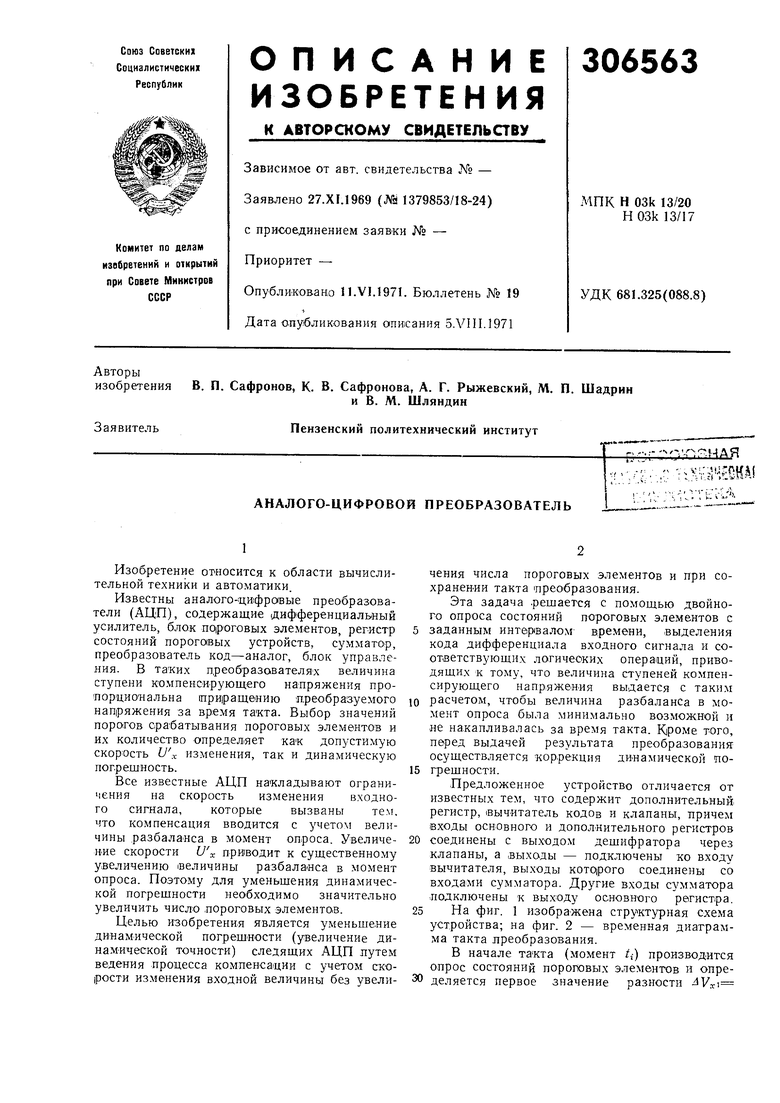

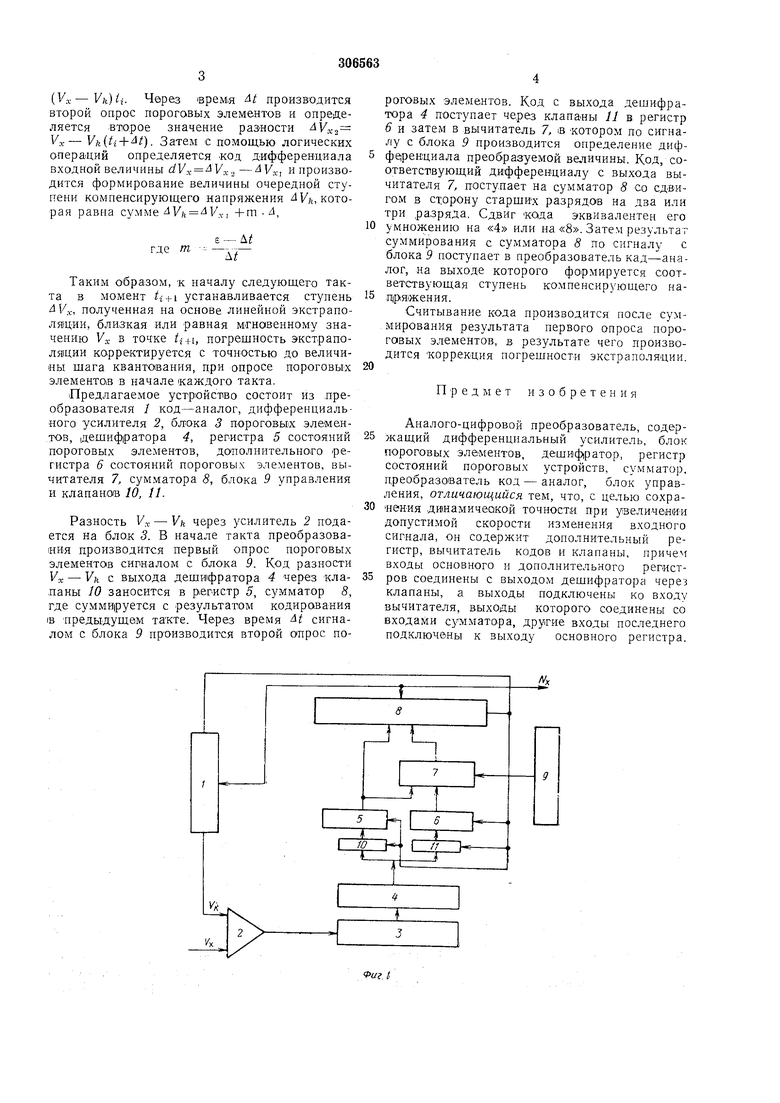

На фиг. 1 изображена структурная схема устройства; на фиг. 2 - временная диаграмма такта преобразования.

(V.T-Vk)ti. Через щремя i производится второй опрос пороговых элементов и определяется второе значение разиости ЛУх - Vx- Vh{ti+(). Затем с помощью логических операций определяется «од дифференциала входной величины dVx Vx., и производится формирование величины очередной ступени компенсирующего напряжения 4у, которая равна сумме 4 Vft 4Кт1 +т-4,

где ffi Г

Таким образом, к началу следующего такта в момент ti+i устанавливается ступень ЛУх, полученная на основе линейной экстраполя ции, близкая или равная мгновенному значению Vx в точке ti+i, погрешность экстрапоЛЯ1ЦИИ корректируется с точностью до величины шага квантования, при опросе пороговых элементов в начале каждого такта.

Предлагаемое устройство состоит из .преобразователя / код-аналог, дифференциального усилителя 2, блока 3 пороговых элементов, дешифратора 4, регистра 5 состо-яний пороговых элементов, дополнительного регистра 6 состояний пороговых элементов, вычитателя 7, сумматора 8, блока 9 управления и клапанов 10, 11.

Разность Vx - Vfe через усилитель 2 подается на блок 3. В начале такта преобразования производится первый опрос пороговых элементов сигналом с блока 9. Код разности УХ - Ffe с выхода деши|фратора 4 через клапаны 10 заносится в регистр 5, сумматор S, где суммируется с результатом кодирования IB предыдущем такте. Через время t сигналом с блока 9 производится второй опрос пороговых элементов. Код с выхода дешифратора 4 поступает через клапаны 11 в регистр 6 и затем в вычитатель 7, в котором по сигналу с блока 9 производится определение диффе ревциала преобразуемой величины. Код, соответствующий дифференциалу с выхода вычитателя 7, поступает на сумматор 8 со сдвигом в сторону старщих разрядов на два или три разряда. Сдвиг кода эквивалентен его умножению на «4 или на «8. Затем результат суммирования с сумматора 8 по сигналу с блока 9 поступает в преобразователь кад-аналог, на выходе которого формируется соответствующая ступень компенсирующего на.цряжения.

Считывание кода производится после суммирования результата первого опроса пороговых элементов, в результате чего производится коррекция погрешности экстраполяции.

Предмет изобретения

Аналого-цифровой преобразователь, содержащий дифференциальный усилитель, блок пороговых элементов, дешифратор, регистр состояний пороговых устройств, сумматор, преобразователь код-аналог, блок управления, отличающийся тем, что, с целью сохранения ди намичеакой точности при увеличении допустимой скорости изменения входного сигнала, он содержит дополнительный регистр, вычитатель кодов и клапаны, причем входы основного и дополнительного регистров соединены с выходом дешифратора через клапаны, а выходы подключены ко входу вычитателя, выходы которого соединены со входами сумматора, другие входы последнего подключены к выходу основного регистра.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство стабилизации динамического диапазона сигнала | 1986 |

|

SU1480096A1 |

| Аналого-цифровой преобразователь | 1976 |

|

SU580640A1 |

| Аналого-цифровой преобразователь | 1973 |

|

SU486470A1 |

| Адаптивный аналого-цифровой преобразователь | 1986 |

|

SU1312733A2 |

| Адаптивный цифровой корректор | 1987 |

|

SU1506558A2 |

| Фотоэлектрический анализатор количества и размеров частиц | 1987 |

|

SU1518727A1 |

| Аналого-цифровой преобразователь | 1980 |

|

SU884127A1 |

| Устройство цифрового преобразования видеосигнала | 1989 |

|

SU1660210A1 |

| Устройство преобразования информации | 1989 |

|

SU1676099A1 |

| Устройство для контроля экспоненциальных процессов | 1986 |

|

SU1310781A1 |

Авторы

Даты

1971-01-01—Публикация