первый дополнительный элемент И-ИЛИ-И соединен с третьим входом элемента ИЛИ и с входом второго доиолнительного регистра, выход которого через второй дополнительный элемент И-ИЛИ-И соединен с пятым входом элемента ИЛИ.

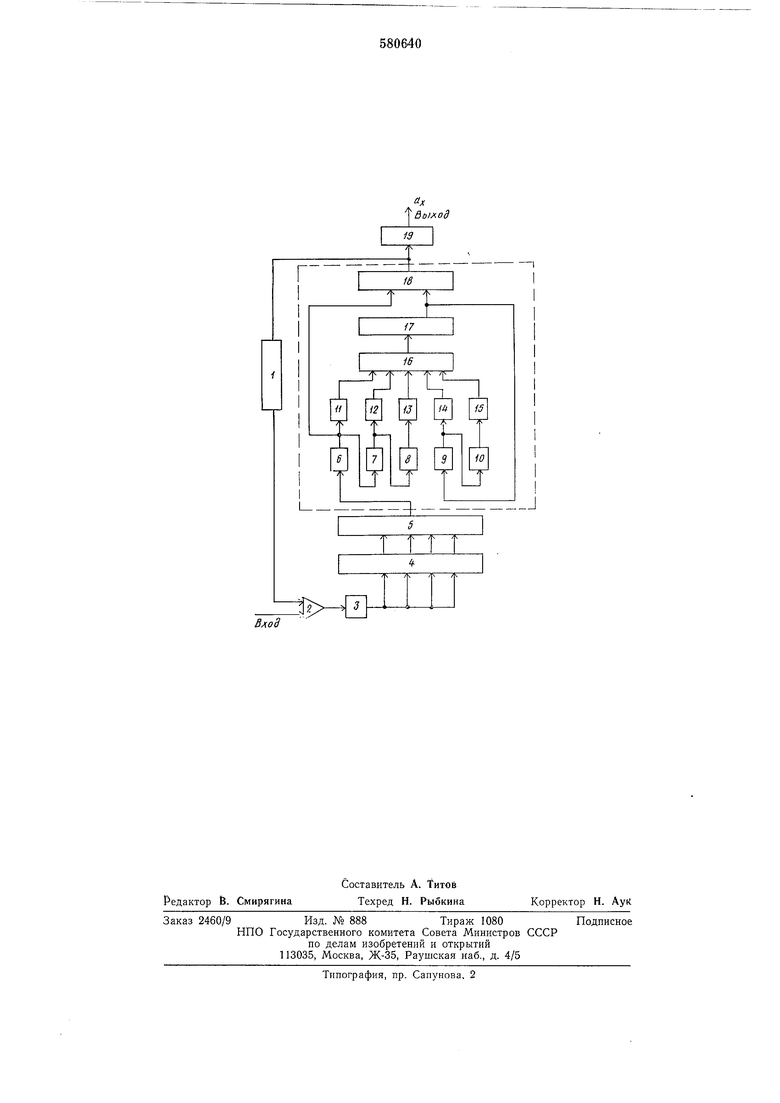

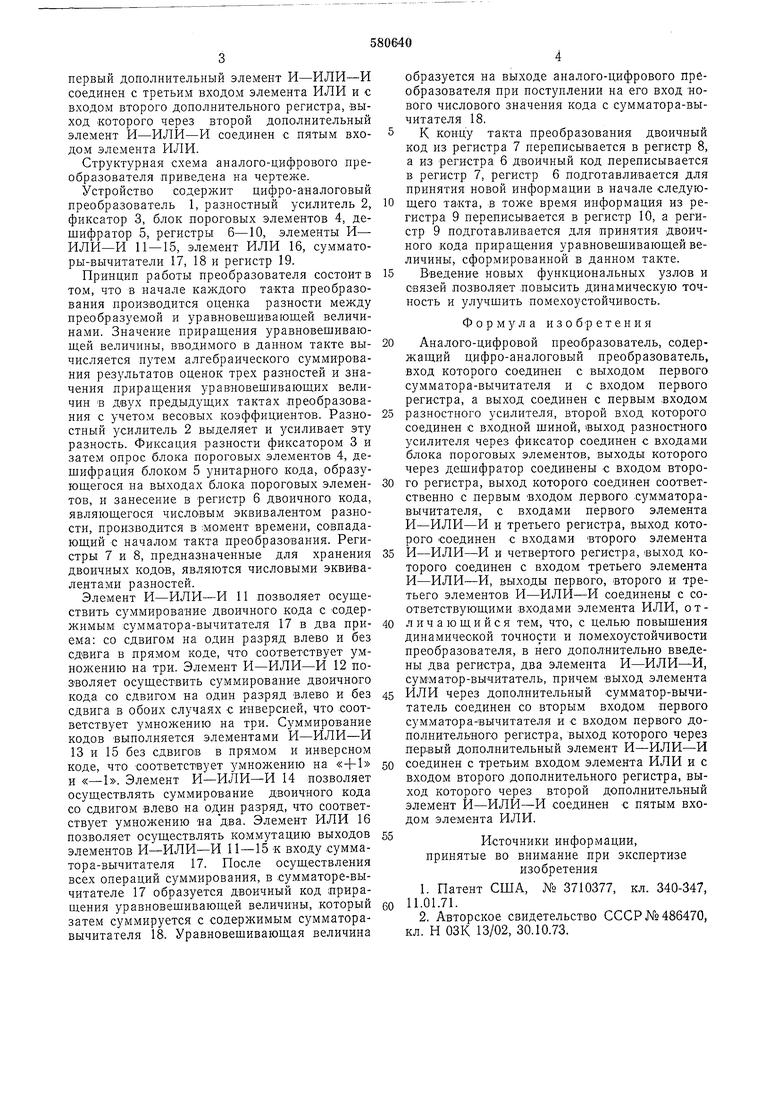

Структурная схема аналого-цифрового преобразователя приведена на чертеже.

Устройство содержит цифро-аналоговый преобразователь 1, разностный усилитель 2, фиксатор 3, блок пороговых элементов 4, дешифратор 5, регистры 6-10, элементы И- ИЛИ-И 11 - 15, элемент ИЛИ 16, сумматоры-вычитатели 17, 18 и регистр 19.

Иринцип работы преобразователя состоит в том, что в начале каждого такта преобразования производится оценка разности между преобразуемой и уравновешивающей величинами. Значение приращения уравновешивающей величины, вводимого в данном такте вычисляется путем алгебраического суммирования результатов оценок трех разностей и значения приращения уравновешиваюших величин в двух предыдущих тактах преобразования с учетом весовых коэффициентов. Разностный усилитель 2 выделяет и усиливает эту разность. Фиксация разности фиксатором 3 и затем опрос блока пороговых элементов 4, дешифрация блоком 5 унитарного кода, образующегося на выходах блока пороговых элементов, и занесение в регистр 6 двоичного кода, являющегося числовым эквивалентом разности, производится в ;момент времени, совпадающий с началом такта преобразования. Регистры 7 и 8, предназначенные для хранения двоичных кодов, являются числовыми эквивалентами разностей.

Элемент И-ИЛИ-И 11 цозволяет осуществить суммирование двоичного кода с содержимым сумматора-вычитателя 17 в два приема: со сдвигом на один разряд влево и без сдвига в прямом коде, что соответствует умножению на три. Элемент И-ИЛИ-И 12 позволяет осуществить суммирование двоичного кода со сдвигом на один разряд влево и без сдвига в обоих случаях с инверсией, что .соответствует умножению на три. Суммирование кодов выполняется элементами И-ИЛИ-И 13 и 15 без сдвиго В в прямом и инверсном коде, что соответствует умножению на «-fl и «-1. Элемент И-ИЛИ-И 14 позволяет осуществлять суммирование двоичного кода со сдвигом влево на один разряд, что соответствует умножению на два. Элемент ИЛИ 16 позволяет осуществлять коммутацию выходов элементов И-ИЛИ-И 11-15 к входу сумматора-вычитателя 17. Иосле осуществления всех операций суммирования, в сумматоре-вычитателе 17 образуется двоичный код приращения уравновещивающей величины, который затем суммируется с содержимым сумматоравычитателя 18. Уравновещивающая величина

образуется на выходе аналого-цифрового преобразователя при поступлении на его вход нового числового значения кода с сумматора-вычитателя 18.

К концу такта преобразования двоичный код из регистра 7 переписывается в регистр 8, а из регистра 6 двоичный код переписывается в регистр 7, регистр 6 подготавливается для принятия новой информации в начале следующего такта, в тоже время информация из регистра 9 переписывается в регистр 10, а регистр 9 подготавливается для принятия двоичного кода приращения уравновешивающей величины, сформированной в данном такте.

Введение новых функциональных узлов и связей позволяет повысить динамическую точность и улучщить помехоустойчивость.

Формула изобретения

Аналого-цифровой преобразователь, содержащий цифро-аналоговый иреобразователь, вход которого соединен с выходом первого сумматора-вычитателя и с входом первого регистра, а выход соединен с первым входом разностного усилителя, второй вход которого соединен с входной шиной, выход разностного усилителя через фиксатор соединен с входами блока пороговых элементов, выходы которого через дещифратор соединены с входом второго регистра, выход которого соединен соответственно с первым входом первого сумматоравычитателя, с входами первого элемента И-ИЛИ-И и третьего регистра, выход которого соединен с входами второго элемента И-ИЛИ-И и четвертого регистра, выход которого соединен с входом третьего элемента И-ИЛИ-И, выходы первого, второго и третьего элементов И-ИЛИ-И соединены с соответствующими входами элемента ИЛИ, отличающийся тем, что, с целью повышения динамической точности и помехоустойчивости преобразователя, в него дополнительно введены два регистра, два элемента И-ИЛИ-И, сумматор-вычитатель, причем выход элемента ИЛИ через дополнительный сумматор-вычитатель соединен со вторым входом первого сумматора-вычитателя и с входом первого дополнительного регистра, выход которого через первый дополнительный элемент И-ИЛИ-И соединен с третьим входом элемента ИЛИ и с входом второго дополнительного регистра, выход которого через второй дополнительный элемент И-ИЛИ-И соединен с пятым входом элемента ИЛИ.

Источники информации,

принятые во внимание при экспертизе

изобретения

1.Патент США, № 3710377, кл. 340-347, 11.01.71.

2.Авторское свидетельство СССР №486470, кл. Н ОЗК 13/02, 30.10.73.

Вмд

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь | 1973 |

|

SU486470A1 |

| Аналого-цифровой инкрементный умножитель | 1982 |

|

SU1057971A1 |

| Инкрементный умножитель аналоговых сигналов | 1983 |

|

SU1113820A1 |

| Цифровой гармонический анализатор | 1979 |

|

SU873148A1 |

| Цифровой функциональный преобразователь | 1977 |

|

SU684551A1 |

| Устройство масштабирования цифрового дифференциального анализатора | 1983 |

|

SU1156069A1 |

| ФАЗОМЕТР С ГЕТЕРОДИННЫМ ПРЕОБРАЗОВАНИЕМ ЧАСТОТЫ | 2013 |

|

RU2551837C2 |

| Устройство для вычисления полиномиальной функции от аналогового аргумента | 1990 |

|

SU1737444A1 |

| Устройство для вычисления показателя экспоненциальной функции | 1985 |

|

SU1270770A1 |

| Функциональный преобразователь | 1977 |

|

SU693379A2 |

Авторы

Даты

1977-11-15—Публикация

1976-01-23—Подача