Данное изобретение относится к области автоматики.

Известны аналого-цифровые устройства для вычисления интегралов Стильтьеса, содержащие соединенные между собой преобразователь напряжения в частоту, генератор эталонной частоты, двухтактный генератор, времяимпульсные преобразователи, ключи, триггеры, логические элементы, схему синхронизации и реверсивный счетчик.

Однако эти устройства имеют недостаточную точность и помехоустойчивость.

Предлагаемое устройство отличается тем, Что в нем выход преобразователя интегрирующего напряжения в частоту и выход генератора эталонной частоты подключены через управляемые сигналами с выходов логических элементов «И ключи, логические элементы «ИЛИ и схему синхронизации ко входам сложения и вычитания реверсивного счетчика. Выходы двух время-импульсных преобразователей интегрирующей функции, присоединенных запускающими входами к выходам двухтактного генератора, подключены через «чогический элемент «ИЛИ к единичному входу одного из триггеров, к элементу задержки импульсов и к рабочему входу ключа, управляющий .вход которого соединен с единичным выходом упомянутого триггера. Выходы ключа и элемента задержки импульсов соединены соответственно с единичным и нулевым входами второго триггера и через логический элемент неравнозначности подключены к счетному входу третьего триггера, единичный выход которого соединен со входами логических элементов «И, подключенных вторыми входами к нулевому и единичному выходам второго триггера. Это позволило повысить точность и помехоустойчивость устройства.

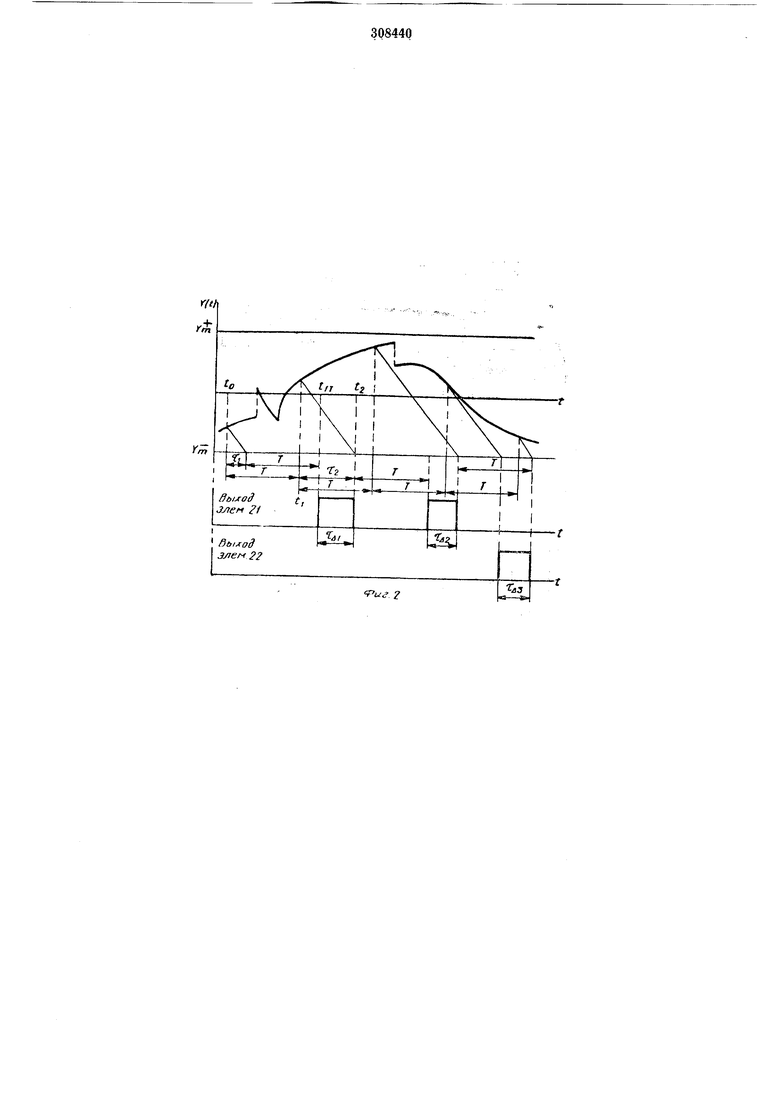

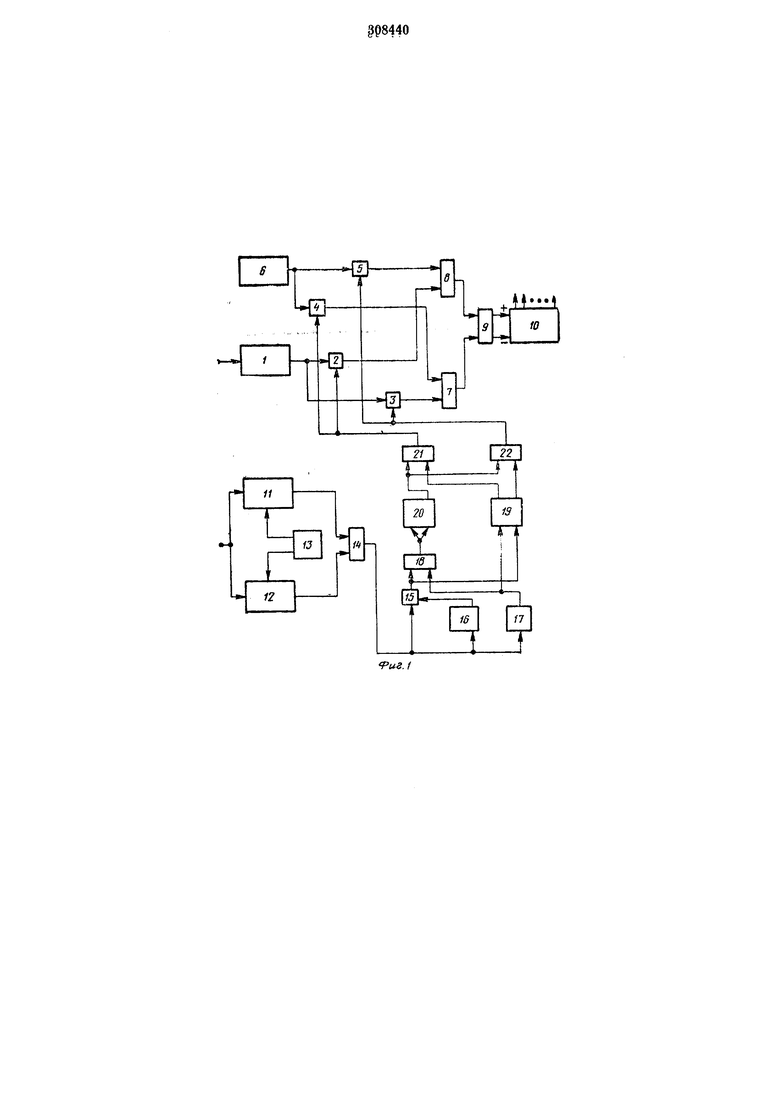

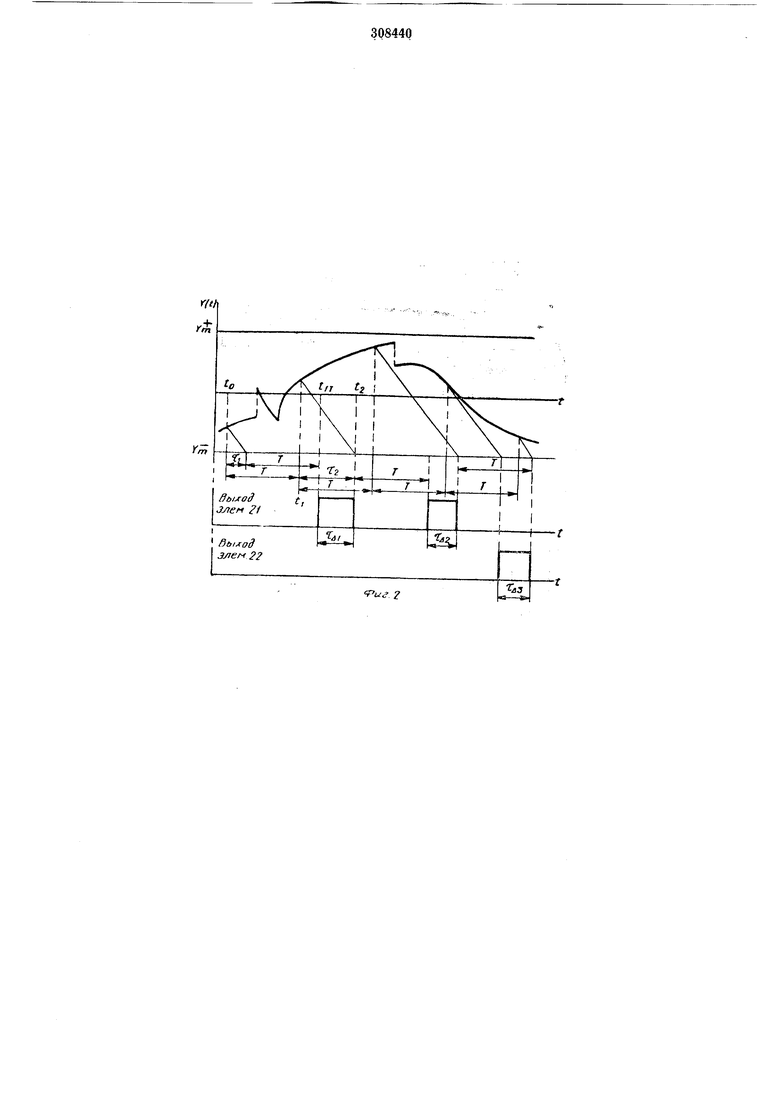

На фиг. 1 приведена блок-схема устройства, на фиг. 2 - временная диаграмма, поясняющая его работу.

Напряжение (t), представляющее интегрируемую функцию, подано на вход преобразователя 1 напряжения в частоту (фиг. 1), имеющего характеристику

/ /о+ах,

где /о и а - константы, а х изменяется в пределах от х до х + .

Выход преобразователя / соединен с рабочими входами нормально закрытых ключей 2 и 3, пропускающих импульсы на выход только

при наличии на их управляющих входах высокого потенциала. С рабочими входами идентичных ключей 4 и 5 соединен выход генератора эталонной частоты fo-6. Выходы ключей 2 и 5 соединены со входами логического элемента «ИЛИ 8. Выходы элементов 8 и 7 сои 5, управляющие входы которых соединены с выходом элемента «И 22.

Если , то в течение тЛ на суммирующий вход « + реверсивного счетчика импульсов 10 с выхода преобразователя / через ключ 2, элемент «ИЛИ 5 и схему синхронизации 9 поступит число импульсов

N(fo+axi),

где Хг - среднее значение x(t) в течение а на его вычитающий вход «- с выхода генератора эталонной частоты через открытый ключ 4, элемент «ИЛИ 7 и схему синхронизации 9 поступит число импульсов

N- /отА;.

Таким образом, приращение содержимого счетчика 10 за время Т (фактически счет ведется в течение тД;, а остальное время Т-тА может быть использовано, например, для считывания содержимого счетчика 10) составит

Ni ,(8)

где с аЬ.

Поскольку в (8) значение Xi является средним значением x(t) на отрезке времени тА, влияние помехи, присутствующей в сигнале x(t), на результат вычисления существенно меньше, чем при вычислении непосредственно по точной формуле.

Если , то, рассуждая аналогично предыдущему с учетом того, что согласно вышеописанному Б этом случае под высоким потенциалом в течение тД, Ь|Агг/| находится выход элемента «И 22, т. е. открыты ключи 3 и 5, получаем

,./о; {fo + axi}r,

откуда

I Ail/1 ,

T. e. и в 9TOM случае имеем выражение, аналогичное (8).

После п циклов Т результат N, зафиксированный счетчиком 10 (при нулевых начальных условиях, т. е. при , ), составит

.Ni cI,(9)

11

Нетрудно видеть, что при достаточно малом Т - таком, чтобы среднее значение x(t) в течение Т мало отличалось от его среднего значения на интервале тА,-, что практически всегда возможно, и при выполнении естественного условия (5) формула (9) с точностью до масштабного коэффициента представляет собой интегральную сумму Стильтьеса.

Следует отметить, что первое условие ири длительной работе устройства должно выполняться лишь статистически, т. к. отклопения

значений Ni, обусловленные его невыполне нием, вносят незначительные, статистически независимые взаимно компенсирующиеся вви ду непостоянства знака отклонения результата от истинного, а условие (5) является несколько видоизмененным условием существования интеграла Стильтьеса.

Считывание результата Л с разрядовых выходов счетчика 10 может быть осуществлено

любым из известных способов.

При одновременном вычислении нескольких интегралов Стильтьеса с одинаковой интегрирующей функцией можно использовать одну общую часть схемы фиг. 1. формирующую ин тервалы тД; (элементы //-22, а в случае применения идентичных преобразователей напряжения в частоту - также один общий генератор эталонной частоты 6 и общие ключи 4,5. Генератор 6 в случае идентичности применяе° мых преобразователей / может быть общим и при различных интегрирующих функциях. Ясно также, что при одинаковых интегрируемых функциях общими могут быть элементы

/ и 5. 5

Предмет изобретения

Аналого-цифровое устройство для вычисления интегралов Стильтьеса, содержащее соединенные между собой преобразователь напряжения в частоту, генератор эталонной частоты, двухтактный генератор, время-импульсные преобразователи, ключи, триггеры, логические элементы, схему синхронизации и реверсивный счетчик, отличающееся тем, что, с целью повьтн.ения точности и помехоустойчивости, в нем выход преобразователя интегрирующего напряжения в частоту и выход генератора эталонной частоты подключены через управляемые сигналами с выходов логических .т-нтов «И ключи, логические элементы «ИЛИ и схему синхронизации ко входам сложения и вычитания реверсивного счетчика;

выходы двух время-импульсных преобразователей интегрирующей функции, присоединенных запускающими входами к выходам двухтактного генератора, подключены через логический элемент «ИЛИ к единичному входу одного из триггеров, к элементу задержки импульсов и к рабочему входу ключа, управляю щий вход которого соединен с единичным выходом упомянутого триггера; выходы ключа и элемента задержки импульсов соединены соответственно с единичным и нулевым входами второго триггера и через логический элемент неравнозначности подключены к счетному входу третьего триггера, единичный выход которого соединен со входами логических элементов

0 «И, подключенных вторыми входами к нулевому и единичному выходам второго триггера. ным интервалу времени между очередными запусками преобразователей 11 и 12. Благодаря этому первый импульс на выходе элемента задержки 17 появляется в момент Лг /о+т, + 7.(6) Сравнивая (3) и (6) с учетом (2) и (4), нетрудно видеть, что импульс на выходе преобразователя 12 появится позлее, т. е. . Это ясно также из следующего: если const, то ИМПУЛЬС с выхода преобразователя 11, задержанный на время Т. появился бы на выходе элемента задержки 17 одновременно с ИМПУЛЬСОМ на выхо.е преобразователя 12, запущепного на время Т позже,чем преобразовате ль //. Поскольку же согласно условию у(л+Т) /(#«), имеет и задержанный на Т выходной импульс преобразователя 11 опережает выходной импульс преобразователя /2 на величину тм т,(о+Г)-г/(/о)1&. (7) Первый импульс с в лхода элемента задержки 17 поступает на нулевой вход триггера 19, устанавливая п соответствующее состояние (высокий потенциал на левой выходной шине), и через логиче кий элемент неравнозначности 18 - на счетный вход триггера 20, устанавливая его в единичное (высокий потентиял на правой выхотной шине) (так как исходным является нулевое). ПРИ этом высокий потенциал оказывается потячным на оба вхппа ПОТРНЦИЯЛЬТ-ЮГО элемента «И 21, т. е. на его выходе устанавливается с этого момента высокий потенциал. Спустя время Тд1 второй импульс, поступаюц,ий непосредственно с выхода преобразователя 12, ПРОХОДИТ через логический элемент «ИЛИ М и открытый теперь ключ 15 ня опипичцый вход триггера 19, устанавливая его в соответствующее состояние, а также - через логический элемент неравнозначности 18-на счетный вход триггера 20, возвращая его в нулевое исходное состояние. При этом высокии потенциал снимается с левых входов элементов «И 21 и 22, т. е. в этом состоянии их выходы, как и в исходном, находятся под низким потенциалом. Этот же импульс с выхода преобразователя 12 поступает также на вход элемента задержки импульсов /7. Таким образом, в течение времени , проприрашениюпорционального согласно (7) функции y(t) за время от о ДО io+T, выход элемента «И 21 находится под высоким потенциалом. Нетрудно видеть (фиг. 2), что в дальнейшем импульс с выхода преобразователя 12 (фиг. 1), поступивший на вход элемента задержки 17, играет роль первого импульса в предыдущем рассмотрении, а следующий импульс с выхода преобразователя 11, вновь запущенного спус12,- роль второго импульса, т. е. следующий интервал т. , в течение которого будет поддерживаться высокий потенциал на выходе элемента «РЪ 21, окажется пропорциональным приращению y(tu+2T -y( и т. д., т. е. х,. (t,)l,(t,+ (i-) (подразумевается, что ). Рассуждая аналогично предыдущему, нетрудно показать, что в случае, если , т. е. //((с), первым появляется импульс с выхода преобразователя 12, и, спустя время т,, -импульс с выхода преобразователя 11, задержанный элементом задержки 17 на время Г. В этом случае в течение т, триггер 20, как и в предыдущем случае, находится в единично состоянии, но теперь в единичном состоянии находится и тпиггеп 19. т. f. при гСгп-t-rT) :/Г д- -f-ПЛ под высоким потенциалом в течение времени т Д, Ъ t/{t,+iT -:;(f,+ (,t/ находится выход логического элемента «И 22, а HP я.пементя «И 21. Если ., импупьсы на входы логического элемента неравнозначности 18 поступают одновременно, при этом импульс на его выходе не возникает, т. е. триггер 20 остается в нулевом состоянии (тА,. - 0), а состояние триггера 19 при не роли, т. к. оно станавлиряется в ня1тя,ле каждого интервала тА в соотп тствпи со знячo т А.-г/ (со ластю приняТ1; м обозначениям: «О при А. и «1 при ). Нетрудно убедиться, что при переходе из одного рржиля в (от // 0 к //,, ;0 и тгроборот) описанный алгоритм работы схе.мы обеспечивает сохранение пропорциональности длительности тА.. приращению v(f) на интервале .)7, tri + iT с соблюдением знака (знак индицируется состоянием триггера 19 течение т А,-; при этом, если А7., высокий потенпиал поддерживается в течение тА, на выходе элемента «И 21, а если А, - на выхолной щине элемента «И 22). Рассмотрим теперь работу верхней части (элементы 1-10 фиг. 1. На входы ключей 4 и 5 с выхода генератора эталонной частоты 6 непрерывно поступают ИМПУЛЬСЫ с частотой fn. Напряжение , представляющее интегрируемую сЬункцию, подано на вход линейного преобразователя / напряжения в частоту, так что с его выхода на рабочие входы ключей 2 и 3 непрерывно поступают импульсы с частотой f :fn-rax(t. Из описания работы нижней части схемы ясно, что ключи 2-5 нормально закрыты, причем в случае на время тА, открываются ключи 2 и 4, управляющие входы которых соединены с выходом элемента «И 21, а цри

иг. 2

| название | год | авторы | номер документа |

|---|---|---|---|

| УСИЛИТЕЛЬ ВРЕМЯИМПУЛЬСНЫХ СИГНАЛОВ | 1971 |

|

SU312375A1 |

| Способ интегрирующего аналого-цифрового преобразования и устройство для его осуществления | 1985 |

|

SU1381709A1 |

| УСТРОЙСТВО ПОИСКА И СОПРОВОЖДЕНИЯ СИГНАЛА СИНХРОНИЗАЦИИ В СПУТНИКОВЫХ СИСТЕМАХ СВЯЗИ ПО ПРИЕМУ | 1995 |

|

RU2093964C1 |

| Устройство для измерения вихревого компонента скорости потока | 1984 |

|

SU1265619A1 |

| Аналого-цифровой преобразователь | 1974 |

|

SU1005305A1 |

| Устройство для измерения вихревого компонента скорости потока | 1982 |

|

SU1016746A1 |

| Преобразователь активной мощностиВ КОличЕСТВО иМпульСОВ | 1979 |

|

SU845109A1 |

| Преобразователь перемещения в код | 1974 |

|

SU560249A1 |

| Устройство для вычисления показателя экспоненциальной функции | 1986 |

|

SU1335990A1 |

| Устройство синхронизации | 1983 |

|

SU1095435A1 |

Даты

1971-01-01—Публикация