Изобретение относится к области запоми-наюпдих устроЙ€1 5.

Известны буферные заноминающне устройства, содержащие .магазин ко.манд, регистры, счетчики, схе.мы сравнеиия, вентили, с.хемы ИЛИ, лвпии задержки, триггеры, шины передачл пиформацми. Недостатком известиы.х устройств является большой объе.м оборудования для обработки запросов и и.х посылки в оиеративную намять, недостаточная гибкость в разрешении конфликтов ,из-за отсутствия динамического .приоритета, что приводит к иростоям вычислителей системы.

Цель изобретения - увеличить быстродействие системы, уменьшить оборудование, обеспечпвающее непрерывность обработки информацин в вычислителях системы и увеличить гибкость системы за счет использоваиия динамического приоритета.

Достигается это тем, что предлагаемое буферное заномииающее устройство содержит магазин операндов, схемы сравнения содержимого регистров .магазина ко.манд с содерЖИ.мым регистров готовности блоков оперативной памяти, первые триггеры запоминания уровня, веитили выдачи старшей зоны адреса команды из регистров магазина команд, схему анализа признака адреса, схемы сравнения содержимого регистров магазина операндов с содержимым регистра готовности блоков операгпвпэи памятп, вторые триггеры заиомппапия у|)овпи. вептпл п вы.хачп сгарши.ч разрядов адреса операнда, регистры дина.мического и .максимального приоритета, счетчик адреса магазпногз, веитжти заппси содержимого счетчпка адреса в регистры магазиил ко.мапд, схе.мы сравпения содоржшгого счогчика адреса с содержпмы.м poriiCTjiois мгппзиаа ко.мапд, веитп.чп записи co.ioji/KnMoro ппформациониого регпсг|)а Б periicrp магазина команд, веитпл; записи содержимого счетчп;ка адреса магазинов в регистр, опера 1дов, с.че.мь сравнепия содержимого счетчика адреса с содержимы.м магаз 1 а операндов, ве ггили содержп. информац юииого регпсгра в регист) магаз)1а операндов, тр птеры запрета магазшю) команд и опера; дов, npnMCN первые вход;. схем с-равпе1 1:ия содерж1 мого рег1 строБ млгазина комапд , через .с.хемы ПЛИ к регистра готов ости блоков операТ В 10Й , а вход схем сравиеП Я - к рег страм магаз;п а ко. п N araзиНа 0 ерапдов соответстзе 1 ю, выходы указа иных схем сраБие 1 1,ч 1одсоедпнепы ко входам первых и вторых триггеров запо. уровня, выходы которых связаны с первымн входами вепылей выдачи старшнх разрядов адреса команд и оиерапдов, а вторые

команд и магазина операндов; первый вход схемы анализа п-ризнака адреса соединен с /(-ым регистром магазина команд, а ее второй вход-с S-ым регистром магазина операндов, а ее выход соединен со входом вентиля выдачи содержимого регистра максимального приоритета и со входом вентиля выдачи содержимого регистра динамического приоритета; выход счетчика адреса магазинов через вентиль соединен с иервы.ми входами вентилей записи содержимого счетчика адреса в регистры магазина команд, вторые входы вентилей связаны с выходами иервых триггеров заномииания уровня, выходы указанных вентилей подключены к регистрам магазина команд; схемы сравнения содержимого счетчика адреса связаны со счетчиком адреса и с регистрами магазина команд, выходы указанных схем сравнения иодключены к первым входам вентилей записи содержимого информационного регистра в регистр магазина команд, вторые входы вентилей связаны с ,информационНЫчМ регисгром; выход счетчика адреса магазинов через вентиль соединен с иервыми входами вентилей записи содержимого счетчика адреса в регистры магазина оиераидов, Вторые входы вентилей связаны С выходами вторых триггеров запоминания уровня, выходы указанных вентилей-с регистрами магазииа операндов, схемы сравнения содержимого счетчика адреса связаны со счетчиком адреса и с регистрами магазииа оиераиДОВ, выходы указанных схем сравнення иодключены к первым входам вентилей записи содержимого информационного регистра в регистр .магазина операндов, вторые входы вентилей связаны с информацио гным регисгром.

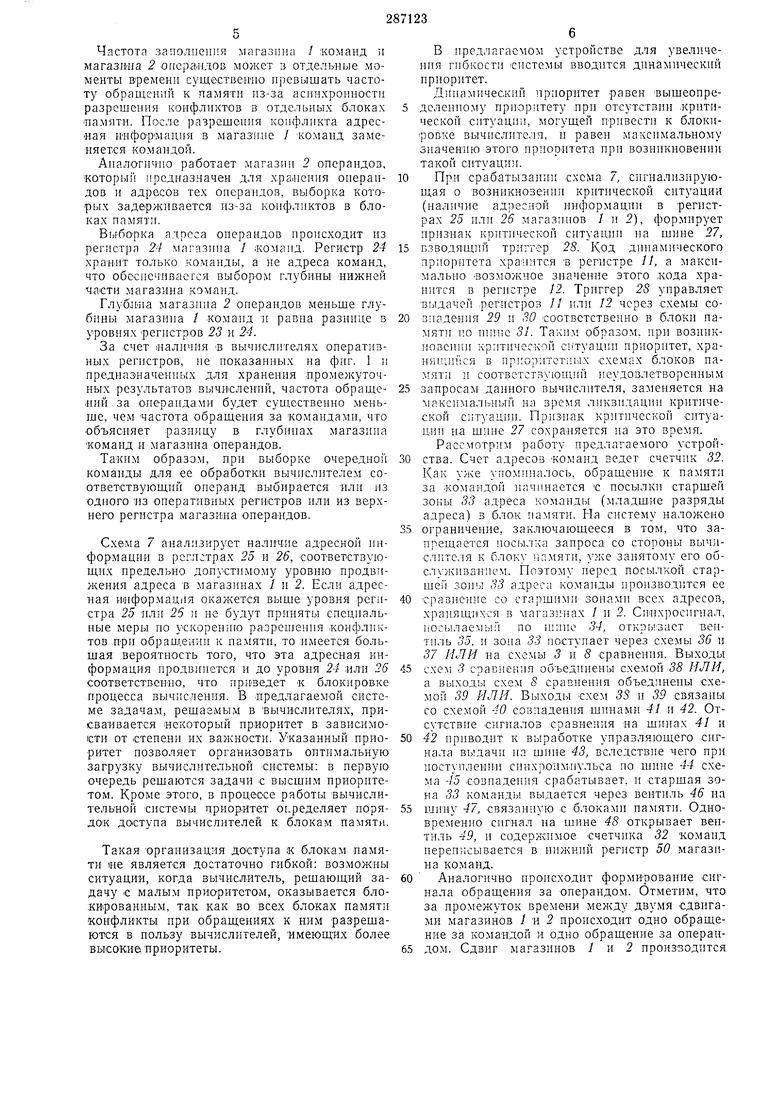

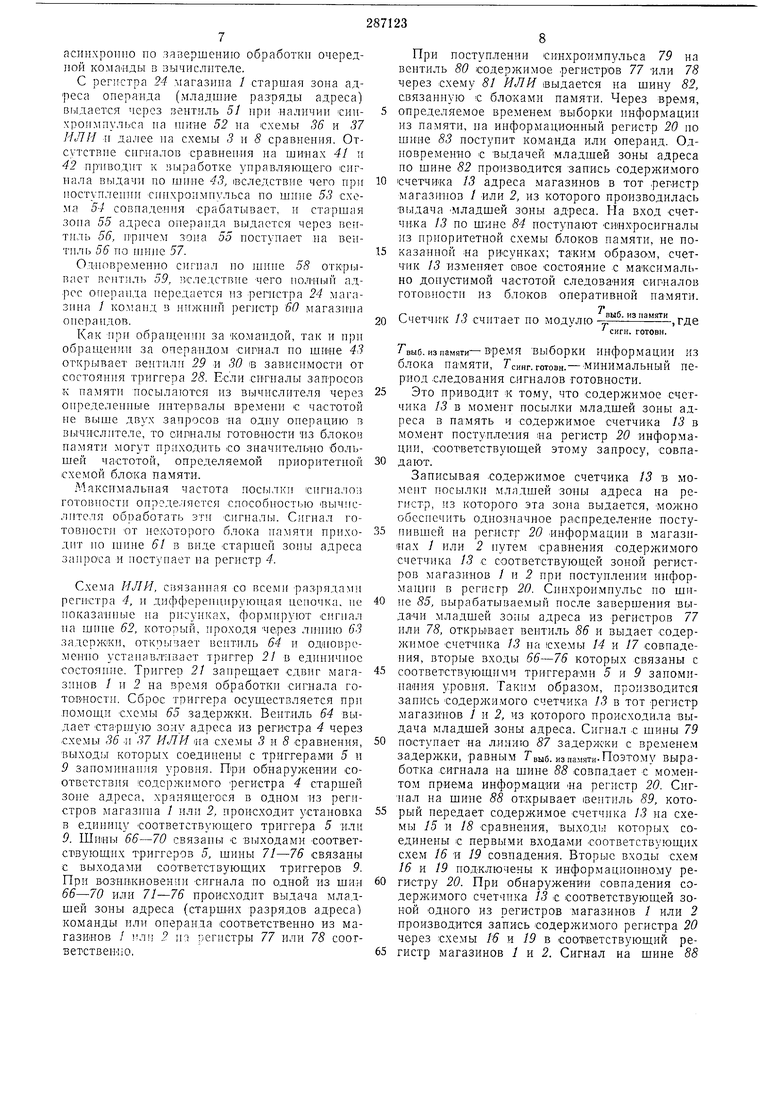

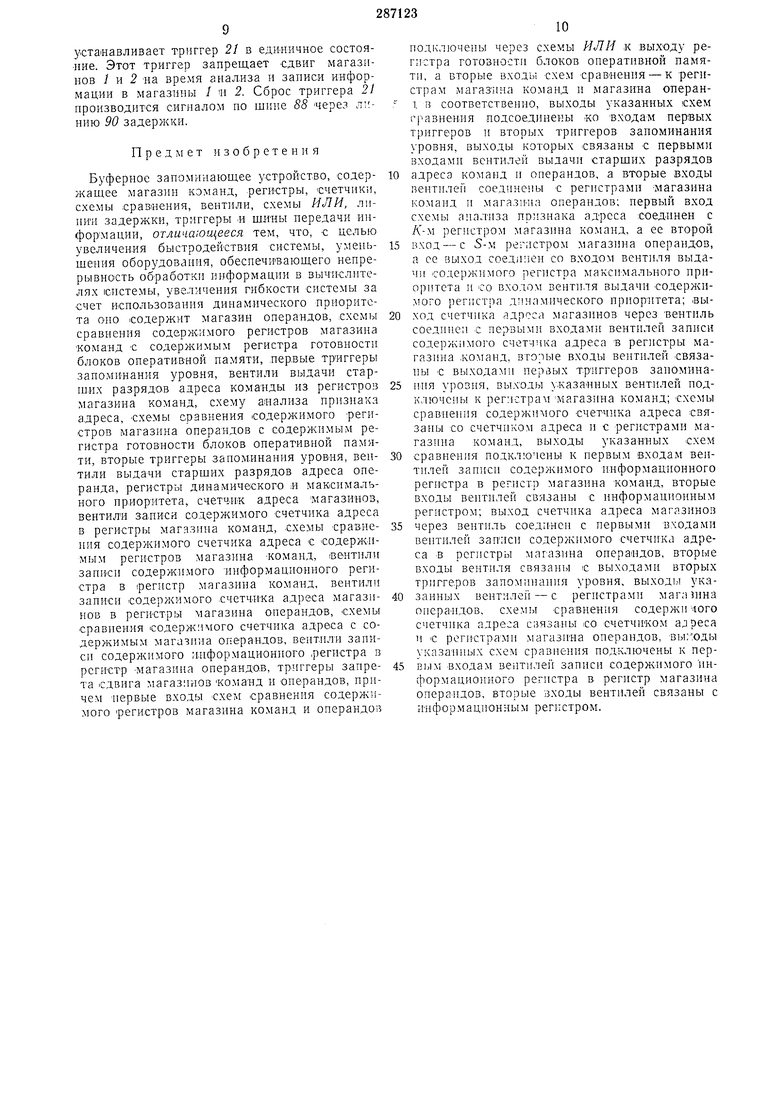

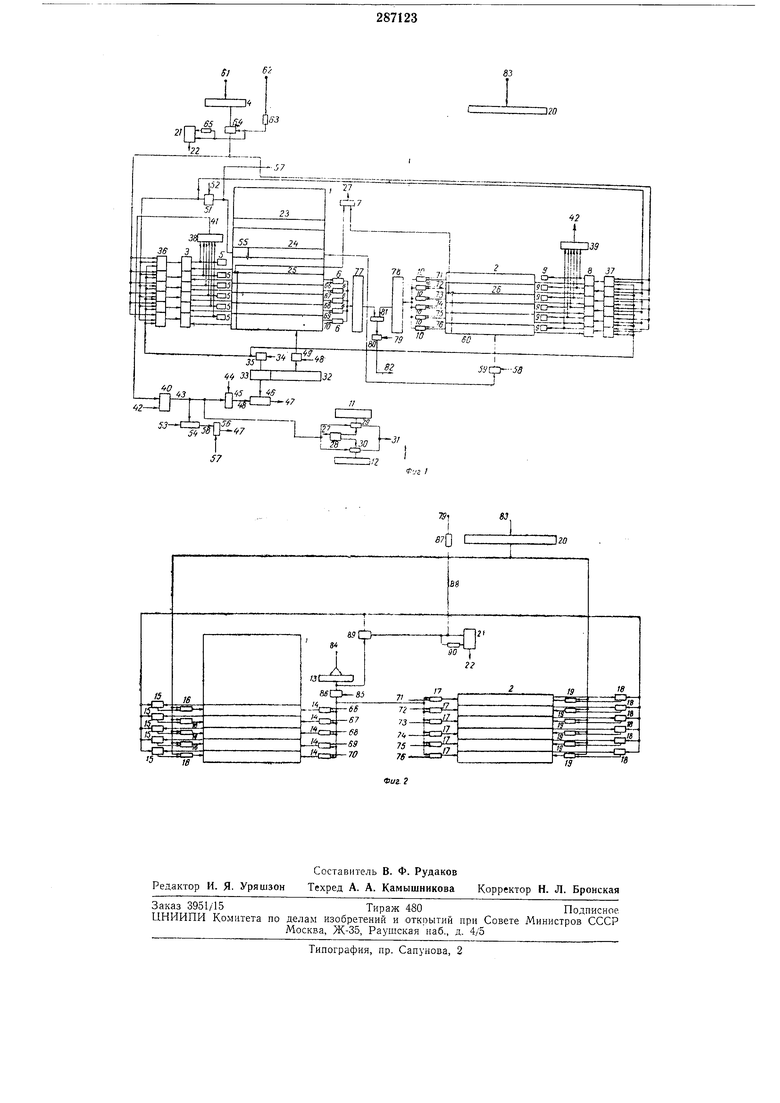

На фиг. 1 представлена функциональная схема части лредлагаемого устройства, ipeaдизующей формирование и посылку запросов в оперативиую память, анализ информации о готовности блокОВ памяти к обслуживанию запросов и вытачу сначала старшей, а затем младшей зоны адреса команды или операнда; на фиг. 2 - функциональная схема части предлагаемого устройства, реаЛИзуюндая распределение информации, иостуиаюш,ей ,нз блоков памяти по магазинам команд и операндов.

Общими узлами для фиг. 1 и фиг. 2 являются магазин 1 лсоманд и .магазин 2 операндов.

Вычислительная система содержит некоторое количество вычислителей и блоков оиеративной памяти, работаюш.их ио ириицнпу расслоения. Каждый из вычислителей может обращаться iK любому из блоков памяти но системе шин, связывающих вычислитель со всеми блоками. Начало обращения вычислителя к блоку наимяти заключается в иосылке старшей зоны слова обращения к блоку, представляющей собой п младших разрядов адреса, где Р - количество блоков памяти в стетеме. Одновременно посылается динамнческий приоритет данного вычислителя. Запросы, поступившие от разных вычислителей к некоторому блоку памяти, анализируются приоритетной схемой, которая организует очередь заиросов в соответствии с их дина.мическими приоритетами н вырабатывает расиределеипые во времени сигналы готовности от блоков памяти в виде п младших разрядов запроса. После анализа информации готовности в вычислителе нредлагаемое устройство выдает оста1вшуюся часть адреса в выбранный блок иамяти, который через время, определяемое циклом обрашения к блоку памяти, посылает в вычислитель соответствующую информацию, которая иомещается в оиределенный регистр магазинов предлагаемого устройства.

Предлагаемое устройство содержит магаЗИП У команд, магазин 2 оиерандов, схемы 3 сравнения содержимого регистров магазина команд с содержимым регистра 4 готовности блоков оперативной памяти, триггеры 5 запоминания уровня, вентилн 6 выдачи старших

разрядов адреса команды из регистров магазина ко.манд, схему 7 анализа признака адреса, схемы 8 сравнения содержимого регистров магазина онерандоз с содержимым регистра 4 готовности блоков оперативной намяти, триггеры 9 запоминания уровия, вентили 10 выдачи старших разрядов адреса операнда, регистрЕл 11 и }2 динамического и максимального приоритетов соответственно, счетчик 13 адреса магазниов, вен гили 14 записи содержимого

счетчика адреса в регистры магазина команд, схемы 15 сравнения содержимого счетчика адреса с содержимым регистров магазина / команд, вентили 16 заннси содержимого ннформаг(ионного регистра в регистр магазина / команд, вентили 17 записи содерл имого счетчика адреса магазинов в регистры магазина 2 операндов, схемы 18 сравнения содержимого счетчика / адреса с содержимым магазина 2 операндов, веитили 19 записи содержимого информаплонного регистра 20 в регистр магазина 2 оиерандов, триггеры 21 запрета сдвига магазинов команд и операндов с шнной 22 запрета сдвига. Магазин / команд нредназначен для хранення команд и адресов

тех команд, выборка которых :из намяти невозможна из-за конфликтов в блоках памяти. Сдвпг магазина вверх осуществляется асинxpOiHHO по завершению очередной операции в вычислителе. Выборка команды для ее обработки вычислителем производится из регистра 23 магазина. В регистре 23 могут находиться только команды, а не адреса команд, так как глубина нижней части магазина выбирается из сообрал ений разрешения конфликта в памяти к МОменту поступления информации в регистр 23. В промежутке между двумя сдвигами в магазине команд происходит два обращения; обращение за командой и за онерандом, если требуется выборка онеЧастота заполнения магазина / команд и магазииа 2 опера.идов может в отдельные моменты временн существеипо превышать частоту обращений к памяти нз-за асннхронностн разрешения конфликтов в отдельных блоках намятн. После разрешения конфликта адресная ИнфОрмация в магазине / команд заменяется командой.

Апалогнчно работает магазин 2 операндов, который предназначен для хра(11ения онерандов и адресов тех операндов, выборка которых задерживается из-за конфликтов в блоках памяти.

Выборка адреса операндов нронсходит из регистра 24 магазина / ;комаид. Регистр 24 хранит только команды, а не адреса команд, что обеспечивается выбором глубины нижней части магазина команд.

магазина 2 операндов меньше глубины магазина / команд и равна разнице в уровнях регистров 23 и 24.

За счет наличия ъ вычислителях оперативных регистров, не ноказанных на фиг. 1 и предназначенных для хранения промежуточных результатов вычислений, частота обраще«ий за операндами будет существенно меньше, чем Частота обращения за командами, что объясняет разницу в глубинах магазина команд и магазина операндов.

Таким образом, при выборке очередной команды для ее обработки вычислителем соответствующий операнд выбирается или из одного из оперативных регистров или из верхнего регистра магазина операндов.

Схема 7 анализирует наличие адресной информации в регистрах 25 и 26, соответствующих предельно допустимому уровню продвижения адреса в магазинах 1 и 2. Если адресная И1нформац11я окажется выще уровня регистра 25 ИЛИ 25 и не будут приняты специальные меры ио ускорению разрешення конфликтов .при обращении к памяти, то имеется большая вероятность того, что эта адресная информация продв11} ется и до уровня 24 или 26 соответственно, что приведет к блокировке процесса вычисления. В предлагаемой системе задачам, рещаемым в вычислителях, присваивается некоторый приоритет в зависимости от степени их важности. Указанный приоритет позволяет организовать оптимальную загрузку вычислительной системы: в первую очередь рещаются задачи с высшим приоритетом. Кроме этого, в процессе работы вычислительной системы приоритет ог.ределяет порядок доступа вычислителей к блокам памяти.

Такая организация доступа к блокам памяти ие является достаточно гибкой: возможны ситуациИ, когда вычислитель, решающий задачу с малым приоритетом, оказывается блокированным, так как во всех блоках памяти конфликты при обращениях к ним разрешаются в пользу вычислителей, имеющих более высокие, приоритеты.

В предлагаемом устройстве для увеличения гибкости системы вводится динамический ириоритет. Динамический приоритет равен вышеопределенному приоритету нри отсутствии критической ситуации, могущей привести к блокировке вычислителя, и равен максимальному значению этого приоритета при возникновении такой ситуации.

При срабатывании схема 7, сигнализирующая о возникновении критической ситуации (наличие адресной информации в регистрах 25 или 26 магазинов / и 2), формирует прпзнак критпческой сптуацип на шине 27,

взводящий триггер 28. Код динамического приоритета хранится в регистре //, а максимально возможное значение этого :кода хранится в репгстре 12. Триггер 2S управляет выдачей регистров 11 или 12 через схемы совпадения 29 и 30 соответственно в блоки памят 1 по нише 31. Таким образом, при возникиозешп критической сптуации приоритет, храHiiuuniCH в приоритетных схемах блоков памяти и соответстпуюп1,ий неудовлетворенны.м

запросам да 1ного вычпслителя, заменяется на максимальный на время ликвидации критической ситуации. Признак критической ситуации на щине 27 сохраняется на это время. Расс тотрим работу предлагаемого устройства. Счет адресов команд ведет счетчик 32. Как уже упо п палось, обращение к па.мяти за командой начинается с посылки старшей зоны 33 адреса команды (младшие разряды адреса) в блок памяти. На систему наложено

ограничение, заключающееся в том, что запрещается носылка заироса со стороны вычислителя к блоку памяти, у.же занятому его обслуживанием. Поэтому иеред посылкой старшей зоны 33 адреса команды производится ее

сравиение со старшими зонами всех адресов, хранящихся Б магаз ;нах / и 2. Синхросигнал, 11осылаемы: 1 по ишпо 34, открывает вентиль 55, и зона 33 поступает через схемы 36 и 37 ИЛИ на схемы 3 м 8 сравнения. Выходы

схем 5 сравнения объединены схемой 58 ИЛИ, а выходы схем 8 сравнения объединены схемой 55 ИЛИ. Выходы схем 55 и 55 связаны со схемой 40 совпадения шинами 41 и 42. Отсутствие сигналов сравие П1я на щинах 41 и

42 ириводит к выработке управляющего сигнала выдачи иа щине 43, вследствие чего при поступленпн синхроимпульса по шине 44 схема 45 совпадения срабатывает, и старшая зона 55 команды выдается через вентиль 46 на

шину 47, связанную с блоками памяти. Одновременно сигнал на шине 48 открывает вентиль 49, и содерж.имое счетчика 52 команд иереппсывается в нижний регистр 50 магазина команд.

Аналогично происходит формирование сигпала обращения за операндом. Отметим, что за иромежуток времени между двумя сдвигами магазинов / и 2 происходит одно обращение за командой и одно обращение за операнасинхронно по завершению обработки очередной кома-нды в вычислителе.

С регистра 24 магазина / старшая зона адреса операнда (младшие разряды адреса) гзыдается через вентиль 51 ири -наличии сиихроимпул1):са па тииие 52 на схемы 36 и 37 ИЛИ It далее па схемы 3 и 8 сравнения. Отсутствие сигналов сраъиеИИЯ на шииах 41 i 42 нриводит к выработке управляюшего 1сигнала выдачи по шине 43, вследствие чего при пОСтуплеппи -снихроимнульса по шине 53 схема 54 совиаделия срабатывает, и старшая зоиа 55 адреса опе11аида выдается через вентиль 56, Прпчем зоиа 55 иостуиает на вентиль 56 по 57.

Одповременно сигнал ио innne 58 открывает вентиль 59, следствпе чего нолный адрес операнда передается из -регистра 24 магазииа / комаид в нижиий регистр 60 магазина онерапдов.

Как ирн обрангеиии за командой, так и ири обрашепин за операндом сигнал по ши1не 43 открывает вентили 29 и 30 в зависимости от состояиия триггера 28. Если сигналы запросов к памяти посылаются из вычислителя через оиределеииые иитервалы времени с частотой не выше двух занросов на одну операцию в вычислителе, то сигналы готов-ности из блоков иамяти могут приходить со значительно большей частотой, оиределяемой приоритетной схемой блока намяти.

Максимальная частота и-осг,1лки сигиалов готовности оиреде.тяется способностьчо азычислителя обработать эти сигналы. Сггиал готовности ОТ иекоторого блока памяти приходит по ншие 61 в виде старшей зоны адреса запроса и иостуиает на регистр 4.

Схема ИЛИ, связанная со всеми разрядами регис/гра 4, и диффереппируюн ая цеиочка, пе показанные на ри-супках, формируют сигиал иа шиие 62, который, проходя через линию 63 задержки, открывает вентиль 64 и одиовремеиио устаиавливает триггер 21 в единичное состояние. Триггер 21 заиреш;ает сдвиг магазинов / и 2 на время обработки сигнала готовности. СбрОС триггера осушествляется при номоши Схемы 65 задержки. Вентиль 64 выдает старшую зону адреса из регистра 4 через схемы 36 -и 37 ИЛИ aia схемы 5 и 8 сравнения, выходы которых соединены с триггерами 5 и 9 заиомииаиия уровия. При обнаружении соответствия содержимого регистра 4 старшей зоне адреса, хранящегося в одном из регистров магазипа 1 или 2, ирои-сХОднт устаиовка в едиинцу соответствуюш,его триггера 5 или 9. Шииы 66-70 связаны с выходами соответствующих триггеров 5, шины 71-76 связаны с выходами соответствующих триггеров 9. При в-озникновении сигнала но одной из шии 66-70 или 71-76 ироисходит выдача младшей зоны адреса (старших разрядов адреса) команды или онеранда соответственно из магазинов / ИЛ . п регистры 77 или 78 соответствеНПО.

При поступлении синхроимнульса 79 на веитиль 80 содержимое регистров 77 или 78 через схему 81 ИЛИ выдается на шину 82, связанную с блоками памяти. Через время,

определяемое временем выборки информации из намяти, па информационный регистр 20 ио шине 83 постуннт команда или онеранд. Одновременно с выдачей младшей зоны адреса но щине 82 нроизводнтся заиись содержимого

счетчика 13 адреса магазинов в тот регистр магазинов / или 2, из которого производилась Выдача -младшей зоны адреса. На вход счетч:ика 13 но шине 84 иостунают синхросигналы из нриоритетной схемы блоков памяти, не ноказанной «а рисунках; таким образо1М, счетчик 13 изменяет овое состояние с максимально доиустимой частотой следования сигналов готовности из блоков онеративной намяти.

СчетчнК 13 счнтает но модулю- , где

- с

СИГН. ГОТОВН.

Твыб. из памяти-вре.мя выборки информации ИЗ блока памяти, Гсинг.готовн.-минимальный период следования сигналов готовности.

Это нрИБОДит к то.му, что содержимОе счетчика 13 в момент посылки младшей зоны адреса в намять ч содержимое счетчика 13 в момент поступления на регистр 20 информации, Соответствующей этому запросу, совпадают.

Занисывая -содержимое счетчика 13 в момеит посылки младшей зоны адреса на регистр, из которого эта 30)ia выдается, МОжно обеспечить однозначное распределение иоступившей иа регистр 20 информацни в магазинах / или 2 иутем сравнения содержимого счетчика 13 с соответствующей зоной регистров магазиНОв 1 п 2 при иостуилении информации в рсгисгр 20. Синхроимнульс по шнне 85, вырабатываемый носле завершения выдачи младшей зоны адреса из регистров 77 или 78, открывает вентиль 86 и выдает содержимое счетчика 13 на схемы 14 и 17 совиадения, вторые входы 66-76 которых связаны с

соответствующими тритгерами 5 и 9 запоминания уровня. Таким образом, производится запись содержимого счетчика 13 в тот регистр магазиНов 1 и 2, из которого происходила выдача младшей зоны адреса. Сигнал с шины 79

иостуиает на линию «§7 задержки с временем задержки, равным Твыв. из памяти-Поэтому выработка сигнала на шине 88 совнадает с моментом нриема информации на регистр 20. Сигнал на щине 88 открывает вентиль 89, который передает содержимое счетчика 13 на схемы 15 и 18 сравнения, выходы которЕлх соединены с первыми входами соответствующих схем 16 и 19 совнаден-ия. Вторые входы схем 16 и 19 нодключены к информационному регистру 20. При обнаружении совпадения содержимого счетчика 13 с соответствующей зоной ОДНОГО из регистров магазинов / или 2 производится запись содержимого регистра 20 через схемы 16 и 19 ъ соответствующий реустанавливает триггер 21 в единичное состояние. Этот триггер запрещает сдвиг магазинов 1 2 на время аиал,иза и записи информации в магазины 1 и 2. Сброс триггера 21 производится сигналом по шине 88 через линию 90 задержки.

Предмет изобретения

Буферное запоминающее устройство, содержащее магазин команд, регистры, счетчики, схемы сравиения, вентили, схемы ИЛИ, линии задержки, триггеры .и щины передачи информации, отличшощееся тем, что, с целью увеличения быстродействия системы, уменьшения оборудования, обеспечивающего непрерывность обработки информации в вычислителях юистемы, увеличения гибкости системы за счет исиользования динамического приоритета оно содержит магазин операндов, схемы сравнения содерж.имого регистров магазина Команд с содержимым регистра готовности блоков оперативной памяти, .первые триггеры запоминания уровня, вентили выдачи старших разрядов адреса команды из регистров магазина команд, схему аиализа признака адреса, схемы сравнения содержимого регистров магазина операндов с содержимым реги:стра готовности блоков оперативной памяти, вторые триггеры запоминання уровня, вентили выдачи старщих разрядов адреса операнда, регистры динамического ;И максимального приоритета, счетчик адреса магазинов, вентили заииси содержимого счетчика адреса в регистры магазина команд, схемы сравнения содер/кимого счетчика адреса с содержимым регистров магазина КОманд, (вентили записи содержимого информационного регистра в регистр магазина комаид, вентили заииси содержимого счетчи:ка адреса магазинов в регистры магазина онерандов, схемы сравнения содержимого счетчика адреса с содержимым магазина операндов, веитили записи содержимого информационного регистра в регистр Магазина операндов, триггеры запрета сдвига магазинов «оманд н операндов, причем первые входы схем сравнения содержимого регистров магазина команд и операндов

10

подключены через схемы ИЛИ к выходу регистра готовности блоков онеративной памяти, а вторые входы схем сравнения - к регистрам магазина команд и магазина оперант, в соответственно, выходы указанных схем сравнения подсоединены «о входам первых триггеров и вторых триггеров запоминания уровня, выходы которых связаны с первыми входами вентилей выдачи старщих разрядов

адреса команд и онерандов, а вторые входы вентилей соединены с регистрами Магазина комаид и магазиИа операндов; первый вход схемы анализа признака адреса соединен с Л-м регистром магазина команд, а ее второй

вход - с S-M per;icTpoM магазина операндов, а ее выход соединен со входом вентиля выдачи содержимого регистра максимального приоритета и со входом вентиля выдачи содержимого регистра динамического приоритета; выход счетчика адреса магазинов через вентиль соединен с первыми входами вентнлей записи содержимого счетчика адреса в регистры магазниа .команд, вторые входы вентилей связаны с выходами первых триггеров заноминання уровня, выходы указанных вентилей нодключеиы к регистрам магазина команд; схемы сравнения содержимого счетчика адреса связаны со счетчиком адреса и с регистрами магазииа команд, выходы указанных схем

сравнения подключены к первым входам вентилей заниси содержимого информационного регистра в регистр магазина команд, вторые входы вентилей связаны с информациоиным регистром; выход счетчика адреса магазинов

через вентиль соединеи с первыми входами вентилей заииеи содержимого счетчика адреса в регистры магазина онерандов, вторые входы вентиля связаны с выходами вторых триггеров запомииання уровня, выход1л указанных вентилей - с регистрами маг;пнна онерандов, схемы сравнения содержи-юго счетчика адреса связаны со счетчиком адреса и с регистрами магазина операндов, выводы указанных схем сравиення нодключены к первым входам вентилей записи содержимого информационного регистра в магаз 1на операндов, вторые 1зходы вентилей связаны с ршформационным регистром. Si

| название | год | авторы | номер документа |

|---|---|---|---|

| ЛАТЕНТНО-УЕХиЛ-ГКАЯ,БИБЛИОТЕКА | 1970 |

|

SU283685A1 |

| ПРИОРИТЕТНОЕ УСТРОЙСТВО ДЛЯ ЦИФРОВОЙ ВЫЧИСЛИТЕЛЬНОЙ СИСТЕМЫ | 1970 |

|

SU281901A1 |

| ЦЕНТРАЛЬНЫЙ ПРОЦЕССОР МУЛЬТИПРОГРАММНОЙ МУЛЬТИПРОЦЕССОРНОЙ ВЫЧИСЛИТЕЛЬНОЙ СИСТЕМЫ | 1971 |

|

SU309363A1 |

| Микропрограммное устройство для анализа программ | 1980 |

|

SU943729A1 |

| Устройство для перевода выражений в польскую инверсную запись | 1982 |

|

SU1130879A1 |

| Имитатор канала | 1987 |

|

SU1467556A1 |

| Устройство синтаксически управляемого перевода | 1989 |

|

SU1651298A1 |

| УСТРОЙСТВО Д.ПЯ ИЗВЛЕЧЕНИЯ КВАДРАТНОГО КОРНЯ | 1971 |

|

SU300449A1 |

| Устройство управления процессора | 1988 |

|

SU1670686A1 |

| Микро-ЭВМ | 1982 |

|

SU1124316A1 |

I ,

.70 czzz-i

Зм

S9 70

гг

17

я

2

/#

Авторы

Даты

1970-01-01—Публикация