щий буферный регистр ввода 12, блок управления 13, блок управления 14 внешней памятью, арифметико-логический блок 15, блок 16 оперативных ре- гистров, блок 17 локальной памяти, приемный буферный регистр вывода 18, два буферных регистра вывода 19 и 20, передающий буферный регистр вывода 21, схему 22 дополнения до четности. Pea- лизуя свои функции,процессор jftwiynpo- водниковой внешней памяти позволяет сократить объем данных, передаваемых по каналам обмена между вычислительной системой и полупроводниковой внешней памятью, освободить центральный процессор от работы по формированию массивов данных, более эффективно использовать оперативную память за счет управления распределением полупроводниковой внешней памяти непосредственно процессором полупроводниковой внешней памяти, а также вести тестирование и наладку полу провод ни-4 ковой внешней памяти без использования центрального процессора. 5 з.п, ,ф-лы, 7 ил

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1984 |

|

SU1254495A1 |

| Устройство для управления вводом-выводом | 1989 |

|

SU1735859A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1984 |

|

SU1288704A1 |

| Адаптивная система обработки данных | 1987 |

|

SU1451713A1 |

| Система ввода-вывода для микропрограммируемой ЭВМ | 1988 |

|

SU1667084A1 |

| Устройство для обмена данными в многопроцессорной вычислительной системе | 1983 |

|

SU1136143A1 |

| Устройство для сопряжения ЭВМ с магистралью локальной сети | 1990 |

|

SU1839258A1 |

| Устройство для сопряжения процессора с группой блоков памяти | 1987 |

|

SU1587518A1 |

| Устройство для контроля микропроцессорной системы | 1990 |

|

SU1753474A1 |

| УСТРОЙСТВО КОНТРОЛЯ ПРОЧНОСТИ КРЫЛА ВОЗДУШНОГО СУДНА | 2011 |

|

RU2469289C1 |

Изобретение относится к вычислительной технике и может быть использовано в высокопроизводительных вычислительных системах. Целью изобретения является экономия адресных пространств полупроводниковой внешней памяти и оперативной памяти, расширение функциональных возможностей и повышение производительности вычислительной системы за счет реализации произвольных алгоритмов доступа к данным и их предварительной обработки. Процессор полупроводниковой внешней памяти включен в состав высокопроизводительной вычислительной системы, содержащей оперативную память, центральный процессор, устройство ввода/вывода, полупроводниковую внешнюю память, устройство управления дисками, диски, причем процессор полупроводниковой внешней памяти содержит приемный буферный регистр ввода 8, два буферных регистра ввода 9 и 10, схему 11 контроля четности, передающий буферный регистр ввода 12, блок управления 13, блок управления 14 внешней памятью, арифметико-логический блок 15, блок 16 оперативных регистров, блок 17 локальной памяти, приемный буферный регистр вывода 18, два буферных регистра вывода 19 и 20, передающий буферный регистр вывода 21, схему 22 дополнения до четности. Реализуя свои функции, процессор полупроводниковой внешней памяти позволяет сократи

жила владимир васильевич

евтеев геннадий николаевич

ляпунцова елена вячеславовна+2069132SWIтснING DeVIce11 347915 таганрог ростовской обл., чехова 2211 347931 таганрог, п.тольятти 14-18

11 347902 таганрог, тр.резервов 7-7

11 347900 таганрог, свердлова 6

Изобретение относится к вычисли- тельной технике и может быть использовано в высокопроизводительных вычислительных системах.

Целью изобретения является экономия адресных пространств полупровод- никовой внешней памяти и оперативной памяти, расширение функциональных возможностей и повышение производительности вычислительной системы за счет реализации произвольных алгорит- мов доступа к данным и их предварительной обработки.

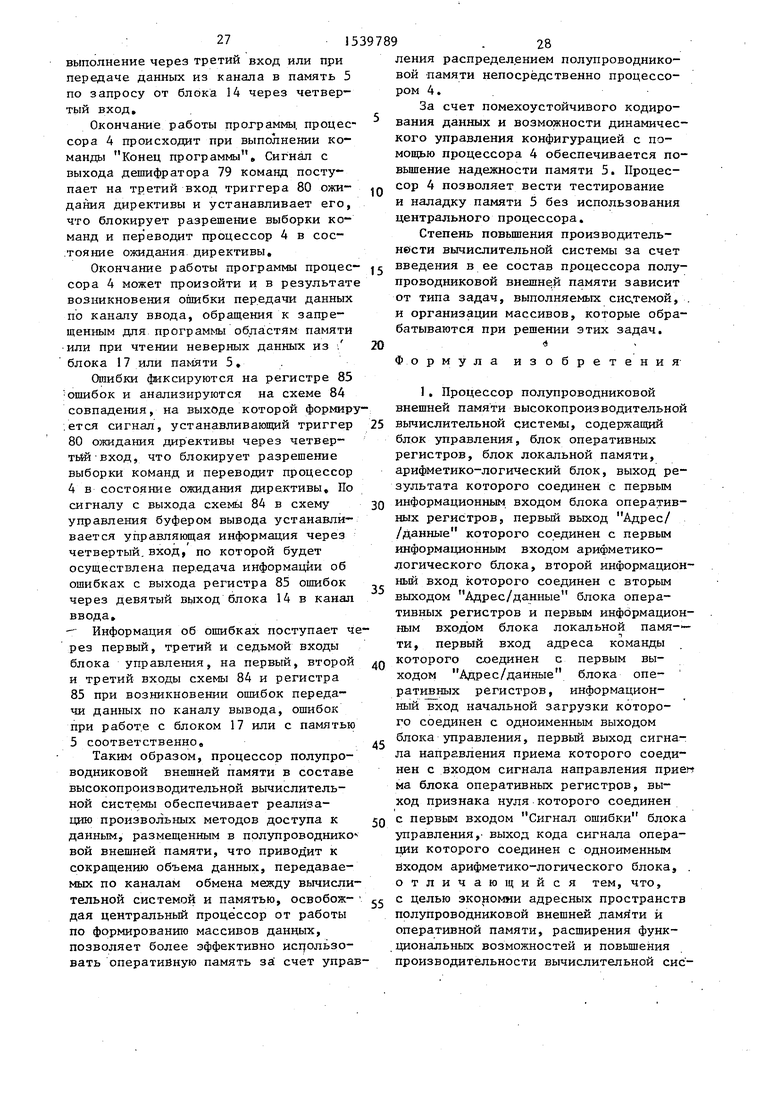

На фиг.1 показана структурная схема высокопроизводительной вычислительной системы с процессором полупровод

никовой внешней памяти; на фиГ.2 - . структурная схема процессора полупроводниковой внешней памяти; на фиг.З - структурная схема блока управления внешней памятью; на фиг.А - структур- ная схема блока локальной памяти; на фиг.5 - схема блока оперативных регистров; на фиг.6 - схема арифметико- логического блока; на фиг.7 - схема блока управления,

Вычислительная система содержит оперативную.память 1, центральный процессор 2, устройство -3 ввода-выво да, процессор 4 полупроводниковой внешней памяти, полупроводниковую

внешнюю память 5, устройство 6 управления дисковыми накопителями и дисковые накопители 7.

Управление обменом с полупроводниковой внешней памятью в вычислительной системе осуществляется следующим образом.

По запросу задачи пользователя операционная система центрального про

0

5 9

5

Q

Q

5

цессора определяет области памяти 1 и памяти 5, которые будут участвовать в обмене, а также программу, в соответствии с которой будут формироваться адреса и будет осуществляться обмен данными с памятью 5.

Программа, а также параметры,которые содержат сведения об областях памяти 5, участвующих в обмене, направляются в локальную память процессора 4. Непосредственно еред програм- . мой и параметрами в процессор 4 пере- дается информация, управляющая загрузкой программы и параметров и установкой границ областей памяти 5 и локальной памяти процессора 4, разрешенных для данного обмена

Информация, управляющая Загрузкой программы и параметров в память про-- цессора 4, собственно программа и параметры составляют так называемую директиву,

Вычислительная система осуществляет связь памяти 5 через устройство 3 и процессор 4, Для загрузки директивы или, передачи массива данных операционная система передает в устройство 3 управляющую информацию, содержащую описание областей оперативной памяти вычислительной системы, в которых размещена директива или откуда будет записан или считан массив данных.

Процессор 4 после очередного сеан-. са обмена переводится в состояние ожидания директивы. Находясь в таком состоянии, процессор 4 воспринимает первые слова, поступающие на его вход в качестве управляющих слов директивы.

После приема директивы процессор 4 переключается на выполнение принятой программы, которая содержит команды обмена управляющие пересылкой данных между устройством 3 и памятью 5. Пересыпка осуществляется через процессор 4, в котором находится описание областей размещения данных в памяти 1 вычислительной системы.

При выполнении пересылки данных из памяти 1 в память 5 данные считываются из памяти 1 в устройство 3, откуда они передаются в процессор 4 Он формирует соответствующую адресную информацию и сигнал записи, осуществляет контроль правильности передачи данных из устройства 3, в процессор 4, организуя защиту памяти, формирует составной код информацион- ного слова для исправления двойных и одиночных и обнаружения тройных ошибок.

При выполнении пересылки данных из памяти 5 в память 1 вычислительно системы процессор 4 формирует адреса и сигналы, управляющие чтением данных из памяти 5, осуществляет исправление одиночных и двойных ошибок и онаруживает тройные ошибки. Данные из процессора 4 поступают в устройство 3, в котором хранится информация, указывающая, в какую область памяти 1 вычислительной системы должны быть переданы данные,считанные из памяти 5 в«р

Процессор 4 содержит (фиг,2) приемный буферный регистр 8 ввода, два буферных регистра 9 и 10 ввода, схему 11 контроля четности, передаю- щий буферный регистр 12 ввода, блок 13 управления, блок 14 управления внешней памятью, арифметико-логический блок 15, блок 16 оперативных регистров, блок 17 локальной памяти, приемный буферный регистр 18 вывода, два буферных регистра 19 и 20 вывода, передающий буферный регистр 21 вывода и схему 22 дополнения до четности.

Процессор 4 в составе высокопро- изводительной вычислительной системы предназначен для организаций обмена данными между устройством 3 и памятью 5 по каналам ввода и вывода и реализации произвольных методов до ступа к данным, хранящимся в памяти 5, с помощью программ , размещенных в блоке 17 локальной памяти и выполняемых аппаратурой процессора 4.

0

5

0

5 п

Q с

Q

5

5

Процессор 4 обеспечивает повышение надежности памяти 5 за счет помехе- устойчивого кодирования информации и программного восстановления информации, хранящейся в памяти 5, а также сбор и обработку статистических данных о сбоях в работе памяти 5.

Процессор 4 принимает информацию из устройства 3 через второй вход на первый вход регистра 8, С регистра 8 информация может быть передана в регистр 9 или в регистр 10 в зависимости от того, какой из буферных регистров-, открыт для приема. Данные в буферный регистр пересылаются группа- ми. Максимально группа может содержать шестьдесят четыре 64-разрядных слова. По окончании приема группы слов буферный регистр переводится из состояния приема в режим выдачи и начинает передавать информацию в процессор 4 через регистр 12,с выхода регистра 9 через первый вход регистра 12 или с выхода регистра 10 через второй вход регистра 12. Одновременно с переключением режима работы первого буферного регистра второй буферный регистр переводится в состояние приема информации из устройства 3. Управление считыванием из буферных регистров и переключением режимов их работы производится блоком 13 процессора 4. Сигналы управления поступают с первого выхода блока 13 на второй и третий входы регистров 8 и 12 соответственно. Аналогично организована работа пары регистров 19 и 20 и соответствующих регистров 18 и 21, предназначенных для передачи инфор мадии из памяти 5 в устройство 3, Управление записью в буферных регистрах и переключение режимов работы осуществляет блок 13 процессора 4, Сигналы управления поступают с второго выхода блока 13 на первый и третий входы регистров 18 и 21.

Информация передается по каналам связи между процессором 4 и устройством 3 словами, которые дополняются контрольными разрядами (контроль по четности). Переданная по каналу ввода информация поступает с выхода регистра 8 на вход схемы 11 контроля четности, на выходе которой формируется сигнал ошибки, поступающий на первый вход блока 13. Передаваемая в канал ввода информация с выхода регистра 21 поступает на вход схемы

22 дополнения до четности, с выхода которой контрольные разряды вместе с информационным словом через четвертый выход процессора передаются в устройство 3.

Процессор 4 имеет собственную локальную память, где хранятся программа и данные. При загрузке директивы для программы, которая будет выполняться, устанавливаются граничные условия по памяти блока 17. Граничные условия и программа поступают с первого выхода регистра 12 на первый вход блока 17 в процессе загрузки директивы.. Через первый выход блока 17 производится выдача команд в блок 13.

Адрес в блок 17 поступает по второму входу с регистра команды или по третьему входу со счетчика команд, расположенных в блоке 13, и выдается соответственно с третьего и четвертого выходов. Кроме того, адрес в блок 17 поступает через четвертый вход с первого выхода блока 16 реги- стров. Данные в блоке 17 передаются с второго выхода блока 16 регистров на пятый вход и с первого выхода блока 14 на шестой вход. Считанные данные из блока 17 через выход поступа- ют на первые входы блока 16 регистров и блока 14.

Сигналы, управляющие направлением приема адресов и данных, выдаются с пятого выхода блока 13 и принимаются на седьмой вход блока 17.

При выполнении операций обращения к блоку 17 памяти могут быть обнаружены ошибки при чтении данных и ошибки обращения по адресу к запрещенным областям блока 17 для данной программы. Сигналы об этих ошибках передаются с второго выхода блока 17 через третий вход в блок 13.

Блок 16 регистров предназначен для быстрого считывания операндов и записи результатов выполняемых команд. Организация блока 16 регистров позволяет в каждый такт считывать

один или два операнда, либо записывать один операнд.

Данные в блок 16 регистров поступают с первых выходов блоков 17, 14 и 15, через первый, второй и третий входы соответственна. Кроме того, Дан ,ные принимаются через четвертый , вход блока 16 регистров из блока 13. Эта же связь, используется для передачи в блок 16 регистров адреса. Ин

0

5

,Q 5 JQ

JQ

с

5

45

0

формация, управляющая приемом адресов и данных, поступает из блока 13 в блок 16 регистров через пятый вход. Считанные из блока 16 регистров операнды с первого и второго выходов направляются на первый и второй входы блока 15, на второй и третий входы блока 14 и на четвертый и пятый входы блока 17. Данные, считанные с первого выхода блока 16 регистров, направляются на четвертый вход блока 13 и на второй вход регистра 18.

При выполнении операций сложения, вычитания, сдвига , пересылки из регистров в регистр и логических операций результат записывается в блок 16 регистров и анализируется на равенство нулю, может быть выработан признак нуля, который поступает на пятый вход блока 13,

Арифметико-логический блок 15 служит для обработки целочисленных операндов и выполняет операции сложения, вычитания, логические операции и операции сдвига.

Операнды в блок 15 поступают через первый и второй входы из блока 16 регистров. Код операции поступает рез третий вход блока 15 с седьмого выхода блока 13. Результат выполнения операции выдается с первого выхода и записывается в блок 16 регистров.

При выполнении операций в блоке 15 может быть выработан признак переполнения разрядной сетки, который с второго выхода поступает на шестой вход блока 13,

Блок 14 управления внешней памятью непосредственно участвует в организации обмена вычислительной системы с памятью 5. Блок 14 организует обмен между памятью 5 и блоком 17, между памятью 5 и каналами связи с устройством 3, а также между памятью 5 и блоком 16 регистров. В процессе загрузки директивы для программы, которая будет выполняться, устанавливаются граничные условия, поступающие с выхода регистра 12 через четвертый вход блока 14. Данные в блок 14 в режиме записи в память 5 поступают с первого выхода регистра 12 через четвертый вход, из блока 17 - через первый вход, а из бло- ,ка регистров 16 - через второй и третий входы. После кодирования данные передаются в память 5 через второй выход. В режиме считывания из памя- ,

915

ти 5 данные в блок 14 поступают через пятый вход для обнаружения и исправления ошибок. После анализа, исправления и обнаружения олибок данные передаются через первый выход блока 14 на третий вход регистра 18, на шестой вход блока 17 или на второй вход блока 16 регистров.

Адресная информация поступает в блок 14 из блока 16 регистров или памяти 1в

После сравнения с граничными условиями и преобразования в соответст- ствии с конкретной конфигурацией памяти 5 адрес пересылается в память 5 через третий выход блока 14 Сигналы, управляющие работой блока 14, подаются с восьмого выхода блока 13 через шестой вход. Блок 14 вырабатывает сигналы управления работой памяти 5, которые через четвертый выход направляются в полупроводниковую внешнюю память.

Сигналы запроса адресов или дан-

ных, считываемых из блока 17 направления приема данных, считанных из памяти 5 , и сигналы нарушения граничных условий и обнаружения некорректируемых ошибок в данных передаются через пятый выход блока 14 на седьмой вход блока 13.

Управление работой всех устройств процессора и обеспечение их взаимодействия осуществляет блок 13 управления. Блок 13 обеспечивает загрузку директивы в процессор 4, формирует адрес команд, производит выборку команд из блока 17, дешифрирует код операции принятой команды, анализирует состояние регистров и устройств, участвующих в выполнении анализируемой команды. В случае готовности соответствующих регистров и устройств блок 13 вырабатывает разрешение на выполнение команды и сигналы, задающие временную диаграмму выполнения команды. Блок 13 следит за правильностью передачи информации по каналу, выдаваемой из памяти 5, считанной из блока 17, переводит процессор 4 в исходное состояние по окончании выполнения программы или при нарушении граничных условий,

По окончании выполнения программы или при возникновении ошибок блок 13 формирует код, который указывает на то, как выполнена программа и переда-

0

789

5

0

0

5

0

5

10

ет его через девятый выход на четвертый вход регистра 18,

В исходном состоянии первая переданная по каналу ввода информация воспринимается процессором 4 как директива и первое слово, содержащее управляющую информацию о загрузке программы и параметров и установке ограничений для программы по памяти блока 17 и памяти 5, с выхода регистра 12 поступает на восьмой вход блока 13.

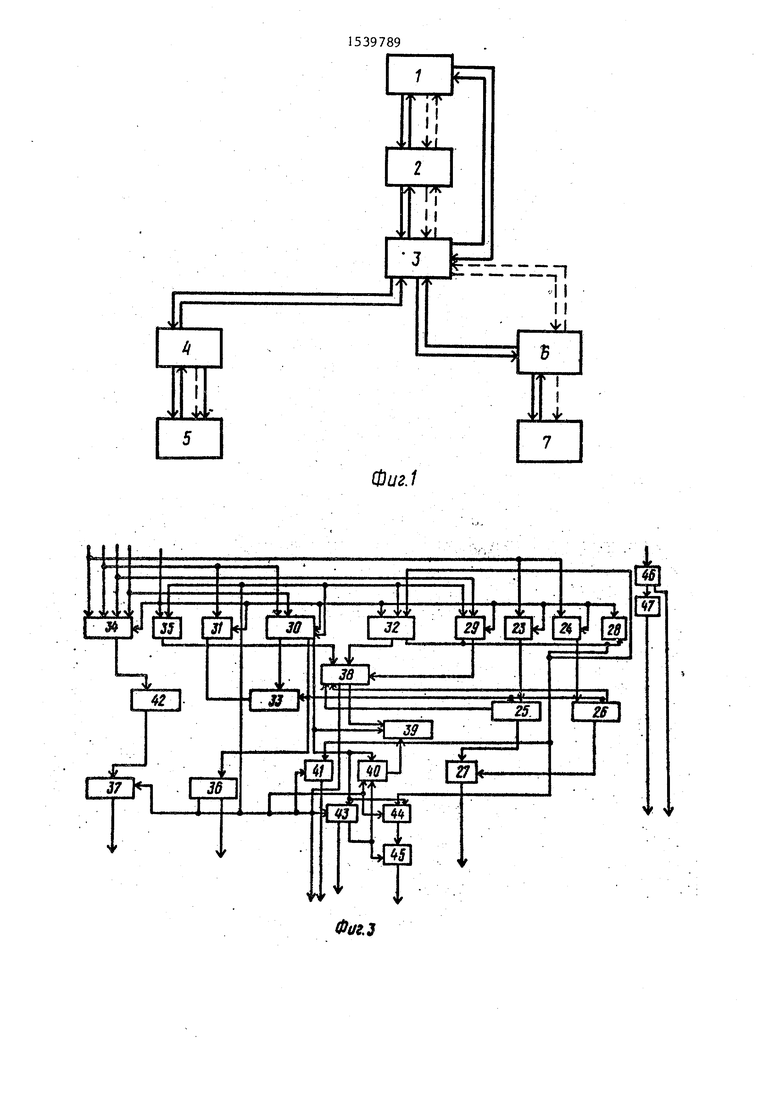

Блок 14 управления внешней памятью (фиг.З) содержит регистры 23 и 24 нижней и верхней границ адреса, две схемы 25 и 26 сравнения адреса с нижней и верхней границами, триггер 27 ошибки обмена, регистр 28

кода операции, счетчик 29 объема обмена, регистр 30 текущего адреса, регистр 31 приращения адреса, триггер 32 готовности адреса, сумматор 33 адреса, регистр 34 подготовки данных, 5 триггер 35 готовности данных, регистр 36 адреса, регистр 37 записи данных, схему 38 совпадения, схему 39 сравнения, регистр 40 незанятости кубов, триггер 41 записи, схему 42 кодирования, шестнадцать счетчиков 43 управления кубами, шестнадцать регистров 44 направления приема информации, мультиплексор 45, схему 46 декодирования и регистр 47 передачи информации.

Блок 14 выполняет операции обмена с памятью 5 и полностью контролирует ее работу.

Во время загрузки директивы на первые входы регистров 23 и 24 верхней и нижней границ принимаются граничные условия, поступающие с регистра передачи буфера ввода через четвертый вход блока 14. Указанная передача осуществляется с помощью сигнала управления загрузкой директивы, формируемого блоком 13 и поступающего на первые входы регистров 23 и 24, В процессе выполнения команд обмена в слу

чае, если текущий адрес памяти 5, поступающий на первые входы 25 и 26 схем сравнения, превышает какую-либо границу (значение граничных условий поступает на вторые входы схем 25 и 26 сравнения с выходов регистров 23 и 24), соответствующая схема 25 или 26 сравнения вырабатывает на выходе сигнал нарушения границы,который поступает на первый или второй вход триггера 27, ошибки

1)

обмена и через такт передается в блок 13 с выхода триггера 27учерез пятый выход блока 14.

Выполнение всех команд обмена начинается с загрузки кода операции и количества данных на первый вход регистра 28 кода операции и на первый вход 29 счетчика объема обмена. Прием количества данных происходит под управлением сигнала установки режима работы счетчика, который в данном . случае разрешает параллельный прием на счетчик 29, Сигнал установки режима формируется в блоке 13 и поступает через шестой вход блока 14 на второй вход счетчика 29,

Прием кода операции происходит в том случае, если содержание счетчика 29 равно нулю, т,е, в текущий момент, когда блок 14 не выполняет операции обмена. Сигнал нуля счетчика поступает с первого выхода счетчика 29 на второй вход разрешения приема регистру 28,

При загрузке операций обмена, в которых адреса памяти 5 формируются в блоке 14, из блока 16 регистров через второй вход блока 14 поступают последовательно значения начального адреса и адресного приращения соответственно на первые входы регистра 30 текущего адреса и регистра 31 приращения адреса. Управление приемом этих значений происходит при помощи сигналов разрешения приема начального адреса и адресного приращения-, поступающих через шестой вход блока 14 на вторые входы регистров 30 и 31

По сигналу разрешения приема начального адреса устанавливается триггер 32 готовности адреса. Сигнал разрешения приема поступает на первый вход триггера 32,

Операции обращения к памяти 5 могут происходить по непосредственным адресам, формируемым в блоке 44,или ( по косвенным адресам, хранящимся в памяти 174 В случае выполнения операции обмена по непосредственным адресам текущий адрес с выхода регистра ,30 текущего адреса и адресное смещение с выхода регистра 31 поступают на оба входа сумматора 33, с выхода которого следующий адрес передается tHa третий вход регистра 30,

Разрешением приема следующего адреса и выхода сумматора является сигнал разрешения внешней памяти, фор

10

15

20

мируемый на1 выходе схемы 38 совпадения и поступающий на четвертый вход регистра 30, Этот же сигнал поступает на вход сброса триггера 32 готовности адреса, но при обмене по непосредственным адресам сброс триггера по сигналу разрешения внешней памяти заблокирован сигналом кода операции, который поступает с выхода регистра 28 кода операции на третий вход триггера 32,

При выполнении обмена по косвенным1 адресам адрес из блока 17 поступает через первый вход блока 14 на пятый вход регистра 30 текущего адреса. Такой способ формирования адреса сохраняется на протяжении всего обмена. Управление передачей адреса из блока 17 памяти осуществляется сигналом разрешения приема адреса, поступающим через шестой вход блока 14 на второй вход регистра 30 и на первый вход триггера 32 готовности адреса, В отличие от организации обменов по непосредственным адресам при обмене по косвенным адресам адрес принимается на регистр 30 только по сигналам блока 13, а триггер 32 по каждому сигналу разрешения внешней памяти сбрасывается.

Команды обмена, осуществляющие запись в память 5, требуют периодической загрузки регистра 32 готовности данных. Данные в виде 64-разрядных слов поступают из регистра ввода и : блока памяти 17 через четвертый и первый входы блока 14 на первый и второй входы регистра 34, Данные в виде слов поступают с выхода блока 16 регистров через второй и третий вхо- ды блока 14 на третий и четвертый входы регистра 34, Управление загрузкой данных в регистр 34 по одному из направлений приема осуществляет блок 13, формируя сигнал разрешения приема данных, поступающий на пятый вход регистра 34, этот же сигнал поступает на первый вход установки триггера 32 готовности данных.

25

30

35

40

45

50

Оборудование, предназначенное для приема, анализа и переработки адреса. и данных в блоке 14, представляет core бой конвейер, состоящий из регистров 30 и 36 для адреса и регистров 34 и 37 для данных, причем регистры 37 и 36 являются выходными и связаны соответственно с вторым и третьим выходами блока 14, Передача информации в. конвейере осуществляется при условии, что есть сигнал разрешения внешней памяти, свидетельствующий о тем,. что разрешена передача адреса и данных при записи в память 5, или передача адреса в память 5 при чтении, а также разрешен запуск счетчиков управления кубами памяти 5

Анализ условий продвижения информации в конвейере осуществляет схема 38 совпадения. На входы этой схемы подается следующая информация: на первый вход - сигнал о готовности данных с выхода триггера 35, на второй вход - сигнал о готовности адреса с выхода триггера 32, на третий и четвертый входы - сигналы удовлетворения граничным условиям с первых выходов схем 25 и 26 сравнения, на пятый вход - сигнал отсутствия конфликта по доступу к кубам, на шестой вход - сигнал ненулевого состояния счетчика 29 объема обмена.

Сигнал отсутствия конфликта по доступу к кубам вырабатывается схемой 39 сравнения. Последняя представляет собой мультиплексор, на первый вход управления которого поступают младшие разряды текущего адреса с второго выхода регистра 30. Младшие разряды указывают номер куба, к которому произойдет обращение по текущему адресу. На второй вход данных мультиплексора поступают разряды регистра 40 незанятости кубов„Выходной сигнал схемы 39 свидетельствует об отсутствии конфликта по кубам.

При совпадении всех входных условий схема 38 вырабатывает сигнал разрешения внешней памяти, являющийся основным управляющим сигналом блока 14 и выполняющий следующие функции: разрешение продвижения конвейера адреса и данных, разрешение сброса соответствующего разряда регистра незанятости кубов, разрешение установки триггера 41 записи, уменьшение состояния счетчика 29 объема обмена на единицу, сброс триггеров 35 и.32 готовности данных и адреса, причем адреса только в случае обмена по косвенным адресам.

Кроме того, сигнал передается в блок 13, где участвует в формирова нии запроса следующего адреса из блока 17 в случае обмена в режиме косвенной адресации или вызова оче0

5

0

5

0

5

0

5

0

5

редкого слова данных из регистра ввода при осуществлении обмена регистра ввода и памяти 5 или из локальной памяти процессора 4 при обмене блока 17 и памяти 5. Этот сигнал также поступает на первый вход разрешения приема данных регистра 37 записи данных Подготовленные на регистре 34 и закодированные в схеме 42 кодирования данные поступают с выхода схемы 42 . на второй вход регистра 37, По сигналу разрешения внешней памяти, поданному на первый вход регистра 36 адреса,-, осуществляется подача адреса с второго выхода регистра 30 текущего адреса на второй вход регистра 37. Сигнал разрешения внешней памяти, поданный на первый вход триггера записи, разрешает прием признака записи с выхода регистра 28 кода операции при выполнении обмена по записи данных в память 5.

По сигналу разрешения внешней памяти , поданному на третий вход счетчика 29 объема обмена, его состояние уменьшается на единицу. Сигнал разрешения внешней памяти разрешает сброс разряда регистра незанятости кубов, поступая на первый вход регистра 40 по младшим разрядам регистра 30, которые подаются с первого выхода регистра 30 на второй вход регистра 40,

Работой кубов памяти 5 управляют 16 счетчиков 43 управления. Каждому кубу поставлен в соответствие один счетчик, Выбор нужного счетчика осуществляется с помощью младших разрядов адреса, поступающих из регистра 30 на первый вход счетчиков 43, Запуск выбранного счетчика производится сигналом разрешения внешней памяти, который поступает на второй вход счетчика 43, Счетчик запускается одновременно с приемом адреса и данных на регистры 36 и 37, После запуска счетчик начинает работать с частотой синхронизации процессора 4 и через определенное время, равное циклу работы куба, на выходе счетчика вырабатывается сигнал Конец цикла, который с нулевого выхода этого счетчика поступает на третий вход регистра 40 и устанавливает соответствующий данному счетчику разряд регистра 40 незанятости кубов, С первого выхода счетчиков 43 через четвертый выход блока 14 на память 5 поступает от каждого счетчика в соответствующий куб последовательность сигналов, задающая временную диаграмму работы куба.

Режим считывания из памяти 5 обеспечивается 16-ю регистрами 44 направления приема мультиплексором 45 направления приема информации, схемой 46

переводит

следукгции соответственно, что блок 14 в состояние ожидания щей операции обмена.

Блок локальной памяти содержит счетчик 48 адреса памяти, регистр 49 верхней границы, регистр 50 нижней границы, регистр 51 адреса локальной , схему 52 сравнения адреса с

памяти

декодирования и регистром 47 блока 14,.Q верхней границей, схему 53 сравнения

адреса с нижней границей,схему 54 сборки сигналов нарушения границы, внешней памяти, поступающему на первый вход регистров, принимается код направления приема считанной информа-

В шестнадцать регистров 44 жаправ- ления приема по сигналу разрешения

ции. Направление определяется кодом операции, поступающим в схему 44 через второй вход с выхода регистра 28 кода операции. На третий вход регистров 44 подаются младшие разряды реги- 20 стра 30, которые указывают код куба, из которого производится чтение, и в соответствующий регистр направления приема загружается код направлен ния приема 25

Мультиплексор 45 по сигналу Конец цикла работы куба, поступающему на первый вход с второго выхода счетчика 43, выбирает соответствующее направление приема информации, которое 30 поступает на второй вход мультиплексора 45 с выхода регистра 44, Код на правления приема информации с выхода мультиплексора 45 поступает через пятый выход блока 14 в блок 13, Данные из памяти 5 поступают в блок 14 через пятый вход и анализируются в схеме 46 декодирования, которая исправляет одиночные и двойные и обнаруживает тройные ошибки. Сигнал о некорректированной ошибке формируется на первом выходе схемы 46 и передается через пятый выход блока 14 в блок 13, Правильно считанные данные передаются с второго выхода схемы 46 через транслирующий регистр 47--и первый выход блока 14 по направлению, определенному мультиплексором 45, а именно на приемный регистр 8, если выполняется обмен с регистра вывода, 50 либо на вхдд блока 17, либо на вход блока 16 регистров.

Операции обмена с паматью 5 оканчиваются после того, как счетчик 29 объема обмена переходит в нулевое со- 5 стояние, и сигнал с второго выхода счетчика 29 поступает на четвертый и второй входы сброса триггера 32 готовности адреса и регистр 28 кода опера35

40

45

триггер 55 записи, регистр 56 записи схему 57 дополнения до четности, нак питель 58, регистр 59 чтения и схему 60 контроля четности. Блок 17 обеспечивает запись или чтение данных при темпе обращений одно слово за такт и цикле обращения два такта,

Схему блока 17 памяти можно разделить на две части, В одной части происходит прием, формирование и контроль адреса блока 17, Во второй части производится прием, хранение, контроль и выдача данных. Центральное место в адресной части занимает регистр 51 адреса. Этот регистр может принимать информацию из разных устройств процессора 4, Первый вход регистра 51 подключен к регистру коман блока 13 через второй вход блока 17, Эта связь используется при выполнении команд, в которых адрес блока 17 задается в адресном поле команды. На второй вход регистра 51 со счетчика команд блока 13 принимается адрес команды. На третий вход регистра 51 из блока 16 регистров через четгертый вход блока 17 поступает содержимое оперативного регистра. Такая передача осуществляется в командах, где адрес блока 17 указывается в одном из регистров 16 блока регистров, К четвертому входу регистра 51 подключен счетчик 48 адресов памяти. Счетчик 48 используется- для формирования адресов оперативной памяти в командах, организующих обмен между памятью 5 и блоком 17, а также в командах обмена с косвенной адресацией. Первоначальное значение счетчика адресов памяти для этих команд принимается через чет вертый вход блока 17 на первый вход счетчика 48, Кроме того, счетчик адресов памяти используется при загрузке директивы. Первоначальная установ ка счетчика 48 в э гом случае осуществляется по первому входу счетчика, связанному с выходным регистром бупереводит

следукгции соответственно, что блок 14 в состояние ожидания щей операции обмена.

Блок локальной памяти содержит счетчик 48 адреса памяти, регистр 49 верхней границы, регистр 50 нижней границы, регистр 51 адреса локально , схему 52 сравнения адреса с

памяти

адреса с нижней границей,схему 54 сборки сигналов нарушения границы,

0 5

0 0

5

5

0

5

триггер 55 записи, регистр 56 записи, схему 57 дополнения до четности, накопитель 58, регистр 59 чтения и схему 60 контроля четности. Блок 17 обеспечивает запись или чтение данных при темпе обращений одно слово за такт и цикле обращения два такта,

Схему блока 17 памяти можно разделить на две части, В одной части происходит прием, формирование и контроль адреса блока 17, Во второй части производится прием, хранение, контроль и выдача данных. Центральное место в адресной части занимает регистр 51 адреса. Этот регистр может принимать информацию из разных устройств процессора 4, Первый вход регистра 51 подключен к регистру команд блока 13 через второй вход блока 17, Эта связь используется при выполнении команд, в которых адрес блока 17 задается в адресном поле команды. На второй вход регистра 51 со счетчика команд блока 13 принимается адрес команды. На третий вход регистра 51 из блока 16 регистров через четгертый вход блока 17 поступает содержимое оперативного регистра. Такая передача осуществляется в командах, где адрес блока 17 указывается в одном из регистров 16 блока регистров, К четвертому входу регистра 51 подключен счетчик 48 адресов памяти. Счетчик 48 используется- для формирования адресов оперативной памяти в командах, организующих обмен между памятью 5 и блоком 17, а также в командах обмена с косвенной адресацией. Первоначальное значение счетчика адресов памяти для этих команд принимается через четвертый вход блока 17 на первый вход счетчика 48, Кроме того, счетчик адресов памяти используется при загрузке директивы. Первоначальная установка счетчика 48 в э гом случае осуществляется по первому входу счетчика, связанному с выходным регистром бу

21

перевод процессора 4 в состояние ождания директивы-установку триггера 8 В состоянии ожидания директивы пвая переданная через канал ввода информация воспринимается процессором как директива, С выхода регистра педачи буфера ввода через восьмой вход блока 13 первое слово директивы, содержащее порядок загрузки программы и параметров, поступает на первые входы схемы 81 совпадения и схемы 8 управления загрузкой директивы. На второй вход схемы 81 .совпадения с второго выхода триггера 80 ожидания директивы поступает сигнал о том, что этот триггер установлен. На выходе схемы 81 формируется сигнал, кторый поступает на второй вход схем 82 управления загрузкой директивы и разрешает ей прием управляющей инфомации Этот же сигнал поступает на второй вход сброса триггера 80 и на первый вход установки триггера 83 приема директивы, после чего будет сброшен триггер 80 ожидания и устанлен триггер 83 приема директивы. Во время приема директивы на регистры процессора 4 будут установлены гранные условие и адреса, необходимые для работы программы, а также будут записаны программа и параметры в блок 17,

I

При приеме директивы с выхода триггера 83 на второй вход схемы 95 сравнения поступает сигнал, который блокирует выборку сигнале разрешения выборки команд. На первом выходе схемы 82 управления загрузкой директивы формируется сигнал, который поступает на второй вход счетчика адресов команд и разрешает прием начального адреса программы, поступившего через восьмой вход блока 13 на третий вход счетчика 74 из канала, С этого же выхода схемы 82 сигналы разрешения приема передаются в блок 14 и блок 17, где разрешают прием граничных условий на регистры границ, С первого выхода схемы 82 сигналы разрешения приема программы и параметров поступают на вторые входы схем управления локальной памятью 87, счетчиком адреса локальной памяти 90 и буфером ввода 94, что позволяет загрузить на счетчик адреса локальной памяти начальный адрес программы и параметров и записать ИУ в блок 17 по адресам,

22

0

5

0

5

0

5

0

5

0

5

формируемым на счетчике адреса локальной памяти.

Все схемы управления функциональными устройствами (схемы 82, 86-94), входящие в состав блока управления, представляют собой конвейер, на ступени которого загружается управляющая информация, 41 о определяет жесткое выполнение временной диаграммы операций процессора 4. По сигналу разрешения приема на ступень конвейера принимается управляющая информация, которая затем передается с одной ступени конвейера на другую в каждый такт синхронизации. Выход нижней ступени конвейера управления функциональным устройством соединен с входом управления приемом на входные регистры соответствующего исполнительного устройства.

По окончании загрузки директивы на втором выходе схемы 82 формируется сигнал, который указывает, что директива загружена, и поступает на второй вход сброса триггера 83 приема директивы. После сброса триггера 83 блок 13 начинает выполнение программы и на выходе схемы 95 формируется сигнал разрешения выборки команд, поступающий на входы разрешения счета счетчика 74 адресов команд, буферного регистра 77 команд и регистра 78 команд,С выхода счетчика 74 первый адрес команды поступает на первый вход схемы 75 сравнения, на второй вход которой с выхода буферного регистра 76 адресов команд подаются адреса команд, хранящихся в буферном регистре команд. Если адрес, указанный на счетчике 74, не совпадает ни с одним из адресов команд, хранящихся в регистре 77, то происходят запись этого адреса в регистр 76, чтение команды из блока 17 по этому адресу и запись команды в регистр 77, а затем передача ее для выполнения на регистр 78, R случае несовпадения адресов, на первом выходе схемы 75 появляется сигнал, который поступает на первый вход регистра 76 и разрешает прием адреса с выхода счетчика 74 через второй вход в регистр 76, Сигнал с первого выхода схемы 75 также поступает на второй вход регистра 77 и разрешает прием команды, прочитанной из блока 17, поступившей в блок J3 через второй вход и записанной через третий вход в регистр 77. Сигнал

несовпадения с первого выхода схемы 75 сравнения также поступает на третий вход схемы 87 управления локальной памятью и устанавливает управляющую информацию, по которой из блока 17 будет считана команда. Адрес команды с выхода счетчика 74 через четвертый выход блока 13 передается в блок 17, Если адрес команды, указанной на счетчике 74, совпадает с одним из адресов, хранящихся в регистре 76, то соответствующая этому адресу команда поступает из регистра 77 на регистр команд для выполнения. На втором выходе схемы 75 сравнения появляется сигнал, который передается в регистр 77 через четвертый вход и разрешает чтение команды, соответствующей совпавшему адресу.

Команда с выхода регистра 77 поступает на второй вход регистра 78 команд и принимается туда, если на его первом входе есть сигнал разрешения выборки команд, С выхода регистра 78 она поступает на вход дешифратора 79 команд и на четвертый вход счетчика 74 адресов команд, последняя связь используется в том случае, если выполняется команда передачи управления по адресу, указанному непосредственно в команде.

Адрес оперативного регистра, константа и адрес локальной памяти могут быть также указаны непосредственно в команде. Информация с выхода регистра команд через третий выход блока 13 передается в .блок 16 регистров или в блок 17«

После дешифрации код команды поступает на вход схемы 95 сравнения, где производится анализ свободных ресурсов , .необходимых для выполнения выдаваемой команды. Схемы 95 сравнения вырабатывает сигнал разрешения выборки команд, который является основным сигналом разрешения загрузки и

выдачи на выполнение команды, I

Код команды с выхода дешифратора 79 поступает на третий вход схемы 95 и на входы схем управления устройствами процессора 4,

На входы с 4-го по 12-й схемы 95 совпадения с первых выходов схем 86- 94 управления работой устройств подается информация о том, в каком состоянии находятся устройства процессора 4. По коду команды и этим усло

5

5

0

5

0

5

0

5

виям происходит анализ разрешения ,выдачи команды на выполнение и, если нет конфликтов по доступу к каким- либо устройствам процессора 4 при выполнении ранее выданных команд и выдаваемой, вырабатывается сигнал разрешения выборки команд, В этом случае по коду команды схемы управления устанавливают информацию, которая определяет безусловное выполнение выдаваемой команды. Если при выдаче команды есть конфликты по доступу к Каким-либо устройствам при выполнении ранее выданных команд и выдаваемых на выполнение, то блокируется выдача сигнала разрешения выборки команд, что приводит к приостановке выдачи команды на выполнение, блокируется чтение команд из регистра 77 и увеличивается значения счетчика адресов команд.

Схема 86 управления порядком выработки команд передает через второй выход на пятый вход счетчика адресов команд информацию, которая определяет направление приема адреса перехода. При выполнении команд условного перехода адрес принимается с выхода регистра команд через четвертый вход, При выполнении команд безусловного перехода адрес перехода указан в блоке оперативных регистров и принимается через четвертый вход блока 13 на шестой вход счетчика 74, Управляющая информация может быть установлена в схему 86 при выдаче команды перехода на выполнение через второй вход, причем выполнение команд условного перехода определяет признак особого случая или признак нуля, установленные соответственно через третий и четвертый входы схемы 86 из блока 16 регистров или блока 15,

Схема 87 управления локальной памятью передает через второй выход в блок 17 информацию, которая определяет направление приема адреса, данных и тип (запись или чтение). Управляющая информация может быть установлена в схему 87 при загрузке директивы через второй вход с выхода схемы 82, при чтении команд в регистр 77 через третий вход с первого выхода схемы 85, при выдаче команд на рыполнение через четвертый вход с выхода дешифратора 79 команд, при обмене между блоком 17 и памятью 5 че10

15

20

171539789

ера ввода через первый вход блока 17. оследующие адреса при загрузке параетров и программы на счетчике 48 ормируются путем прибавления единицы к предыдущему адресу на счетчике. Верхняя и нижняя адресные границы принимаются на первые входы регистов 49 и 50 в процессе загрузки диективы. Управление направлением приема на регистры 49, 50 и 51 и счетчик 48, а также переключение в режим хранения для регистров 49 и 50 или в режим счета для счетчика 48 производится сигналами, поступающими из блока 13.

Сигналы, управляющие направлением приема или переключением режима рабоы, поступают на третий вход счетчиа 48, на вторые входы регистров 49 50. и на пятый вход регистра 51.

Адрес с регистра 51 подается на первый вход накопителя 58. Кроме того, выход регистра 51 адреса подключен к вторым входам схем 52 и 53 сравения, где производится сравнение 25 адреса с граничными условиями. Граничные условия с выходов регистров 49 и 50 поступают на первые входы схем сравнения 52 и 53. В случае нарушения граничных условий схемы 52 и 53 сравнения вырабатывают сигналы, которые собираются в схеме 54. С выхода схемы 54 сигнал нарушения границы поступает на второй вход накопителя 58 и блокирует обращение к операционной памяти. Одновременно этот сигнал выдается через второй выход блока локальной памяти, сообщая блоку 13 об ошибке обращения.

При записи производится установка триггера 55 записи, выход которого соединен с третьим входом накопитея 58, Помимо установки триггера 55 в блок 17 принимаются данные на регистр 56 записи. Регистр 56 имеет несколько входов. Первый вход регистра 56 соединен с выходным регистром буфера ввода и используется для записи директивы. На второй вход регистра записи принимаются данные из памяти 5, которые сначала, поступают в блок 14, а затем через шестой вход - в блок 17. На третий или четвертый входы регистра 56 принимаются данные из блока 16 регистров. Эта связь используется в командах пересылки данных из блока регистров в блок 17,

Сигналы, управляющие направление приема, поступают из блока 13 на пятый вход регистра 56.

30

35

40

45

50

55

0

5

0

789

5

0

5

0

5

0

5

18

Данные с регистра 56 поступают на четвертый вход накопителя 58, Kptf- ме того, данные с регистра 56 направляются в схему 57 дополнения до четности. Эта схема формирует контрольные разряды, которые записываются в накопитель 58 через пятый вход.

При считывании из блока 17 данные из накопителя 58 поступают через регистр 59 считывания на первый выход блока ,17. Во время выдачи данных производится их контроль по четности в схеме 60, вход которой подключен к выноду регистра 59, В случае нарушения четности схема 60 вырабатывает сигнал ошибки, который передается в блок 13.

Блок 16 оперативных регистров процессора 4 содержит (фиг,5) первый регистр 61 адреса, второй регистр 62 адреса, триггер 63 записи, регистр 64 записи, первый узел 65 оперативных регистров, второй узел 66 оперативных регистров, схему 67 анализа равенства кода нулю, первый регистр 68 выдачи и второй регистр 69 выдачи.

Число оперативных регистров в блоке равно 16. Для сокращения времени выполнения операций, вызывающих два и более операндов, в схему введены два узла оперативных регистров, хранящих одинаковую информацию. Это позволяет одновременно считать два операнда.

Выборка операндов из блока 16 ре-- гистров начинается с загрузки в регистры 61 и 62 адресов соответствующих оперативных регистров.

Информация в регистры 61 и 62 поступает из регистра команды блока 13, в котором размещаются адресные поля выполняемой команды.

После подачи адреса на вход блоков оперативных регистров на выходные регистры 68 и 69 считывается содержимое соответствующих оперативных -регистров узлов. Выходы регистров 68 и 69 подключены соответственно к первому и второму выходам блока оперативных регистров,

В случае записи блок 13 через пятый вход блока оперативных регистров устанавливает триггер 63 записи и соответствующее направление приема на регистр 64 записи.

На регистр 64 записи данн ме поступают через несколько входов. Для ко10

191539789

манд с непосредственной адресацией рый данные поступают с регистра 13 команд блока на второй вход регистра 64, На третий вход регистра 64 данные принимаются из локальной памяти процессора. При записи данных из памяти 5, которые передаются через блок 14 в блок 16 регистров, используется четвертый вход регистра 64, соединенный с вторым входом схемы оперативных регистров.

На пятый вход регистра 64 принимается сумма или разность с сумматора из блока 15. Результат логической операции принимается по шестому входу регистра 64. Результат операции сдвига принимается по седьмому входу регистра 64.

Выход триггера 63 записи соединен с вторыми входами регистров узлов 65 и 66. Выход регистра 64 подключен к третьим входам регистров узлов 65 и 66. Кроме того, содержимое регистра 64 подается в схему 67 анализа, которая в случае нулевого состояния принятой информации вырабатывает признак нуля, который подается в блок 13.

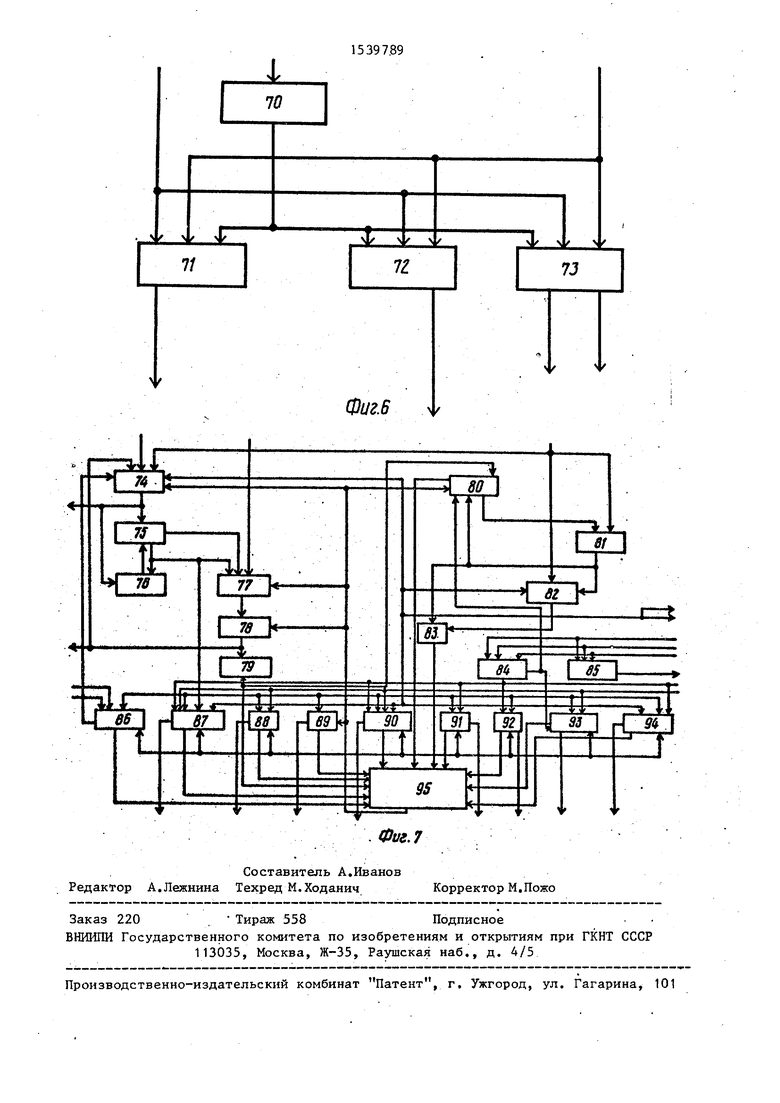

Арифметико-логический блок 15

15

20

25

20

передается в блок 13 через второй выход блока 15 и устанавливает признак особого случая.

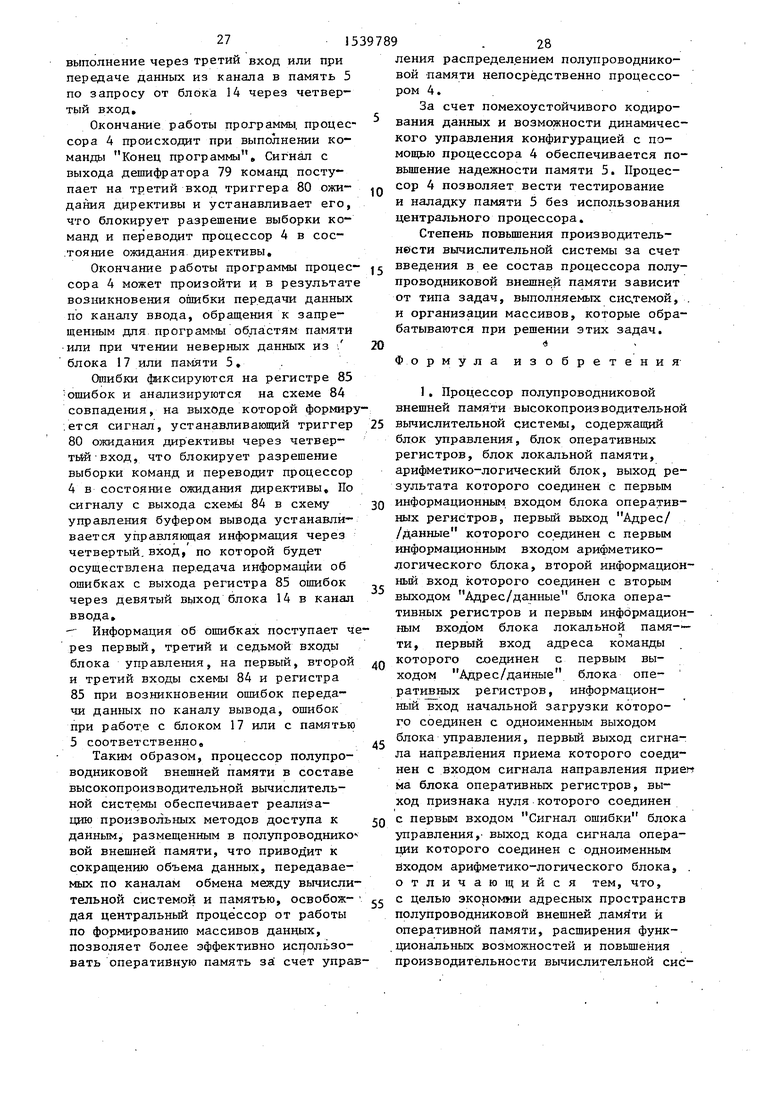

Блок 13 управления содержит (фиг.7) счетчик 74 адресов команд, схему 75 сравнения адресов, буферный регистр 76 адресов команд, буферный регистр 77 команд, регистр 78 команд, дешифратор 79 команд, триггер 80 ожидания директивы, схему 81 совпадения, схему 82 управления загрузкой директивы, триггер 83 приема директивы, схему 84 совпадения ошибок, регистр 85 ошибок, схемы управления порядком выборки команды 86, локальной памятью J57, оперативными регистрами 88,, счетчиком внешней памяти 89, счетчиком адреса локальной памяти 90, формированием адреса внешней памяти 9 1 , формированием данных внешней памяти 92, буфером вывода 93, буфером ввода 94 и схему 95 сравнения.

Блок управления предназначен для обработки командной и адресной информации и выполняет следующие функции:

управляет загрузкой директивы;

организует выборку команд;

дешифрует и выдает команды на

35

40

(фиг.6) содержит регистр 70 кода one- 30 выполнение в устройства фоцессора 4; рации, сдвигатель 71, схему 72 логической обработки и сумматор 73.

Через третий вход в блок 15 из блока 13 поступает код операции, который запоминается на регистре 70. Выход регистра 70 кода операции подключен к первым входам сдвигателя, схемы логической обработки и сумматора. Блок 15 выполняет операции над операндами, хранящимися только в оперативных регистрах. Результаты выполняемых операций записываются/также только в оперативные регистры.

Один из операндов принимается через первый вход блока 15 и поступает на вторые входы схем 71,72 и 73, Второй операнд принимается через второй вход блока 15 и поступает в схемы 71, 72 и 73 через третий вход. Операнды на первый и второй входы поступают одновременно.

Результаты сдвига, логической обработки, сложения или вычитания с первых выходов схем 71, 72 и 73 соответственно передаются через первый выход блока 15, В случае переполнения разрядной- сетки схемы 73 вырабатывается сигнал переполнения, кото45

50

55

устанавливает режим работы процессора 4;

обрабатывает ошибки.

В начале работы блок 13 находится в состоянии ожидания директивы, т.е. установлен триггер 80 ожидания директивы, с первого выхода которого на первый вход схему 95 сравнения поступает сигнал, который блокирует выдачу сигнала разрешения выборки команд с выхода схемы 95, Сигнал разрешения выборки команд является сигналом разрешения выборки из локальной памяти команд и чтения из регистра 77, разрешения дешифрации и выдачи команд на выполнение в функциональных устрой ствах процессора 4.

Сигнал разрешения выборки команд поступает на первые входы всех схем управления 86-94 и разрешает прием управляющей информации с выхода дешифратора 79 команд в эти схемы. Этот же сигнал подается на первые входы счетчика 74 команд и регистра 77, регистра 78 команд и триггера 80 ожидания директивы и разрешает выборку команд из блока 17 в регистр 77, дешифрацию и обработку команд, а также

0

789

рый

5

0

5

20

передается в блок 13 через второй выход блока 15 и устанавливает признак особого случая.

Блок 13 управления содержит (фиг.7) счетчик 74 адресов команд, схему 75 сравнения адресов, буферный регистр 76 адресов команд, буферный регистр 77 команд, регистр 78 команд, дешифратор 79 команд, триггер 80 ожидания директивы, схему 81 совпадения, схему 82 управления загрузкой директивы, триггер 83 приема директивы, схему 84 совпадения ошибок, регистр 85 ошибок, схемы управления порядком выборки команды 86, локальной памятью J57, оперативными регистрами 88,, счетчиком внешней памяти 89, счетчиком адреса локальной памяти 90, формированием адреса внешней памяти 9 1 , формированием данных внешней памяти 92, буфером вывода 93, буфером ввода 94 и схему 95 сравнения.

Блок управления предназначен для обработки командной и адресной информации и выполняет следующие функции:

управляет загрузкой директивы;

организует выборку команд;

дешифрует и выдает команды на

выполнение в устройства фоцессора 4;

устанавливает режим работы процессора 4;

обрабатывает ошибки.

В начале работы блок 13 находится в состоянии ожидания директивы, т.е. установлен триггер 80 ожидания директивы, с первого выхода которого на первый вход схему 95 сравнения поступает сигнал, который блокирует выдачу сигнала разрешения выборки команд с выхода схемы 95, Сигнал разрешения выборки команд является сигналом разрешения выборки из локальной памяти команд и чтения из регистра 77, разрешения дешифрации и выдачи команд на выполнение в функциональных устройствах процессора 4.

Сигнал разрешения выборки команд поступает на первые входы всех схем управления 86-94 и разрешает прием управляющей информации с выхода дешифратора 79 команд в эти схемы. Этот же сигнал подается на первые входы счетчика 74 команд и регистра 77, регистра 78 команд и триггера 80 ожидания директивы и разрешает выборку команд из блока 17 в регистр 77, дешифрацию и обработку команд, а также

2515

рез пятый и шестой входы, при записи и чтении данных из блока 17.соответственно и при обмене с памятью 5, по адресам, хранящимся в блоке 17, через шестой вход схемы 87. Запросы от блока 14 поступают на пятый и шестой входы через седьмой вход блока 17.

Схема управления оперативными регистрами 88 передает через второй выход в блок 16 регистров информацию которая определяет направление приема адреса операнда и типа обращения (запись или чтение). Управляющая информация может быть установлена в схе му 88 при, выдаче команды на выполнение через- второй вхрд или при записи операндов, считанных из памяти 5 по сигналу от блока 14, который подается на третий вход схемы 88 через седьмой вход блока 13.

Схема управления счетчиком 89 внешней памяти пе редает через второй выход в блок 14 сигнал установки режима работы счетчика объема обмена, по которому на счетчик из.блока 16 регистров принимается количество данных обмена, по этому же сигналу устанавливается код операции обмена в блоке 14, Управляющая информация устанавливается в схему 89 только при выдаче команд обмена на выполнение через второй вход.

Схема 90 управления счетчиком адреса локальной памяти передает через второй выход в блок 17 управляющую информацию, которая определяет режим работы счетчика адреса локальной па мяти; параллельный прием, счет или хранение, при выполнении загрузки директивы или команд обмена.

Управляющая информация в схему 90 может быть установлена при загрузке директивы через второй вход с первог выхода схемы 82, при выдаче команды на выполнение через третий вход, при выполнении команд обмена блока 17 и памяти 5 и при обмене с памятью 5, по адресам хранящимся в блоке 17.

Запросы на блок 14 на изменение значения счетчика поступают в схему 90 при записи из памяти 5 через четвертый вход или при чтении из блока 17 через пятый вход.

Схема 91 управления формированием адреса внешней памяти передает через второй выход в блок 14 управляющую информацию, которая определяет направление приема начального адреса и

0

0

5

789

с

0

5

0

5

0

5

26

адресного смещения при выполнении операции обмена, в которых адреса фо р- мируются в блоке 14, При выполнении обмена по косвенным адресам управляющая- информация указывает, что адрес внешней памяти необходимо принять из блока 17, Управляющая информация в схему 91 может быть установлена через второй вход при выдаче команды обмена на выполнение или при выполнении команд обмена по косвенным адресам по запросу блока 14 на третий вход схемы 91.

,Схема 92 управления формированием данных внешней памяти передает через второй выход в блок 14 управляющую информацию, которая определяет направление приема данных для записи в память 5 из канала, из блока 17 или. из блока регистров. Управляющая информация в схему 92 может быть установлена через второй вход при выдаче команд на выполнение или при выполнении команд обмена с каналом ввода или блоком 17 по запросу блока 14 через седьмой вход блока 13 на третий вход схемы 92,

Схема 93 управления буфером вывода передает через второй выход на входы управления регистров буфера вывода управляющую информацию, которая определяет порядок и направление приема на регистры 18 и 21, считанную иэ памяти 5 из блока регистров 16, или информацию об ошибках, передаваемую в канал вывода. Управляющая информация в схему 93 может быть установлена при выдаче команд на выполнение через второй вход по запросу блока 14, через третий вход при чтении данных из памяти 5 в канал или при возникновении ошибки по запросу схемы 84 совпадения ошибок на четвертый вход схемы 93.

Схема 94 управления буфером ввода передает через второй выход на входы управления регистров буфера ввода управляющую информацию, которая определяет порядок передачи данных че- . рез регистры 8 и 12, поступивших из канала и записываемых в память 5 или в блок 17 и специальные регистры, входящие в состав устройств процессора 4 при загрузке директивы. Управляющая информация в схему 94 может быть установлена при загрузке дирек- тивы через второй вход с первого выхода схемы 82 при выдаче команд на

I

выполнение через третий вход или при передаче данных из канала в память 5 по запросу от блока 14 через четвертый вход.

Окончание работы программы, процессора 4 происходит при выполнении команды Конец программы. Сигнал с выхода дешифратора 79 команд поступает на третий вход триггера 80 ожидания директивы и устанавливает его, что блокирует разрешение выборки команд и переводит процессор 4 в состояние ожидания директивы.

Окончание работы программы процессора 4 может произойти и в результат возникновения ошибки передачи данных по каналу ввода, обращения к запрещенным для программы областям памяти или при чтении неверных данных из блока 17 или памяти 5.

Ошибки фиксируются на регистре 85 ошибок и анализируются на схеме 84 совпадения, на выходе которой формирется сигнал, устанавливающий триггер 80 ожидания директивы через четвертый вход, что блокирует разрешение выборки команд и переводит процессор

4в состояние ожидания директивы. По сигналу с выхода схемы 84 в схему управления буфером вывода устанавливается управляющая информация через четвертый.вход, по которой будет осуществлена передача информации об ошибках с выхода регистра 85 ошибок через девятый выход блока 14 в канал ввода.

- Информация об ошибках поступает чрез первый, третий и седьмой входы блока управления, на первый, второй и третий входы схемы 84 и регистра 85 при возникновении ошибок передачи данных по каналу вывода, ошибок при работе с блоком 17 или с памятью

5соответственное

Таким образом, процессор полупроводниковой внешней памяти в составе высокопроизводительной вычислительной системы обеспечивает реализацию произвольных методов доступа к данным, размещенным в полупроводнике вой внешней памяти, что приводит к сокращению объема данных, передаваемых по каналам обмена между вычислительной системой и памятью, освобож- дая центральный процессор от работы по формированию массивов данных, позволяет более эффективно использовать оперативную память за счет упра

5

ления распределением полупроводниковой памяти непосредственно процессором 4.

За счет помехоустойчивого кодирования данных и возможности динамического управления конфигурацией с помощью процессора 4 обеспечивается повышение надежности памяти 5. Процессор 4 позволяет вести тестирование и наладку памяти 5 без использования центрального процессора.

Степень повышения производитель- нести вычислительной системы за счет введения в ее состав процессора полупроводниковой внешней памяти зависит от типа задач, выполняемых системой, и организации массивов, которые обрабатываются при решении этих задач.

4

Формула изобретения

5

0

5

5 вычислительной системы, содержащий блок управления, блок оперативных регистров, блок локальной памяти, арифметико-логический блок, выход результата которого соединен с первым

0 информационным входом блока оперативных регистров, первый выход Адрес/ /данные которого соединен с первым информационным входом арифметико- логического блока, второй информационный вход которого соединен с вторым выходом Адрес/данные блока оперативных регистров и первым информационным входом блока локальной памяти, первый вход адреса команды которого соединен с первым выходом Адрес/данные блока оперативных регистров, информационный вход начальной загрузки которого соединен с одноименным выходом блока управления, первый выход сигнала направления приема которого соединен с входом сигнала направления приеп ма блока оперативных регистров, выход признака нуля которого соединен

Q с первым входом Сигнал ошибки блока управления, выход кода сигнала операции которого соединен с одноименным входом арифметико-логического блока, . отличающийся тем, что,

5 с целью экономии адресных пространств полупроводниковой внешней дамя ти и оперативной памяти, расширения функциональных возможностей и повышения производительности вычислительной сие29

темы за счет реализации произвольных алгоритмов доступа к данным и их предварительной обработки, в него введены приемный буферный регистр ввода, первый и второй буферные регистры ввода, передающий буферный регистр ввода, схема контроля четности, блок управления внешней памятью, схема дополнения до четности, приемный буферный регистр вывода, первый и второй буферные регистры вывода и передающий буферный регистр вывода, причем информационный вход приемного буферного регистра ввода соединен с информационным входом процессора, выход данных приемного буферного регистра ввода соединен с информационными входами первого и второго буферных регистров ввода и схемы контроля четности, вы- ходы данных первого и второго буферных регистров ввода соединены с первым и вторым информационными входа ми передающего буферного регистра ввода, вход управления которого соединен с одноименным входом приемного буферного регистра ввода и выходом сигнала Запись/чтение блока управления, выход Нарушение четности схемы контроля четности соединен с вторым входом Сигнал ошибки блока управления, выход данных передающего буферного регистра ввода соединен с информационным входом начальной загрузки .блока управления внешней памятью, входом загрузки директивы блока управления и входом начальной установки блока локальной памяти, информационный выход которого соединен с вторым инфор45

мационным входом блока оперативных никовой внешней памяти, вход данных гистров, первым информационным входом блока управления внешней памятью и входом загрузки команды блока управления, выход команды которого соединен с входом кода команды блока локальной памяти, второй вход адреса команды которого соединен с одноименным выходом блока управления, выход Управление режимом которого соединен с одноименным входом блока локальной памяти, выход сигнала ошибки которого соединен с третьим входом Сигнал ошибки блока управления, четвертый вход Сигнал ошибки которого соединен с выходом переполнения арифметико-логического блока, первый выход данных блока оперативных регистров i соединен с: входом Начальный адрес

50

55

которого является входом блока управ ления внешней памятью, второй информационный вход которого соединен с вторым выходом данных блока оператив ных регистров,

ней памятью, входом Адрес перехода блока управления и первым информационным входом приемного буферного регистра вывода, второй информационный вход которого соединен с вторым информационным входом блока локальной памяти, третьим информационным входом блока оперативных регистров и выходом данных блока управления внешней памятью, выход Сигнал запроса которого соединен с одноименным входом блока управления, выход Разрешение записи/чтения которого соеди- 15 ней- с одноименными входами Запись/

10

/чтение приемного буферного регистра вывода и передающего буферного регистра вывода, вход данных которого является информационным выходом про20 цессора и соединен с входом схемы, дополнения до четности, выход которой является выходом контрольного разряда процессора, первый и второй информационные входы передающего бу25 ферного регистра вывода соединены с выходами данных первого и второго буферных регистров вывода соответственно, информационные входы которых соединены с выходом данных приемного буЗо ферного регистра вывода, третий информационный вход которого соединен с выходом Конец программы блока

Сигнал на35

управления, второй выход правления приема которого соединен с входом управляющей директивы блока управления внешней памятью, выходы данных, адреса и управления внешней памятью которого являются одноименными выходами процессора полупровод

никовой внешней памяти, вход данных

которого является входом блока управления внешней памятью, второй информационный вход которого соединен с вторым выходом данных блока оперативных регистров,

15

20

25

гистр записи данных, схему совпадения, схему сравнения, регистр незанятости кубов, триггер записи, схему кодирования, с первого по шестнадцатый счетчики управления кубами, с первого по шестнадцатый регистры направления приема информации, мультиплексор, схему декодирования и регистр передачи информации, ю при этом первый информационный вход ч блока управления внешней памятью соединен с первыми информационными входами регистра подготовки данных и регистра текущего адреса, вход начального адреса и приращения блока управления внешней памятью соединен с вторыми информационными входами регистра подготовки данных и регистра текущего адреса и информационным входом регистра приращения адреса, второй информационный вход блока управления внешней памятью соединен с третьим информационным входом регистра подготовки данных и параллельным информационным входом счетчика объема обмена, информационный вход начальной загрузки блока управления внешней памятью соединен с четвертым информационным входом регистра подго- 30 товки данных и информационными входа - ми регистров нижней и верхней границ адреса, вход управляющей директивы блока управления внешней памятью соединен с входами Разрешение приема 35 регистра подготовки данных, триггера готовности данных, регистра приращения адреса, регистра текущего адреса, триггера готовности адреса, счетчика объема обмена, регистров нижней и 40 верхней границ адреса, регистра кода операции, выход данных регистра подготовки данных через схему кодирования соединен с информационным входом регистра записи данных, выход данных 45 которого является выходом данных на внешнюю память блока управления внешней памятью, вход разрешения приема регистра записи данных соединен с выходом сигнала Разрешение внешней 50 памяти схемы совпадения, с входами Разрешение приема регистра адреса, триггера записи, регистра текущего адреса, с входами сброса регистров незанятости кубов, направления прие- 55 ма информации,, триггеров готовности данных и адреса, входом разрешения счета счетчика управления кубами и вхрдом вычитания счетчика объема

обмена, первый выход которого соединен с первым входом схемы совпадения, второй и третий входы которой соединены с выходом триггера готовности адреса и выходом триггера готовности данных соответственно, четвертый и пятый входы схемы совпадения соединены соответственно с выходами сигнала несовпадения схем сравнения адреса с нижней и верхней границами, шестой вход схемы совпадения соединен с выходом Отсутствие конфликтов схемы сравнения, первый информационный вход которой соединен с младшими разрядами адреса выхода данных регистра текущего адреса, второй информационный вход схемы сравнения соединен с выходом данных регистра незанятости кубов, первый информационный вход которого соединен с одноименными входом мультиплексора и выходом данных счетчика управления кубами, вход параллельных данных которого соединен с вторым информационным входом регистра незанятости кубов, первым информационным входом регистра направления приема информации и первым выходом адреса регистра текущего адреса,1 второй выход адреса которого соединен с входом первого слагаемого .сумматора адреса, первыми информационными входами схем сравнения адреса с нижней и верхней границами и информационным входом адреса регистра адреса, выход которого является выходом адреса на внешнюю память блока управления внешней памятью, вход второго слагаемого сумматора адреса соединен с выходом адреса регистра приращения адреса, выход сумматора адреса соединен с третьим информационным входом регистра текущего адре са, второй выход счетчика объема обмела соединен с входами разблокировки приема триггера готовности адреса и регистра кода операции, выход данных которого соединен с информационным входом триггера записи, блокировки приема триггера готовности адреса и вторым информационным входом регистра направления приема информации, выход данных которого соединен с вторым информационным входом мультиплексора, выход данных которого и выходы триггера записи и счетчика управления кубами являются выходом сигнала управления на внешнюю память блока управления внешней

памятью, вход информации с внешней памяти которого соединен с входом схемы декодирования, выход данных которой через регистр передачи инфор- мации соединен с выходом данных блока управления внешней памятью, выход ошибки схемы декодирования вместе с выходом триггера ошибки обмена и схемы совпадения яйляются выходом сигнала запроса блока управления внешней памятью, первый и второй входы установки триггера ошибки обмена соединены с выходами сигнала сравнения схем сравнения адреса с нижней и верхней границами соответственно, вторые ин формационные входы которых соединены с выходами данных регистров нижней границы и верхней границы адреса соответственно.

3 Процессор по п.1, отличающийся тем, что блок локальной памяти содержит счетчик адреса памяти, регистр верхней границы, регистр нижней границы, регистр адреса локальной памяти, схему сравнения адреса с верхней границей, схему сравнения адреса с нижней границей, схему сборки сигналов нарушения границ, триггер записи, регистр записи, схему дополнения до четности, накопитель, регистр чтения и схему контроля четности, при этом вход кода команды блока локальной памяти соединен с входом установки режима регистра адреса локальной памяти, первый информационный вход которого соединен с вторым входом адреса команды блока локальной памяти, первый вход адреса команды которого соединен с вторым информационным входом регистра адреса локальной памяти и первыми информационными входами счетчика адреса памяти и регистра записи, вторые информационные входы которых соединены с входом начальной установки блока локальной памяти и первыми информационными входами ре гистров верхней и нижней границ, входы записи которых соединены с входом управления режимом блока локальной памяти, входами записи счетчика адреса памяти и регистра адреса локальной памяти, входом установки триггера записи и входом режима регистра записи, третий и четвертый информационные входы которого соединены с первым и вторым информационными входами соответственно блока локальной памяти, выход данных

регистра записи соединен с информационным входом накопителя и входом схемы дополнения до четности, выход контрольных разрядов которой соединен

с одноименным входом накопителя, адресный вход которого соединен с выходом адреса регистра адреса локальной памяти и первыми информационными входами схем сравнения адреса с верхней и нижней границами, вторые информационные входы которых соединены с выходами данных регистров верхней и нижней границ, выходы сигналов нарушения границ схем сравнения адреса с верхней и нижней границами соединены с первым и вторым входами соответственно схемы сборки сигналов нарушения границ, выход которой соединен с вхо0 Д°м блокировки обращения накопителя и является выходом сигнала ошибки блока локальной памяти, прямой выход триггера записи соединен с входом записи накопителя, выход данных которо-

5 го соединен с информационным входом регистра чтения, выход данных которого соединен с входом схемы контроля четности и является информационным выходом блока локальной памяти, с вы0 ходом сигнала ошибки которой соединен выход схемы контроля четности.

5 регистра записи, второй и третий информационные входы которого соединены соответственно с. вторым и третьим информационными входами блока оперативных регистров, вход управления

0 направлением приема которого соединен с входом установки триггера записи и входом установки режима регистра записи, первый, второй и третий информационные входы которого соеди5 нены с первым информационным входом блока оперативных регистров, выход данных первого регистра адреса соединен с первым информационным входом первого узла оперативных регистров

второй информационный вход которого соединен с выходом данных регистра записи, входом схемы анализа равенства кода нулю и первым информационным входом второго узла оперативных регистров, второй информационный вход которого соединен с выходом данных второго регистра адреса, входы записи первого и второго узлов оперативных регистров соединены с прямым выходом триггера записи, выходы данных первого и второго узлов оперативных регистров соединены с информационными входами первого и второго регистров выдачи соответственно, выходы данных которых соединены с первым и вторым выходами адреса данных соответственно блока оперативных регистров, выход признака нуля которого соединен с выходом схемы анализа равенства кода нулю.

5о Процессор по п.1, отличающийся тем, -что арифметико-лог гический блок содержит регистр кода операции, сдвигатель, схему логической обработки и сумматор, при этом первый информационный вход арифметико-логического блока соединен с первыми информационными входами сум- матора, схемы логической обработки и сдвигателя, первый выход данных которого соединен с выходом результата арифметико-логического блока, вход сигнала Код операции которого соединен с информационным входом регистра кода операции, выход управляющих данных которого соединен с входами управления сдвигателя, сумматора и схемы логической обработки, выход результата которой соединен с выходом результата арифметико-логического блока, второй информационный вход которого соединен с вторыми информационными входами сдвигателя, схемы логической обработки и сумматора, выход данных и выход признака переполнения которого соединены соответственно с выходом сигнала пере - полнения арифметико-логического блока.

5

0

5

ния, схему управления загрузкой директивы, триггер приема директивы, схему совпадения ошибок, регистр ошибок, схему управления порядком выборки команд, схему управления локальной памятью., схему управления оперативными регистрами, схему управления счетчиком внешней памяти, схему управления счетчиком адреса локальной памяти, схемы управления формированием адреса и данных внешней памяти, схему управления буфером вывода, схему управления буфером ввода и схему сравнения, при этом вход загрузки директивы блока управления соединен с первыми информационными входами счетчика адресов команд, схемы совпаде- . ния и схемы управления загрузкой директивы, вход адреса перехода ко- .i торой соединен с вторым информационным входом счетчика адресов команд, вход сигнала Направление приема которого соединен с выходом данных регистра команд, входом дешифратора команд и является информационным выходом блока управления, вход загрузки команды которого соединен с информа- Q ционным входом буферного регистра команд, вход сигнала вывода буферного регистра команд соединен с выходом сигнала совпадения схемы сравнения адресов, первый вход которой соединен с выходом данных счетчика адресов команд, входом буферного регистра адресов команд и является выходом адреса команд блока управления, выход данных буферного регистра адресов команд соединен с вторым входом схемы сравнения адресов, выход сигнала несовпадения которой соединен с входами записи буферного регистра адресов команд, схемы управления локальной памятью и буферного регистра команд, выход данных которого соединен с информационным входом регистра команд, вход разре- шения приема которого соединен с выходом управляющего сигнала схемы сравнения и входами разрешения приема буферного регистра команд, схемы управления счетчиком внешней памяти, . схемы управления порядком выборки команд, схемы .управления локальной памятью, схем управления оперативными регистрами, счетчиком адреса локальной памяти, формированием адреса внешней памяти, буферами вывода

5

0

5

0

5

и ввода,входом разрешения чтения счетчика адресов команд и первым входом установки триггера ожидания директивы, второй вход установки которого соединен с выходом дешифратора команд и входами загрузки команд схемы сравнения и всех схем управления, третий вход установки триггера ожидания директивы соединен с выходом схемы совпадения ошибок и входом блокировки схемы управления буфером вывода, вход данных которой соединен с входом сигнала запроса блока управления, выход управления схемы управления буфером вывода является выходом сигнала Запись/чтение блока управления, первый, второй и третий входы ошибок схемы совпадения ошибок соединены с вторым и третьим входами сигнала ошибки и входом сигнала запроса соответственно блока управления и одноименными входами регистра ошибок, выход которого соединен с выходом сигнала Конец работы блока управления, первый и второй входы блокировки схемы сравнения соединены соответственно с прямыми выходами триггеров ожидания директивы и приема директивы, вход установки триггера приема директивы соединен с входом сброса триггера ожидания директивы, входом разрешения загрузки схемы управления загрузкой директивы и выходом схемы совпадений, второй вход которой соединен с обратным выходом триггера ожидания директивы, выход сигнала окончания загрузки схемы управления загрузкой директивы соединен с входом сброса триггера приема директивы, выход сигнала загрузки схемы управления загрузкой директивы соединен с входами разрешения приема счетчика

0

5

0

5

0

5

0

адресов команд и схем управления локальной памятью, счетчиком адреса локальной памяти и буфером ввода и ляется выходами сигнала направления приема и управления режимом блока управления, входы сигнала запроса блока управления соединены с одноименными входами схем управления ло- калькой памятью,операционными регистрами, счетчиком адреса локальной памяти,формированием адреса внешней памяти,формированием данных внешней памяти и буфером ввода,выход управляющих данных которого является выходом сигнала Запись/чтения блока управления, выходы управляющих данных схем управления счетчиком внешней памяти формированием адреса и данных внешней памяти образуют второй выход сигнала направления приема блока управления, выход управляющих данных схемы управления операционными регистрами является первым выходом сигнала напраьления приема блока управления, выходы управляющих данных схем управ ления счетчиком адреса локальной памяти и локальной памятью являются выходом управления режимом блока управления , первый и второй входы управляющей информации схемы управления порядком выборки команд соединены соответственно с первым и четвертым входами сигналов ошибки блока управления, с первого по девятьй входы информации состояния схемы сравнения соединены соответственно с одноименными выходами схем управления порядком выборки команд, локальной памятью, оперативными регистрами, счетчиком внешней памяти, формированием адреса и данных внешней памяти, буферами вывода и ввода.

Фай

Фаг. 5

71

Фиг.В

f f

и

73

г

| Патент США № 4128880, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Пневмогидравлическая посадочная стойка для крепления очистных выработок | 1959 |

|

SU123509A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Колосниковая решетка с чередующимися неподвижными и движущимися возвратно-поступательно колосниками | 1917 |

|

SU1984A1 |

| Устройство для кодирования 64-разрядных информационных слов в составной корректирующий код с расстоянием шесть | 1982 |

|

SU1132292A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для декодирования составного корректирующего кода | 1983 |

|

SU1229969A1 |

| Ramamorty C.V | |||

| , Li H.F., Pipeline Architecture Computing Surveyz, 1977, vol | |||

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

| Мнчев А.А | |||

| Организация управляющих вычислительных комплексов | |||

| M.I Энергия, 1980, с.45-49, рис.2-4. | |||

Авторы

Даты

1990-01-30—Публикация

1987-01-14—Подача