Предлагаемое устройство относится к цифровым вычислительным машинам с мультипрограммной структурой и, в частности, к устройствам центрального управления, которые осуществляют подготовку команд к выполнению их соответствуюидими исполнительными устройствами.

Известно устройство выборки команд, содержащее буфер команд из 8 адресуемых регистров, два дополнительных адресуемых регистра, которые используются при обработке команд перехода, три регистра со схемами приращения, управляющие выборкой команд из памяти и помещением их в буфер команд, регистр команд, в который команды подаются для декодирования из буфера команд, а в некоторых случаях и непосредственно из памяти с помощью соответствующих схем управления одновременно с записью их в буфер команд, схемы быстрой и точной проверки для обнаружения операции запоминания, ока-, зывающей влияние на содерл имое буфера команд, схемы, осуществляющие выборку из памяти и замену измененных в результате операции запоминания команд, содержащихся в буфере команд.

Предлагаемое устройство отличается от известного тем, что команды для декодирования подаются непосредственно из буфера команд и что информация для замены измененных в

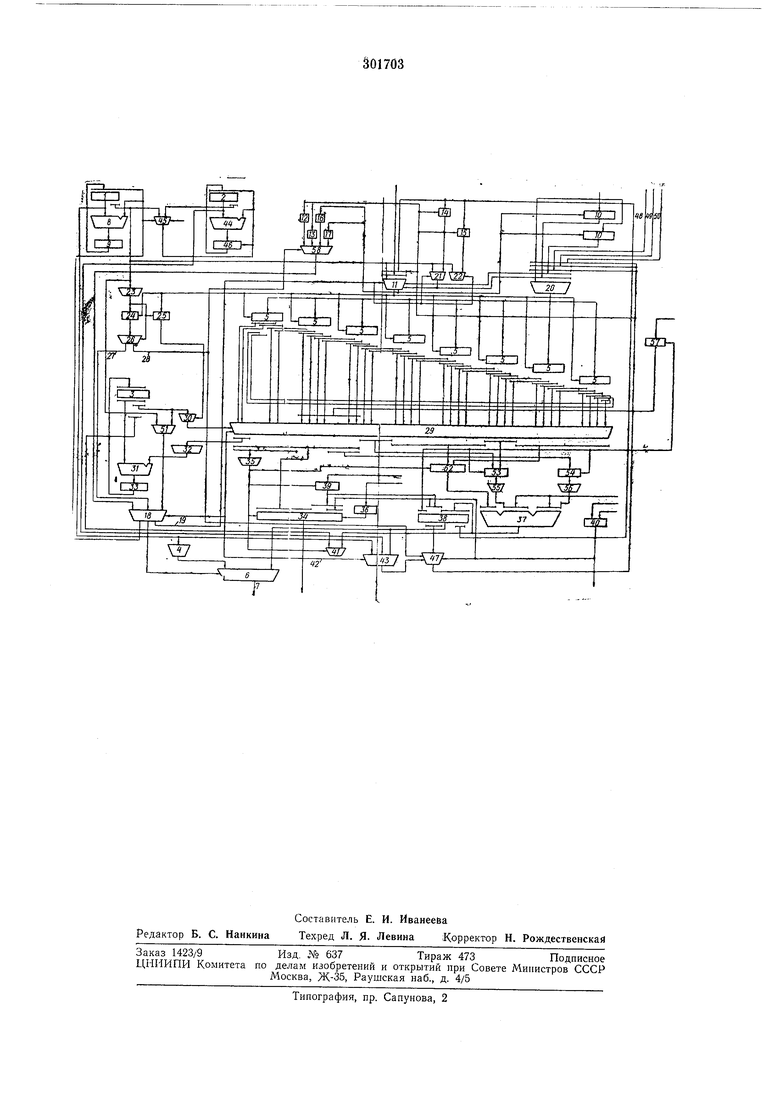

результате операции запоминания команд, содержащихся в буфере команд, подается непосредственно с регистров результата арифметического устройства. Это позволяет упростить структуру и сократить оборудование устройства центрального управления, сократить перерывы в работе цифровой вычислительной машины, вызванные командами запоминания, и, соответственно, повысить производительность. На чертеже представлена структурная схема предлагаемого устройства.

Команды из памяти выбираются 64-разрядными словами.

Адрес первого слова команд помещается в регистры 1 и 2, адрес первой команды - в регистр 5. С выхода регистра / адрес подается на схему 4 формирования запроса, где к адресу слова команд добавляется признак чтения, адрес регистра-приемника, три младших разряда которого совпадают с тремя младшими

разрядами адреса слова-указывают на номер регистра 5 буфера команд, в который нужно поместить выбранное из памяти слово команд. Со схемы 4 запрос на выборку слова команд через коммутатор 6 адресной шины равления оперативной памятью. На суммато ре 5 к адресу первого слова команд добавляется единица и результат - адрес второго слова команд - запоминается в промежуточном регистре 9, выход которого по окончании передачи запроса на первое слово команд подключается ко входу регистра 1, куда занисывается адрес второго слова команд. Передается запрос на выборку второго слова команд, после чего в регистре / устанавливается адрес третьего слова команд, и т. д. до тех нор, пока не возникнет одно из трех условий: 1)переданы занросы на пять слов команд; если переданы запросы на четыре слова, то передается дополнительно запрос еще на одно слово команд, если при этом не задерживается передача запроса на операнд; 2)устанавливается условный режим в результате обработки команды «Условный переход;3)обнаруживается неоднородность, т. е. нарушается процесс выборки в результате операций перехода, прерывания или запоминания. Выбранные из памяти слова команд запоминаются в восьми регистрах 5 буфера команд или, в некоторых случаях, в регистрах 10 дополнительного буфера. Дополнительный буфер используется при обработке команд перехода. В него записываются два первых слова команд новой последовательности, обработка которой начнется, если переход будет успешным. Этот буфер обеспечивает начало работы в случае успешных переходов, ускоряя работу вычислительной машины, и сохраняет содержимое восьми регистров буфера команд на тот случай, если перехода фактически не будет. Запрос на выборку команд в дополнительный буфер формируется как запрос на операнды. На номер регистра буфера команд указывают три младших разряда адреса слова. Этот трехразрядный указатель номера регистра помещается в разряды адреса регистра-приемника при формировании запроса к памяти на команды, а при передаче слов команд из памяти адрес регистра-приемника сопровождает эти передачи. Дешифратор // адреса регистра-приемника открывает входные клапаны регистра буфера команд с номером, соответствующим трехразрядному указателю. Одновременно с передачей запросов в память на выборку команд в дополнительный буфер триггеры 12 и 13 занятости регистров этого буфера по запросу переводятся в состояние занятости. При этом в регистрах 14 и 15 запоминаются три младших разряда адреса слов, на выборку которых в регистры дополнительного буфера передается запрос. Исполнение запросов отмечается триггерами 16 и 17. равления адресной шиной при этом формируется сигнал «Выборка пропускается по шине 19, по которому через коммутирующую схему 20 записи непосредственно с регистров результата с помощью схем 21 и 22 сравнения и дешифратора // адреса регистра-приемника слова команд из регистров 10 дополнительного буфера переписываются в регистры буфера команд с номерами, соответствующими трем разрядам, записанным в регистрах 14 и 15 соответственно. Все запросы на выборку в буфер команд с помощью дещифратора 23 номера регистра буфера команд отмечаются на регистре 24 занятости буфера команд по запросу, а исполнение запросов с помощью дешифраторов // и 23 фиксируется регистром 25. Схемой 26 формируется сигнал по шине 27 «Буфер команд доступен и сигнал по шине 28 «Буфер команд свободен. Первый говорит о доступности регистра буфера команд, в который формируется запрос на выборку слова команд. Если был передан запрос на выборку слова команд в какой-либо регистр буфера команд, но слово по этому за-Просу еще не поступило из памяти, то этот регистр недоступен для последующих выборок до тех пор, пока первый запрос не будет исполнен. Сигнал «Буфер команд свободен говорит о доступности всех восьми регистров буфера команд. Первые 16 разрядов декодируемой команды и следующие 32 разряда из регистров буфера команд направляются на декодирование через коммутирующую схему 29 с помощью дешифратора 30. К адресу декодируемой команды, записанному в регистре 3, на сумматоре 31 добавляется длина команды через преобразователь 32 длины команды, а результат - адрес следующей команды - запоминается промежуточным регистром 33. При переходе к декодированию следующей команды выход регистра 33 подключается ко входу регистра 3, и в нем устанавливается адрес следующей команды. С номощью дешифратора 30 из регистров буфера команд подключаются первые 16 разрядов этой команды и следующие 32 разряда на декодирование и т. д. С регистра 34 под управлением дешифратоа 35 кода операции и счетчика 36 занятости агазина операций арифметического устройтва команда передается в магазин операций того устройства. К содержимому счетчика 36 ри этом добавляется единица. Сумматором 37 адреса формируется адрес перанда, в регистре 38 по этому адресу форируется запрос на операнд с помощью счетика 39 занятости буфера аргументов, счетчиа 40 занятости регистров результата и деифратора кода операции. Запрос на операнд ерез коммутатор адресной шины передается устройство управления оперативной паЕсли сформирован запрос на запись, то схема 41 быстрой проверки определяет предварительно, влияет ли операция запоминания на содержимое буфера команд. В случае определения такого влияния блокируется выборка команд и декодирование (сигнал по шине 42 «блокировка), включается схема 43 точной проверки, которая сравнивает адрес ячейки памяти, в которую будет производиться запоминание, с адресами в регистрах 1 и 2. Регистром 2 отмечается адрес первого слова команд, помещенного в буфер команд. Когда в результате увеличения адреса в регистре 1 происходит совпадение трех младших разрядов слов (разряды 19-21) в этОм регистре с тремя младшими разрядами слов (,разряды 19-21) в регистре 2, при передаче запроса единица добавляется не только к адресу в регистре /, но и к адресу в регистре 2. До бавление единицы к адресу в регистре 2 производится на сумматоре 44 с помощью схемы 45 сравнения, а результат запоминается в промежуточном регистре 46. По окончании передачи запроса выход регистра 46 подключается ко входу регистра 2. Совпадение трех младших разрядов адреса слова в регистрах 1 и 2 указывает на то, что буфер команд заполнён и при последующих выборках происходит не заполнение буфера команд, а замена слов команд, находящихся в этом буфере, начиная с первого помещенного туда слова. В установившемся режиме такое положение сохраняется постоянно. Блокировка выборки команд и декодирования снимается, если результат точной проверки указывает на то, что запоминание не влияет на содержимое буфера команд. Если же адрес ячейки памяти, в которую произведено запоминание, совпадает с адресом какого-либо слова команд, уже находящихся в буфере команд, то блокировка не снимается до тех пор, пока это слово в буфере команд не будет заменено на новое. Как только на счетчике 40 занятости регистров результата отметится, что информация для запоминания поступила в регистр результата, под управлением дешифратора 47 и дешифратора 11 адреса регистра-приемника информация через схему 20 с соответствующего регистра результата по щинам 48, 49 или 50 поступает в соответствующий регистр буфера команд. Блокировка выборки команд и дещифрацни после того снимается. Схема 51 сравнения определяет, на сколько слов адрес в регистре / больше адреса в регистре 3 адреса декодируемой комапды. На регистре 52 запоминается смещение, на регистре 53 - адрес регистра сверхоперативного запоминающего устройства, в котором находится базовый адрес, и в регистре 54 запоминается адрес регистра сверхоперативного запоминающего устройства, в котором находится индекс. При формировании адреса операнда смещение с регистра 52, база и индекс из сверхоперативного запоминающего устройства под управлением дещифраторов 55 и 56 подаются На сумматор адреса. В регистре 57 запоминается информация для модификации команды. 58 - счетчик занятости регистров результата. Предмет изобретения Устройство для выборки команд, содержащее регистры буфера команд и дополнительного буфера, регистры и схемы управления выборкой команд из памяти и помещения их в регистры буфера команд и дополнительного буфера, регистр модификации адреса, отличающееся тем, что, с целью сокращения оборудования и повыщения быстродействия, оно содержит коммутирующую схему передачи команд на декодирование, схему быстрой предварительной проверки и схему точной проверки совпадения адресов ячеек памяти, схему записи непосредственно с регистров результата в регистры буфера команд, причем входы коммутирующей схемы передачи команд связаны с выходами регистров буфера команд, а выходы коммутирующей схемы передачи команд через дещифратор кода операций и регистр модификации адреса подключены ко входам схемы быстрой проверки, выход которой подключен ко входу схемы точной проверки, выход которой соединен со входом дешифратора, другой вход которого подключен к выходу счетчика занятости регистров результата, а выход которого подключен к схеме записи команд в буфер команд непосредственно с регистров результата.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦЕНТРАЛЬНЫЙ ПРОЦЕССОР МУЛЬТИПРОГРАММНОЙ МУЛЬТИПРОЦЕССОРНОЙ ВЫЧИСЛИТЕЛЬНОЙ СИСТЕМЫ | 1971 |

|

SU309363A1 |

| Операционное устройство микропроцессорной вычислительной системы | 1982 |

|

SU1198532A1 |

| ТРАНСЛЯЦИЯ АДРЕСОВ ВВОДА-ВЫВОДА В АДРЕСА ЯЧЕЕК ПАМЯТИ | 2010 |

|

RU2547705C2 |

| СПОСОБ КОДИРОВАНИЯ И ИСПОЛНЕНИЯ КОНТЕКСТНО-ЗАВИСИМОЙ ПРОГРАММЫ МУЛЬТИКЛЕТОЧНЫМ ПРОЦЕССОРОМ, МУЛЬТИКЛЕТОЧНЫЙ ПРОЦЕССОР, КЛЕТКА И КОММУТАЦИОННОЕ УСТРОЙСТВО МУЛЬТИКЛЕТОЧНОГО ПРОЦЕССОРА ДЛЯ ОСУЩЕСТВЛЕНИЯ СПОСОБА | 2013 |

|

RU2530690C2 |

| Вычислительная система | 1977 |

|

SU692400A1 |

| БУФЕРНОЕ ЗАПОМИНАЮЩЕЕ УСТРОИСГСО | 1970 |

|

SU287123A1 |

| КОНТРОЛЛЕР | 1991 |

|

RU2012043C1 |

| КОМАНДЫ СОХРАНЕНИЯ/СОХРАНЕНИЯ БЛОКА ДАННЫХ ДЛЯ СВЯЗИ С АДАПТЕРАМИ | 2010 |

|

RU2522314C1 |

| Устройство центрального управления процессора | 1983 |

|

SU1136177A1 |

| Арифметическое устройство с микропрограммным управлением | 1988 |

|

SU1541594A1 |

Даты

1971-01-01—Публикация