Изобретение относится к области вычислительной техники и может быть использовано при построении вычислительных машин.

В известных арифметических устройствах, работающих по способу с плавающей запятой, результат каждой операции представляется в нормализованном виде. Получению результата в окончательной форме часто предшествует процесс нормализации результата влево, по окончании которого срабатывает усилитель или триггер завершения операции, разрешая начало следующей операции.

Цель предлагаемого изобретения состоит в разработке арифметического устройства, в котором исключены лишние сдвиги и в связи с этим соответственно снижено время выполнения операций.

Поставленная цель достигается введением в схему арифметического устройства специальных схем, производящих анализ типа операции, следующей за выполняемой в данный момент, и осуществляющих блокировку нормализации влево результата данной операции,, если следующая операция требует выравнивания порядков.

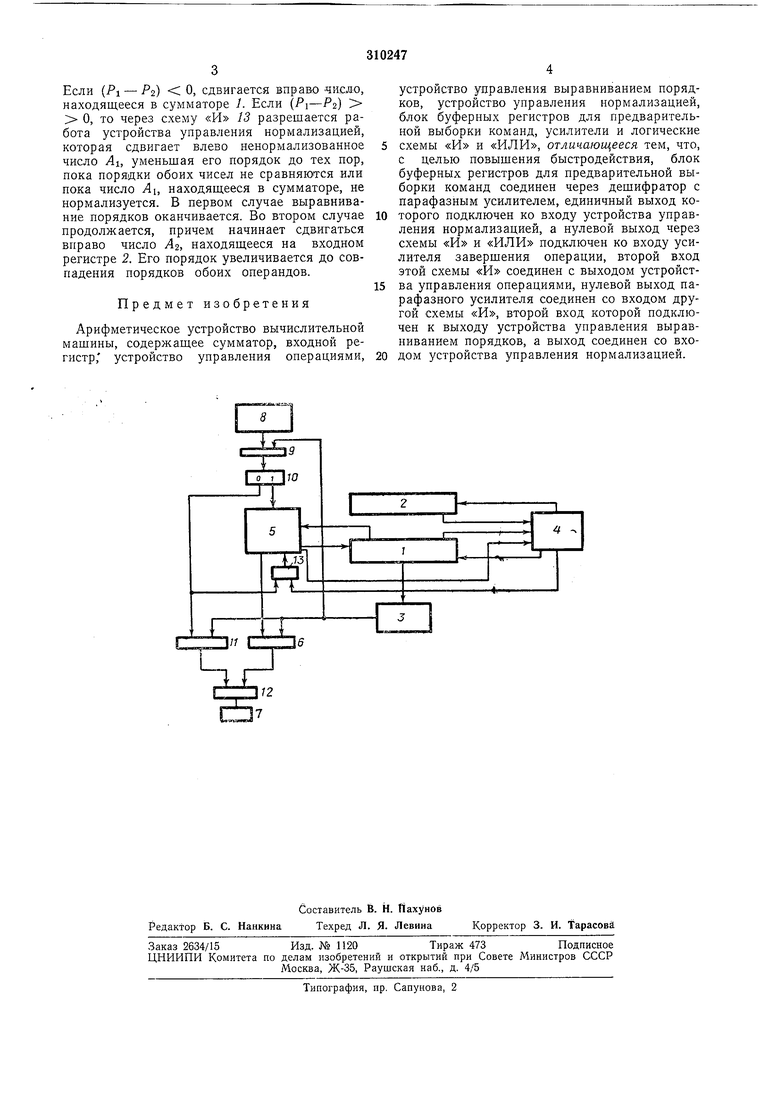

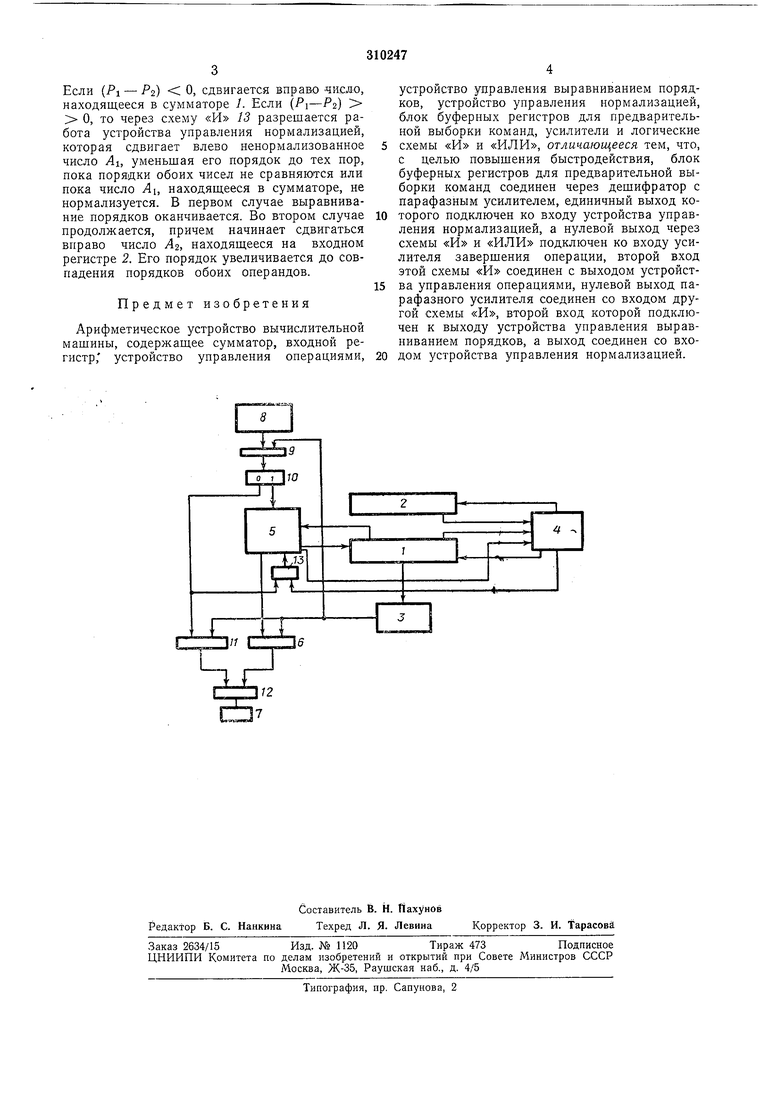

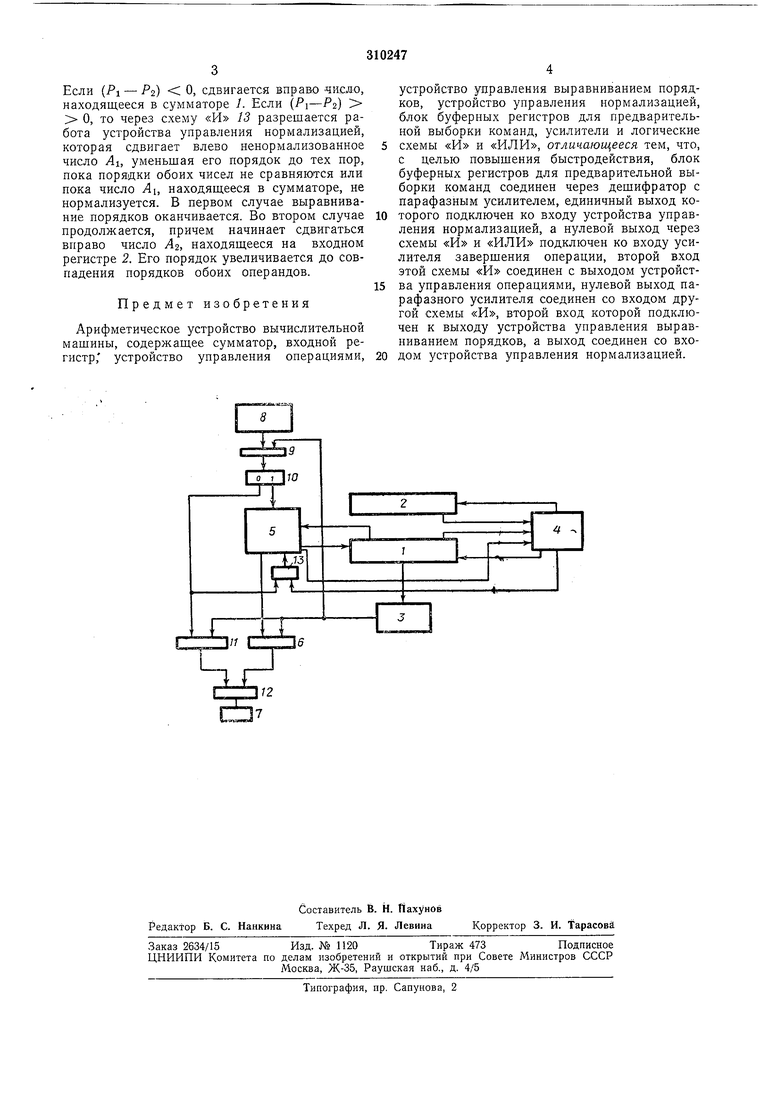

Сущность предлагаемого изобретения поясняется блок-схемой, приведенной на чертеже, где приняты следующие обозначения: / - сумматор; 2 - входной регистр; 3 - устройство управления операциями (УУО); 4 - устройство управления выравниванием порядков (УУВП); 5 - устройство управления нормализацией результата (УУНР); 6 - двухвходовые схемы 7 - усилитель завершения

операции (УЗОп); 8 - буферные регистры операций АУ; 9 - дещифратор групп операций; 10 - парафазный усилитель; 11 - схема 12 - двухвходовая схема 13 - схема «И.

По сигналу устройства управления 3 устройство 5 управления нормализацией начинает работать при условии, что следующая операция, хранящаяся в буферных регистрах АУ 8, не требует выравнивания порядков. В этом

случае усилитель 10 через дешифратор 9 устанавливается в состояние «1, разрешая нормализацию. После ее окончания устройство 3 управления операциями через схемы «И 6 и «ИЛИ 12 возбуждает усилитель 7, разрешая

начало следующей операции.

Если следующая за выполняемой операция требует выравнивания порядков, то усилитель 10 остается в нулевом состоянии. Устройство 3 управления операциями через схемы «И 11

и «ИЛИ 12 возбуждает усилитель 7, разрешая начало следующей операции, без выполнения нормализации результата предыдущей операции. Устройство 4 управления выравниванием

Если (Pi - Pz) О, сдвигается вправо ЧИсло, находящееся в сумматоре /. Если (Pi-Pz) О, то через схему «И 13 разрешается работа устройства управления нормализацией, которая сдвигает влево ненормализованное число AI, уменьшая его порядок до тех пор, пока порядки обоих чисел не сравняются или пока число AI, находящееся в сумматоре, не нормализуется. В первом случае выравнивание порядков оканчивается. Во втором случае продолжается, причем начинает сдвигаться вправо число Л2, находящееся на входном регистре 2. Его порядок увеличивается до совпадения порядков обоих операндов.

Предмет изобретения

Арифметическое устройство вычислительной машины, содержащее сумматор, входной регистр, устройство управления операциями.

устройство управления выравниванием порядков, устройство управления нормализацией, блок буферных регистров для предварительной выборки команд, усилители и логические схемы «И и «ИЛИ, отличающееся тем, что, с целью повышения быстродействия, блок буферных регистров для предварительной выборки команд соединен через дешифратор с парафазным усилителем, единичный выход которого подключен ко входу устройства управления нормализацией, а нулевой выход через схемы «И и «ИЛИ подключен ко входу усилителя заверщения операции, второй вход этой схемы «И соединен с выходом устройства управления операциями, нулевой выход парафазного усилителя соединен со входом другой схемы «И, второй вход которой подключен к выходу устройства управления выравниванием порядков, а выход соединен со входом устройства управления нормализацией.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЛОГИЧЕСКИЙ БЛОК АРИФМЕТИЧЕСКОГО УСТРОЙСТВА | 1969 |

|

SU241108A1 |

| Устройство для умножения | 1976 |

|

SU651341A1 |

| ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО для ПЕРЕРАБОТКИ ЧИСЛОВОЙ И БУКВЕННОЙ ИНФОРМАЦИИ | 1969 |

|

SU255656A1 |

| Арифметическое устройство | 1984 |

|

SU1193661A1 |

| АРИФМЕТИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 2004 |

|

RU2292580C2 |

| ПРОЦЕССОР ДЛЯ ЦИФРОВОЙ СИСТЕМЫ ОБРАБОТКИ ДАННЫХ | 1971 |

|

SU305477A1 |

| Арифметическое устройство | 1989 |

|

SU1647557A1 |

| ОПТИЧЕСКИЙ ЦИФРОВОЙ СУММАТОР С ПЛАВАЮЩЕЙ ТОЧКОЙ | 1997 |

|

RU2123200C1 |

| Цифровое устройство для логарифмирования двоичных чисел | 1972 |

|

SU448459A1 |

| ВЫЧИСЛИТЕЛЬНАЯ ОТКРЫТАЯ РАЗВИВАЕМАЯ АСИНХРОННАЯ МОДУЛЬНАЯ СИСТЕМА | 2009 |

|

RU2453910C2 |

Даты

1971-01-01—Публикация