Известно аналогичное устройство, содержащее управляемые делители частоты и логические схемы.

Описываемое устройство отличается от известного тем, что первый делитель выполнен на двухтактной линии задержки со схемой управления, включенной в цепь обратной связи делителя так, что обмотка запрета второй ячейки соединена с выходом второй схемы «НЕТ, а в цени выхода второй ячейки делителя включены обмотки запрета первой и второй схем «НЕТ, обмотка записи третьей ячейки делителя соединена с выходом третьей схемы «НЕТ, цепь записи которой соединена с выходом ячейки намяти, а цепь запрета - с выходом второй схемы «НЕТ, причем выходы первой и второй схем «НЕТ и выходы ячеек памяти включены на двоичный сумматор, выход которого подключен ко входу второго делителя. Это позволяет уменьшить манинулятивные искажения при низкой несущей частоте.

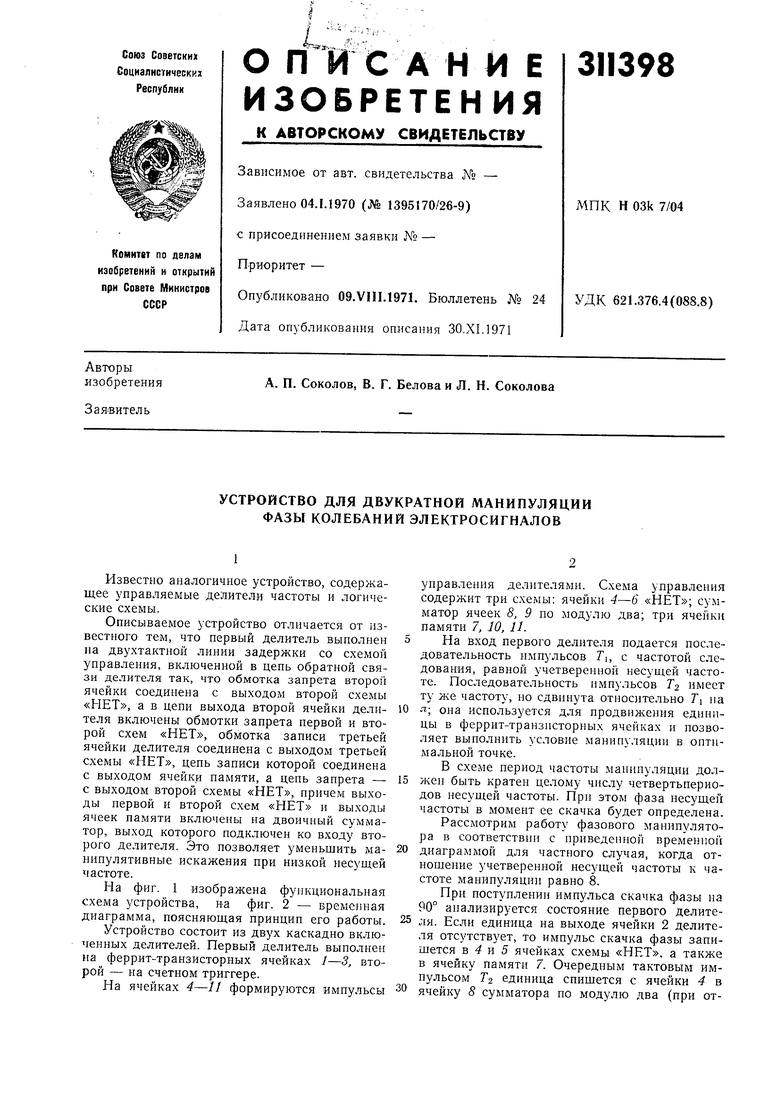

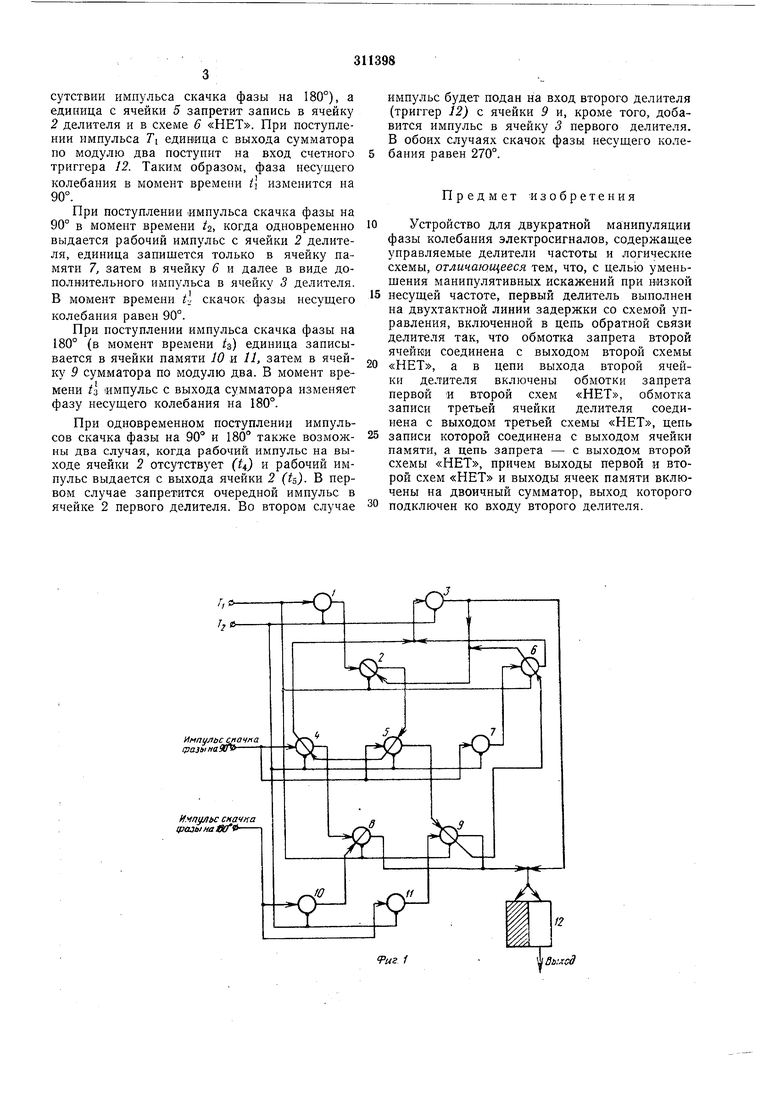

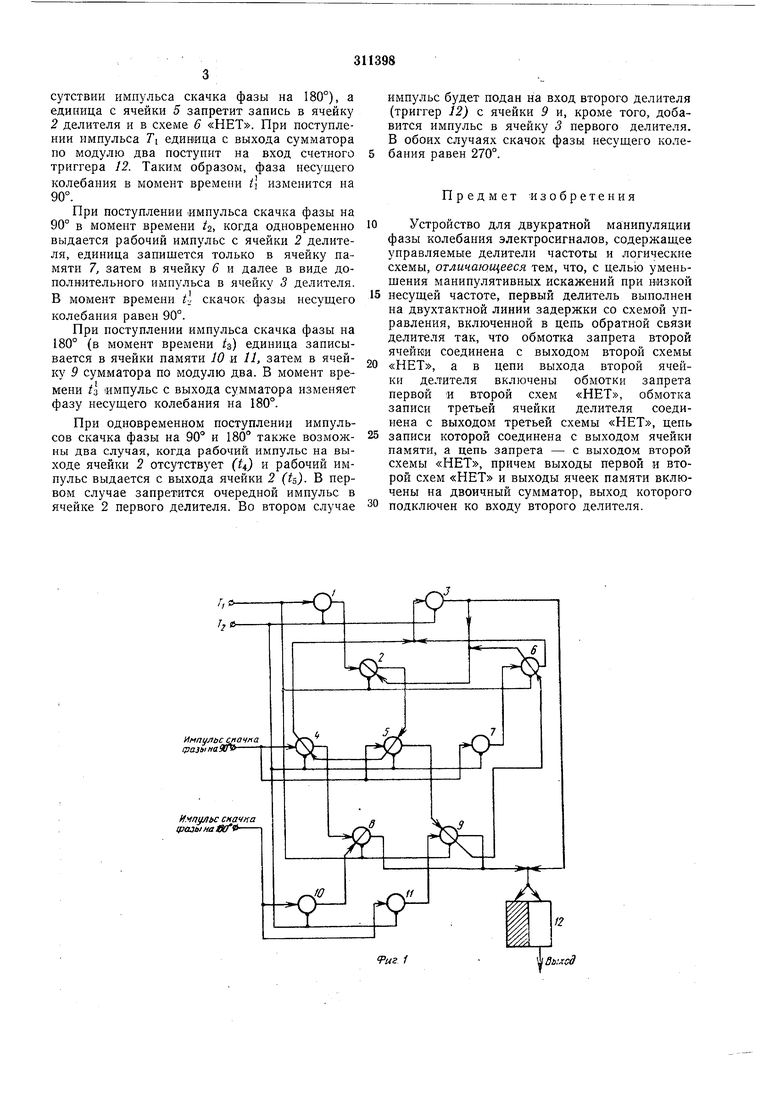

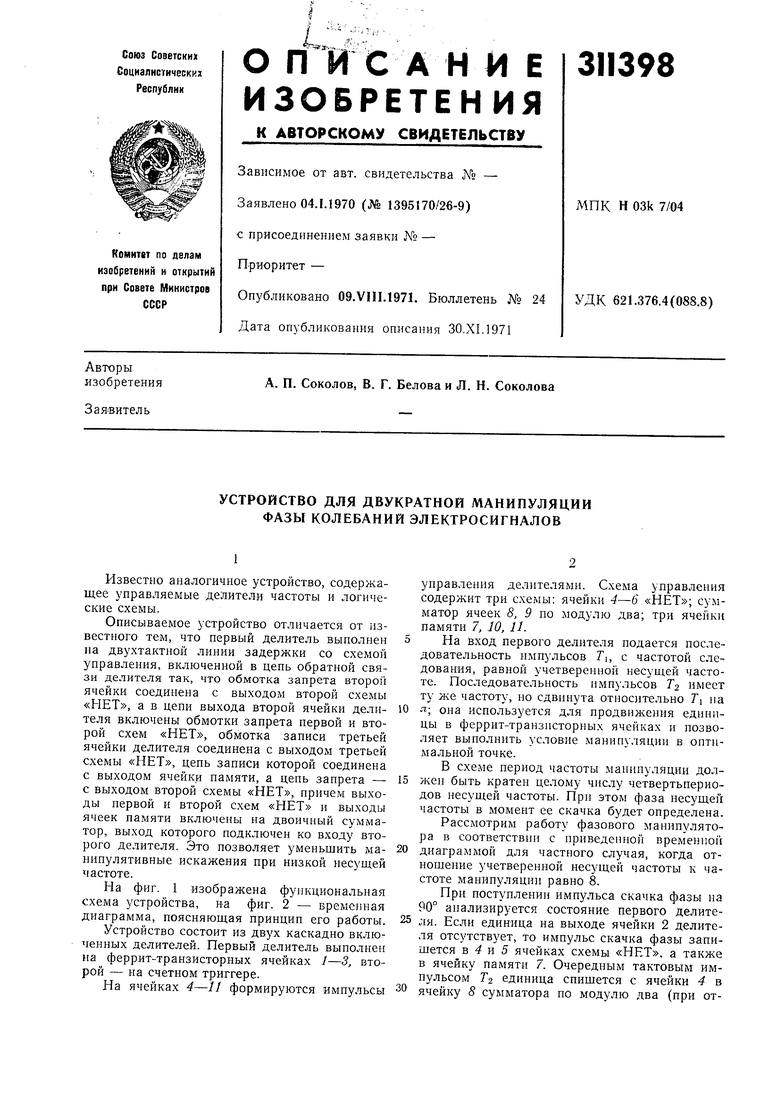

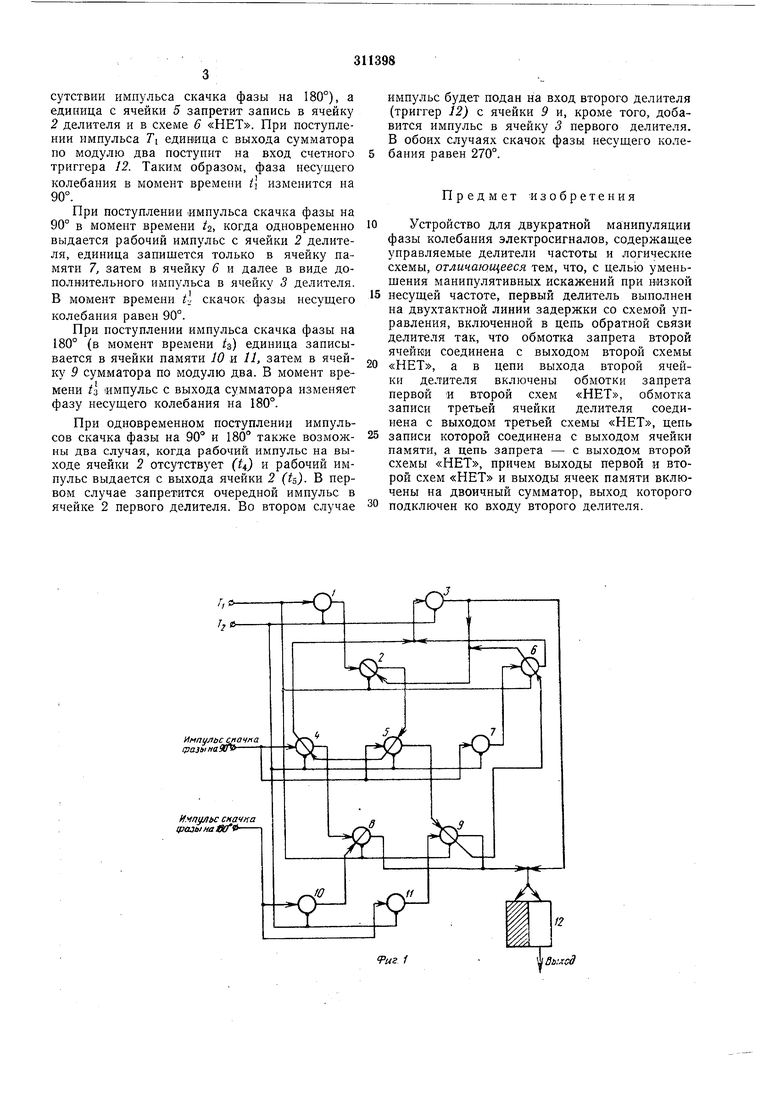

На фиг. 1 изображена функциональная схема устройства, на фиг. 2 - временная диаграмма, поясняющая принцип его работы.

Устройство состоит из двух каскадно включенных делителей. Первый делитель выполнен на феррит-транзисторных ячейках /-3, второй - на счетном триггере.

управления делителями. Схема управления содержит три схемы: ячейки 4-6 сумматор ячеек 8, 9 но модулю два; три ячейки памяти 7, 10, 11.

На вход первого делителя подается последовательность импульсов TI, с частотой следования, равной учетверенной несущей частоте. Последовательность импульсов Г2 имеет ту же частоту, но сдвннута относительно TI на я; она используется для продвилсения единицы в феррит-транзисторных ячейках и позволяет выполнить условие манипуляции в оптимальной точке.

В схеме период частоты манипуляции должен быть кратен целому числу четвертьпериодов несущей частоты. При этом фаза несущей

частоты в момент ее скачка будет определена.

Рассмотрим работу фазового манипулятора в соответствни с приведенной временной диаграммой для частного случая, когда отнонление учетверенной несущей частоты к частоте манипуляцин равно 8.

При поступлении импульса скачка фазы на 90° анализируется состояние первого делителя. Если единица на выходе ячейки 2 делителя отсутствует, то импульс скачка фазы запишется в - и 5 ячейках схемы «НЕТ, а также в ячейку памяти 7. Очередным тактовым импульсом Т2 единица спишется с ячейки 4 в ячейку 8 сумматора по модулю два (при отсутствии импульса скачка фазы на 180°), а единица с ячейки 5 запретит запись в ячейку 2 делителя и в схеме 6 «НЕТ. При поступлении импульса Т единица с выхода сумматора по модулю два поступит на вход счетного триггера 12. Таким образом, фаза несущего

колебания в момент времени t изменится на 90°.

При поступлении «мпульса скачка фазы на 90° в момент времени tz, когда одновременно выдается рабочий импульс с ячейки 2 делителя, единица запишется только в ячейку памяти 7, затем в ячейку 6 и далее в виде дополнительного имнульса в ячейку 3 делителя. В момент времени , скачок фазы несущего колебания равен 90°.

При поступлении импульса скачка фазы на 180° (в момент времени /з) единица записывается в ячейки памяти 10 и 11, затем в ячейку 9 сумматора по модулю два. В момент времени ifa импульс с выхода сумматора изменяет фазу несущего колебания на 180°.

При одновременном поступлении импульсов скачка фазы на 90° и 180° также возможны два случая, когда рабочий импульс на выходе ячейки 2 отсутствует (t4) и рабочий импульс выдается с выхода ячейки 2 (U). В первом случае запретится очередной импульс в ячейке 2 первого делителя. Во втором случае

импульс будет подан на вход второго делителя (триггер 12) с ячейки 9 и, кроме того, добавится импульс в ячейку 3 первого делителя. В обоих случаях скачок фазы несущего колебания равен 270°.

Предмет -изобретения

Устройство для двукратной манипуляции фазы колебания электросигналов, содержащее управляемые делители частоты и логические схемы, отличающееся тем, что, с целью уменьщения манипулятивных искажений нри низкой несущей частоте, первый делитель выполнен на двухтактной линии задержки со схемой управления, включенной в цепь обратной связи делителя так, что обмотка запрета второй ячейки соединена с выходом второй схемы «НЕТ, а в цепи выхода второй ячейки делителя включены обмотки запрета первой 1И второй схем «НЕТ, обмотка записи третьей ячейки делителя соединена с выходом третьей схемы «НЕТ, цепь записи которой соединена с выходом ячейки памяти, а цепь запрета - с выходом второй схемы «НЕТ, причем выходы первой и второй схем «НЕТ и выходы ячеек памяти включены на двоичный сумматор, выход которого подключен ко входу второго делителя.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство поэлементной синхронизации | 1985 |

|

SU1319301A1 |

| Устройство для деления последовательных чисел | 1987 |

|

SU1462298A1 |

| Генератор случайного процесса (его варианты) | 1983 |

|

SU1125624A1 |

| ПРИЕМНИК СПУТНИКОВЫХ РАДИОНАВИГАЦИОННЫХ СИСТЕМ | 1997 |

|

RU2118054C1 |

| Устройство фазовой автоподстройки частоты | 1991 |

|

SU1826135A1 |

| УСТРОЙСТВО для ОПРЕДЕЛЕНИЯ ДОСТОВЕРНОСТИ ИНФОРМАЦИИ, ПЕРЕДАВАЕМОЙ ЦИКЛИЧЕСКИМ КОДоМ | 1971 |

|

SU316204A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА СИГНАЛОВ ТОЧНОГО ВРЕМЕНИ | 1990 |

|

RU2033640C1 |

| Устройство фазовой автоподстройки частоты | 1991 |

|

SU1811020A1 |

| Генератор случайного процесса | 1983 |

|

SU1113800A1 |

| Приемник сигналов с двойной фазовой манипуляцией | 1985 |

|

SU1264370A2 |

Импульс СП шаз1 1на90

Н 1пулк CHavna ipajtii на

12Rfl fFtjpd

t

Авторы

Даты

1971-01-01—Публикация