Изобретение может быть применено в системах связи и радиолокационных системах измерения дальности.

Известно устройство Корреляционного поиска, реализующее равномерный циклический поиск по задержке.

Цель изобретения-сокращение времени поиска.

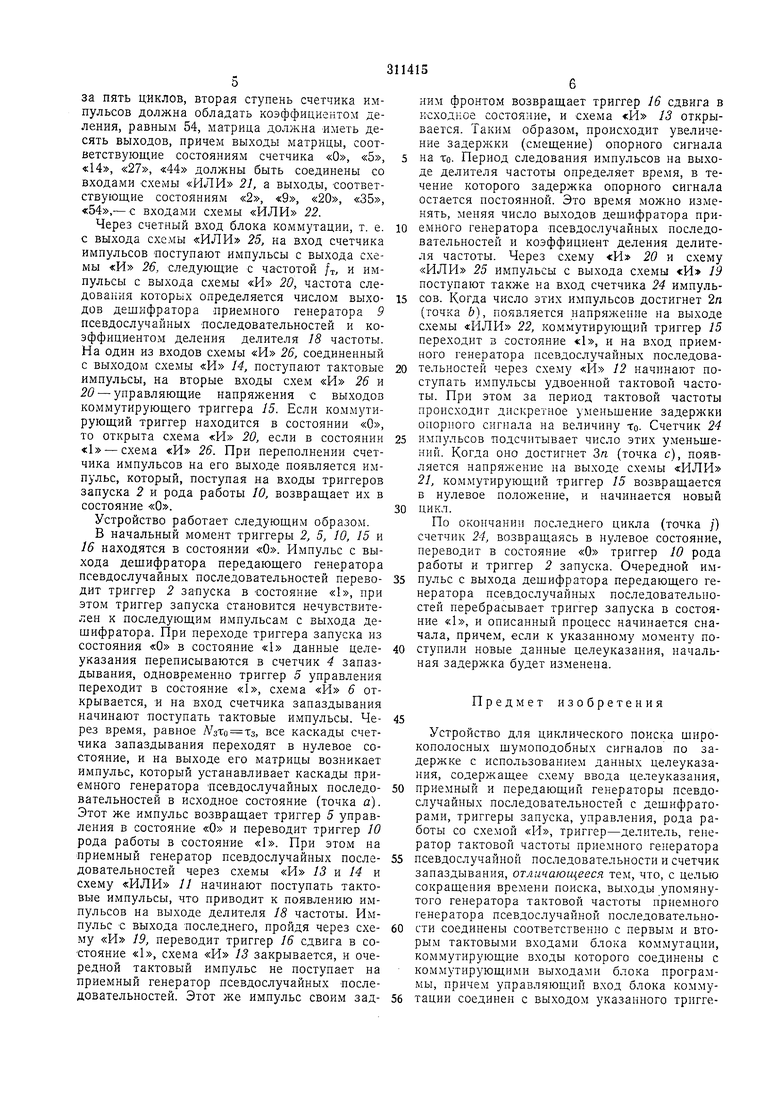

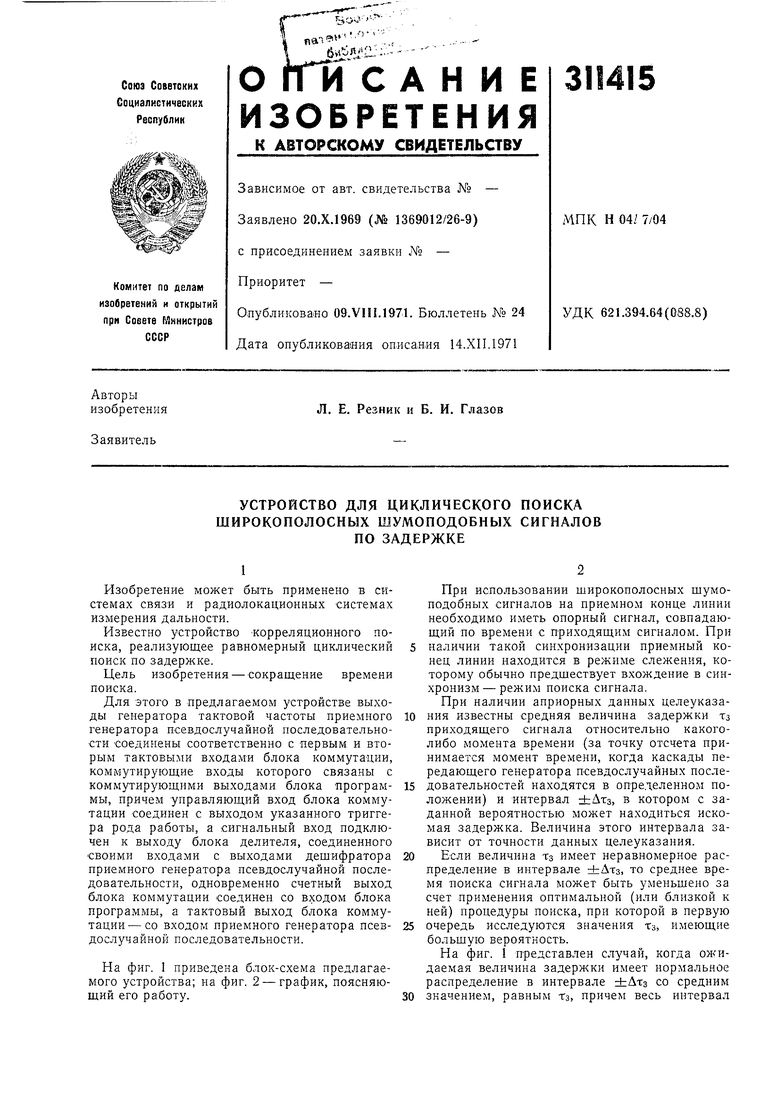

Для этого в предлагаемом устройстве выходы генератора тактовой частоты приемного генератора псевдослучайной последовательности соединены соответственно с первым и вторым тактовыми входами блока коммутации, коммутирующие входы которого связаны с коммутирующими выходами блока программы, причем управляющий вход блока коммутации соединен с выходом указанного триггера рода работы, а сигнальный вход подключен к выходу блока делителя, соединенного своими входами с выходами дешифратора приемного генератора псевдослучайной последовательности, одновременно счетный выход блока коммутации соединен со входом блока программы, а тактовый выход блока коммутации- со входом приемного генератора псевдослучайной последовательности.

При использовании широкополосных шумоподобных сигналов на приемном конце линии необходимо иметь опорный сигнал, совпадающий по времени с приходящим сигналом. При наличии такой синхронизации приемный конец линии находится в режиме слел :ения, которому обычно предшествует в.хождение в синхронизм- режим поиска сигнала.

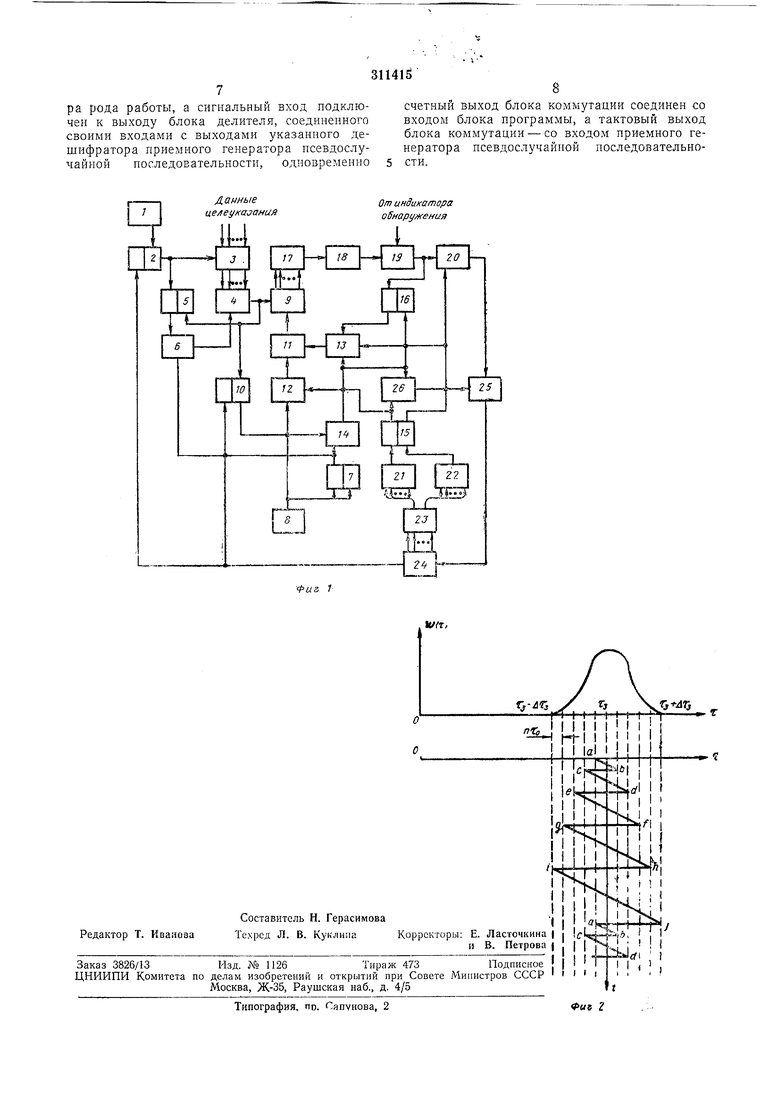

При наличии априорных данных целеуказания известны средняя величина задержки тз приходящего сигнала относительно какоголибо момента времени (за точку отсчета принимается момент времени, когда каскады передающего генератора псевдослучайных последовательностей находятся в определенном положении) и интервал ±Дтз, в котором с заданной вероятностью может находиться искомая задержка. Величина этого интервала зависит от точности данных целеуказания.

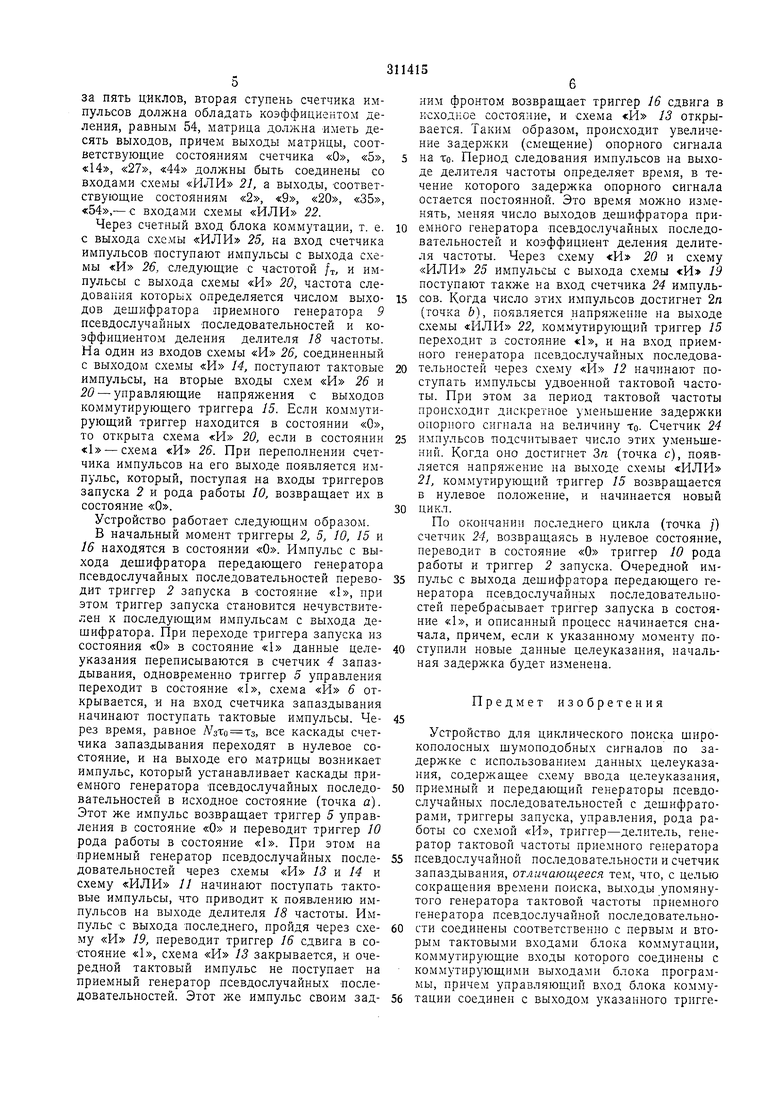

Если величина тз имеет неравномерное распределение в интервале ±Атз, то среднее время поиска сигнала может быть уменьшено за счет применения оптимальной (или близкой к ней) процедуры поиска, при которой в первую очередь исследуются значения Тз, имеющие большую вероятность.

возможных значений задержки просматривается за пять циклов. Поиск на каждом цикле осуществляется путем равномерного сканирования в интервале задержек, оцределяемом номером цикла. Величина (амплитуда) каждого цикла кратна 2-го и равна 2т;о/(, где То - номинальный период следования импульсов приемного генератора псевдослучайных последовательностей; К. - помер цикла; п

ДТз

: - ; т - число циклов.

Если за т частных циклов, соответствующих полному циклу поиска, сигнал не найден, процедура поиска возобновляется с короткого цикла. Необходимо учитывать, что при различных значениях -тз точка а соответствует одному и тому же состоянию каскадов приемного генератора псевдослучайных последовательностей.

В предлагаемом устройстве выход дешифратора передающего генератора / псевдослучайных последовательностей соединен с одним из входов триггера 2 запуска. Данные целеуказания об ожидаемой величине Тз поступают на схему 3 ввода целеуказания в виде

двоичного числа Фронт перепада насо

пряжения, образующийся при переходе триггера запуска из состояния «О в «1, является командой для переписывапия без стирания числа NZ в каскады счетчика 4 запаздывания, работающего на вычитание. Этот же фронт переводит триггер 5 управления в состояние -, при котором открывается схема «И 6, и на вход счетчика запаздывания с триггера-делителя 7 поступают тактовые импульсы с частотой .

и

Триггер-делитель собран по схеме со счетным входом, на который подаются импульсы с частотой 2/т. поступающие от генератора S тактовой частоты. Когда все каскады счетчика запаздывания переходят в состояние «О, на выходе матрицы счетчика появляется импульс, который поступает на вход приемного генератора 9 псевдослучайных последовательностей и устанавливает каскады этого генератора в исходное положение а. Этот же импульс, поступая на входы триггеров управления 5 и рода работы 10, переводит первый в состояние «О, а второй - в состояние «1.

Тактовые импульсы на вход приемного генератора псевдослучайных последовательностей .поступают с выхода схемы «ИЛИ 11 блока коммутации. Схема «ИЛИ // имеет два входа, на один из которых подаются импульсы с частотой 2/т, поступающие через схему «И 12 от генератора тактовой частоты, т. е. по первому тактовому входу блока коммутации, на другой вход через схемы «И 13 и 14 поступают импульсы с выхода триггераделителя с частотой /т. т. е. по второму тактовому входу блока коммутации. Схема «И 14 управляется по управляющему входу блока коммутации выходным напряжением триггера 10 рода работы и открывается, когда триггер находится в состоянии «1. Управляющее напряжение на входы схем «И 12 и 13 подается с противоположных плеч коммутирующего триггера 15. Схема «И 12 открыта, когда коммутирующий триггер находится в состоянии «7, а схема «И 13 открыта, когда коммутирующий триггер находится в состоянии «О. Третий вход схемы «И 13 соединен с выходом триггера 16 сдвига. При этом схема «И открыта, если триггер сдвига находится в состоянии «О.

Выходы дешифратора приемного генератора псевдослучайных последовательностей через схему «ИЛИ 17 блока делителя соединены со входом делителя 18 частоты на триггерах.

Блок делителя состоит из схемы «ИЛИ 17, делителя 18 и схе-мы «И 19. С выхода делителя частоты импульсы поступают на схему «И 19 и далее через сигнальный вход блока коммутации - на схему «И 20 и триггер 16

сдвига. Управляющий сигнал па второй вход схемы «И 19 подается от индикатора обнаружения. В режиме поиска схема «И 19 открыта. Импульсы с выхода схемы «И 19, поступающие на вход триггера сдвига, переводят его в состояние «О.

Коммутирующий триггер 15 переходит из одного состояния в другое под воздействием импульсов, поступающих на его входы через коммутирующие входы блока коммутации с

коммутирующих выходов блока программ, т. е. с выходов схем «ИЛИ 21 и 22. Блок программы состоит из схем «ИЛИ 21 и 22, диодной матрицы 23 и счетчика 24 импульсов. Если импульс появляется на входе триггера,

соединенном со схемой «ИЛИ 21, то триггер нереходит в состояние «О, при появлении импульса на другом входе - в состояние «1. Входы схем «ИЛИ 21 и 22 соединены с выходами диодной матрицы 23, подключенной к

счетчику 24, собранному на триггерах. Счетчик импульсов является двухступенчатым: первая ступень представляет собой делитель с коэффициентом деления п; вторая - собственно счетчик, к разрядам которого подключена матрица. Ко входам схемы «ИЛИ 21 подключены выходы матрицы, соответствующие началу циклов (точки а, с, е, g, i), а КО входам схемы «ИЛИ 22 - выходы матрицы, соответствующие окончанию циклов

(точки Ь, d, I, h, /).

Когда все разряды счетчика импульсов переходят в состояние «О, появляется напряжение на первом выходе матрицы (точка а) и входе схемы «ИЛИ 21. Если на вход счетчика подается 2я импульсов, появляется напряжение на втором входе матрицы (точка Ь) и входе схемы «ИЛИ 22, после поступления еще Зп импульсов - на третьем выходе (точка с) и так далее. В рассматриваемом примеза пять циклов, вторая ступень счетчика импульсов должна обладать коэффициентом деления, равным 54, матрица должна иметь десять выходов, причем выходы матрицы, соответствующие состояниям счетчика «О, «5, «14, «27, «44 должны быть соединены со входами -схемы «ИЛИ 21, а выходы, соответствующие состояниям «2, «9, «20, «35, «54,- с входами схемы «ИЛИ 22.

Через счетный вход блока коммутации, т. е. с выхода схемы «ИЛИ 25, на вход счетчика импульсов поступают импульсы с выхода схемы «И 26, следующие с частотой /т. и импульсы с выхода схемы «И 20, частота следования которых определяется числом выходов дешифратора приемного генератора 9 псевдослучайных последовательностей и коэффициентом деления делителя 18 частоты. На один из входов схемы «И 26, соединенный с выходом схемы «И 14, поступают тактовые импульсы, на вторые входы схем «И 26 и 20 - управляющие напряжения с выходов коммутирующего триггера 15. Если коммутирующий триггер находится в состоянии «О, то открыта схема «И 20, если в состоянии «1 - схема «И 26. При переполнении счетчика импульсов на его выходе появляется импульс, который, поступая на входы триггеров запуска 2 и рода работы 10, возвращает их в состояние «О.

Устройство работает следующим образом.

В начальный момент триггеры 2, 5, 10, 15 и 16 находятся в состоянии «О. Импульс с выхода дешифратора передающего генератора псевдослучайных последовательностей переводит триггер 2 запуска в состояние «1, при этом триггер запуска становится нечувствителен к последующим импульсам с выхода дешифратора. При переходе триггера запуска из состояния «О в состояние «1 данные целеуказания переписываются в счетчик 4 запаздывания, одновременно триггер 5 управления переходит в состояние «1, схема «И 6 открывается, и на вход счетчика запаздывания начинают поступать тактовые импульсы. Через время, равное ЛзТо Тз, все каскады счетчика запаздывания переходят в нулевое состояние, и на выходе его матрицы возникает импульс, который устанавливает каскады приемного генератора псевдослучайных последовательностей в исходное состояние (точка а. Этот же импульс возвращает триггер 5 управления в состояние «О и переводит триггер 10 рода работы в состояние «Ь. При этом на приемный генератор псевдослучайных последовательностей через схемы «И 13 и 14 и схему «ИЛИ 11 начинают поступать тактовые импульсы, что приводит к появлению импульсов на выходе делителя 18 частоты. Импульс с выхода последнего, пройдя через схему «И 19, переводит триггер 16 сдвига в состояние «1, схема «И 13 закрывается, и очередной тактовый импульс не поступает на приемный генератор псевдослучайных последовательностей. Этот же импульс своим задним фронтом возвращает триггер 16 сдвига в исходное состояние, и схема «И 13 открывается. Таким образом, происходит увеличение задержки (смещение) опорного сигнала

на То. Период следования импульсов на выходе делителя частоты определяет время, в течение которого задержка опорного сигнала остается постоянной. Это время можно изменять, меняя число выходов дешифратора приемного генератора псевдослучайных последовательностей и коэффициент деления делителя частоты. Через схему «И 20 и схему «ИЛИ 25 импульсы с выхода схемы «И 19 поступают также на вход счетчика 24 импульсов. Когда число этих импульсов достигнет 2п (точка Ь, появляется напряжение на выходе схемы «ИЛИ 22, коммутирующий триггер 15 переходит з состояние «1, и на вход приемного генератора псевдослучайных носледовательностей через схему «И 12 начинают поступать импульсы удвоенной тактовой частоты. При этом за период тактовой частоты происходит дискретное уменьшение задержки опорного сигнала на величину TO. Счетчик 24

импульсов подсчитывает число этих уменьшений. Когда оно достигнет Зп (точка с), появляется напряженне на выходе схемы «Р1ЛИ 21, коммутирующий триггер 15 возвращается в нулевое положение, и начинается новый

цикл.

По окончании последнего цикла (точка /) счетчик 24, возвращаясь в нулевое состояние, переводит в состояние «О триггер 10 рода работы и триггер 2 запуска. Очередной импульс с выхода дешифратора передающего генератора псевдослучайных последовательпостей перебрасывает триггер запуска в состояние «1, и описанный процесс начинается сначала, причем, если к указанному моменту поступили новые данные целеуказания, начальная задержка будет изменена.

Предмет изобретения

45

Устройство для циклического поиска широкополосных шумоподобных сигналов по задержке с использованием данных целеуказания, содержашее схему ввода целеуказания, приемный и передающий генераторы псевдослучайных последовательностей с дешифраторами, триггеры запуска, управления, рода работы со схемой «И, триггер-делитель, генератор тактовой частоты приемного генератора

псевдослучайной последовательности и счетчик запаздывания, отличающееся тем, что, с целью сокращения времени поиска, выходы упомянутого генератора тактовой частоты приемного генератора псевдослучайной последовательности соединены соответственно с первым и вторым тактовыми входами блока коммутации, коммутирующие входы которого соединены с коммутирующими выходами блока программы, причем управляющий вход блока коммуpa рода работы, а сигнальный вход подключен к выходу блока делителя, соединенного своими входами с выходами указанного дешифратора приемного генератора нсевдослучайной носледовательности, одновременно

/(анные ие/1еукаоания

,

счетный выход блока коммутации соединен со входом блока программы, а тактовый выход блока коммутации - со входом приемного генератора псевдослучайной последовательности.

От индикатора оУнару/кения

| название | год | авторы | номер документа |

|---|---|---|---|

| Управляемая линия задержки | 1990 |

|

SU1725370A2 |

| ПРИЕМНОЕ УСТРОЙСТВО ШИРОКОПОЛОСНЫХ СИГНАЛОВ | 1983 |

|

SU1840292A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА ДИСКРЕТНОЙ ИНФОРМАЦИИ | 1990 |

|

RU2022470C1 |

| СИСТЕМА СВЯЗИ | 2003 |

|

RU2249914C2 |

| Устройство для формирования псевдослучайных сигналов | 1984 |

|

SU1205262A2 |

| Управляемая линия задержки | 1984 |

|

SU1197068A1 |

| ПРИЕМОПЕРЕДАЮЩАЯ АППАРАТУРА ШИРОКОПОЛОСНЫХ ПСЕВДОСЛУЧАЙНЫХ СИГНАЛОВ | 1979 |

|

SU1840119A1 |

| Устройство тактовой синхронизации псевдослучайных последовательностей | 1983 |

|

SU1092744A1 |

| СИСТЕМА ДЛЯ ПЕРЕДАЧИ И ПРИЕМА ИНФОРМАЦИИ | 1992 |

|

RU2047908C1 |

| Устройство для формирования псевдослучайных сигналов | 1979 |

|

SU995292A1 |

tV(f,

Даты

1971-01-01—Публикация