Изобретение относится к цифровой вычислительной технике.

Известны полные двоичные сумматоры функционального типа с 5-образной зависимостью выходного напряжения от входного тока, т. е. выполняющие функцию полного двоичного суммирования и переноса за счет внутренних функциональных связей, без преобразования в стандартные логические операции «ИЛИ, «И, «НЕ.

Однако в известных устройствах ограничена возможность увеличения логического перепада напряжений насыщением транзисторов, предъявляются жесткие требования к расбросу параметров резисторов и необходим дополнительный источник напряжения.

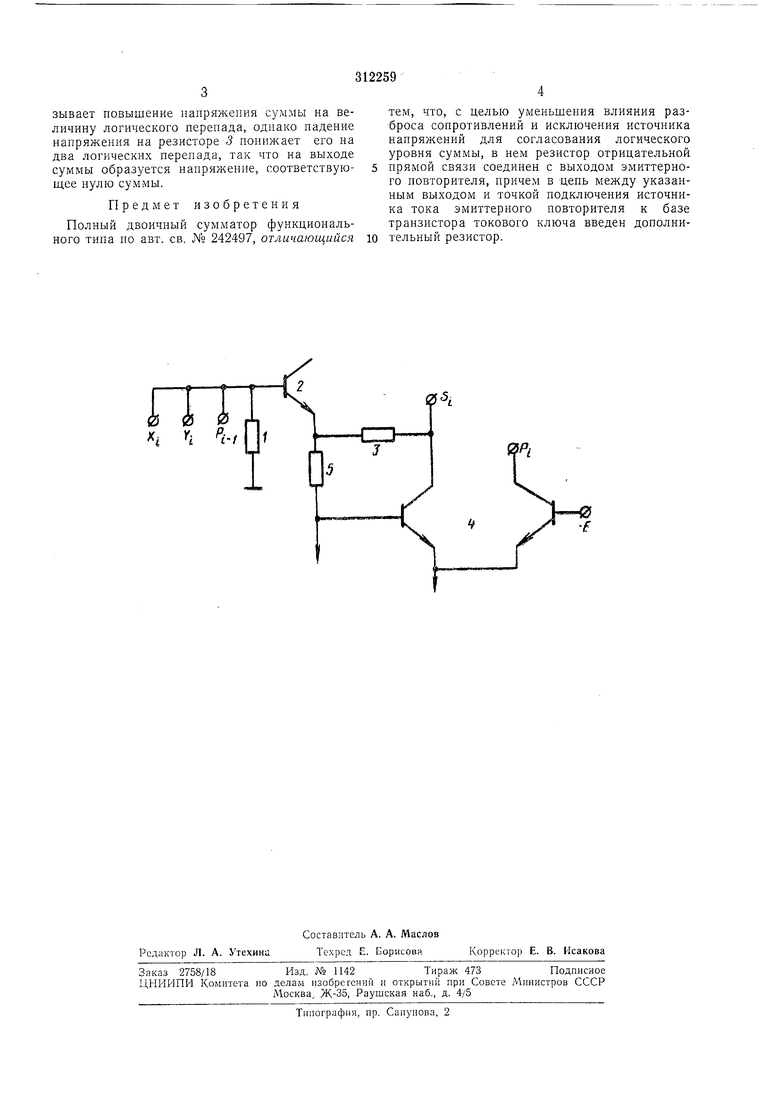

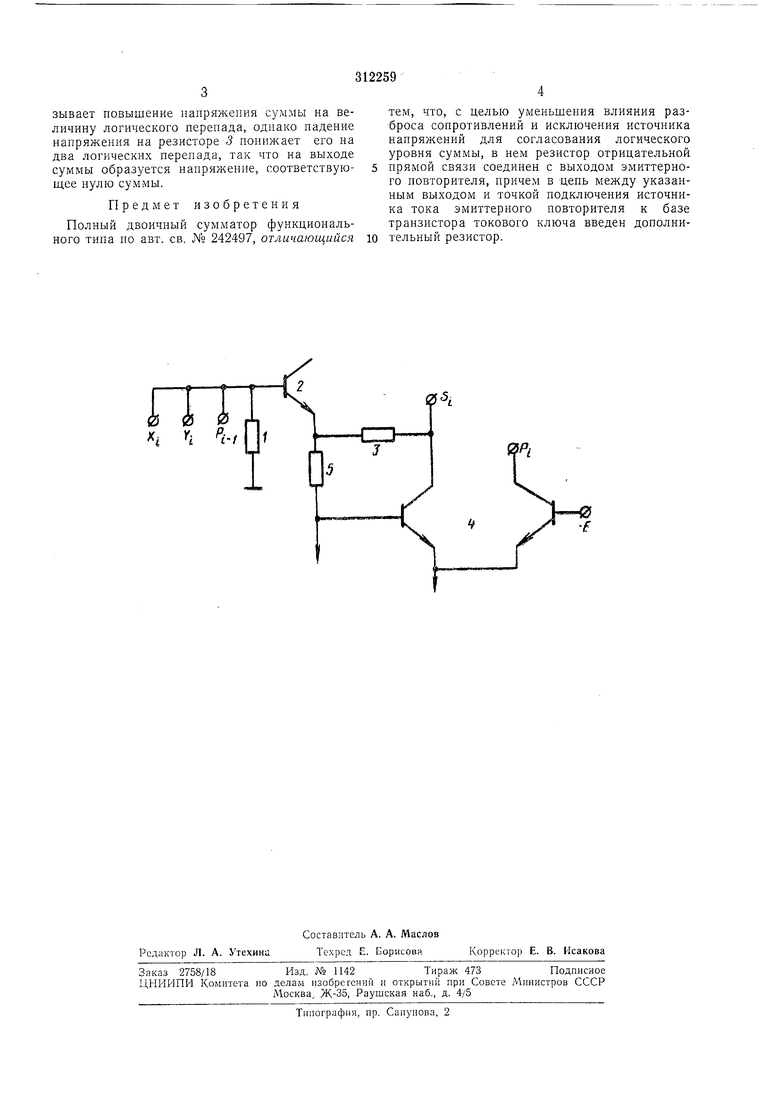

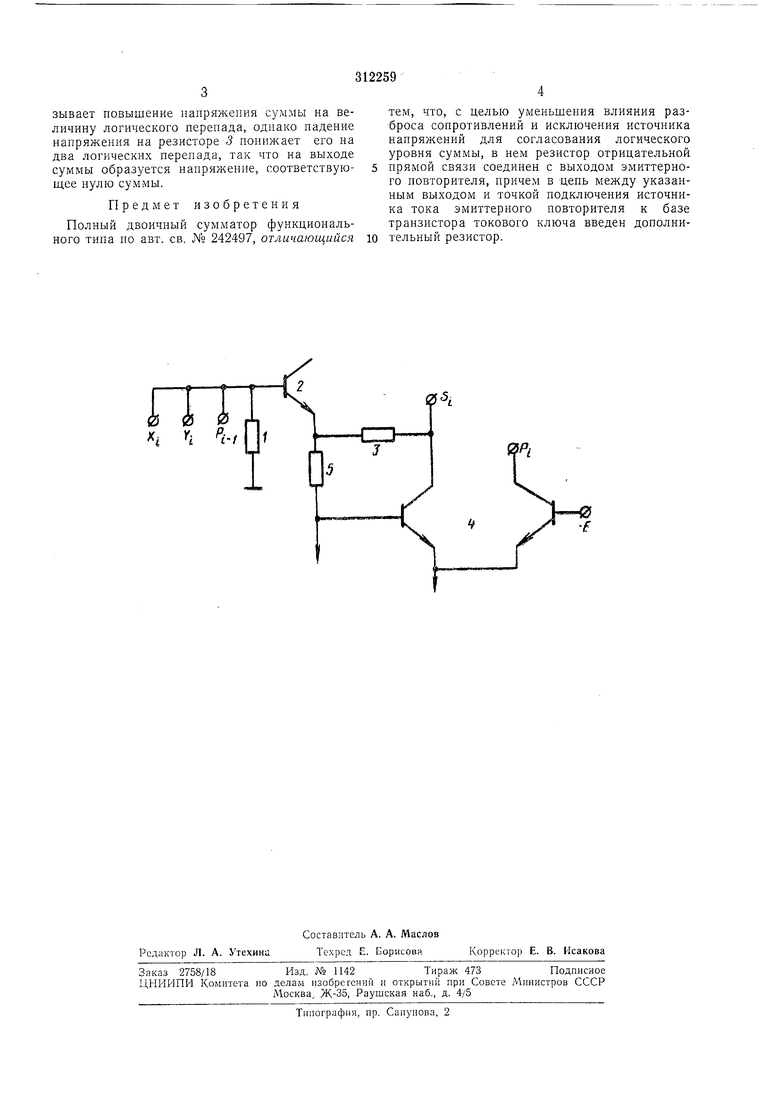

Предложенное устройство отличается тем, что в нем резистор отрицательной прямой связи соединен с выходом эмиттерного повторителя. Причем в цепь между указанным выходом и точкой подключения источника тока эмиттерного повторителя к базе транзистора токового ключа введен дополнительный резистор.

Это позволило уменьшить влияние разброса сопротивлений и исключить источник напряжений для согласования логического уровня суммы.

ны в виде токов в точку соединения резистора / со входом эмиттерного повторителя 2, к выходу которого присоединен резистор 3 прямой отрицательной связи. Первый выход токового ключа 4 является выходом напряжения суммы, второй - выходом тока переноса. Второй вход ключа 4 соединен с источником напряжения смещения, а первый присоединен к дополнительному резистору 5.

При поступлении на вход трех логических нулей (три тока присутствуют) имеет место наиболее низкий уровень напряжения, первый транзистор токового ключа 4 закрыт, ток переноса равен единице (что соответствует

логическому нулю переноса). На выходе суммы имеется низкий уровень напряжения (что соответствует нулю сумм).

При поступлении на вход одной логической единицы (присутствуют два тока) уровень

напряжения на выходе суммы повышается на величину одного перепада (что соответствзет единице суммы). Напряжение источника смещения - Е выбрано таким, что ток переноса продолжает протекать (что соответствует логическому нулю переноса).

При поступлении на вход двух логических единиц (присутствует один ток) уровень напряжения повышается настолько, что второй транзистор ключа 4 закрывается (что соотзывает повышение напряжения суммы на величину логического перепада, однако падение напряжения на резисторе 3 понижает его на два логических перепада, так что на выходе суммы образуется напряжение, соответствующее нулю суммы.

Предмет изобретения

Полный двоичный сумматор функционального типа по авт. св. № 242497, отличающийся

тем, что, с целью уменьшения влияния разброса сопротивлений и исключения источника напряжений для согласования логического уровня суммы, в нем резистор отрицательной прямой связи соединен с выходом эмиттерного повторителя, причем в цепь между указанным выходом и точкой подключения источника тока эмиттерного повторителя к базе транзистора токового ключа введен дополнительный резистор.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПОЛНЫЙ ДВОИЧНЫЙ СУММАТОР ФУНКЦИОНАЛЬНОГОТИПА | 1971 |

|

SU299844A1 |

| КОЛЬЦЕВОЙ СЧЕТЧИК | 1972 |

|

SU427478A1 |

| ПИКОВЫЙ ДЕТЕКТОР | 2009 |

|

RU2409818C1 |

| ПОРОГОВЫЙ ЭЛЕМЕНТ ТРОИЧНОЙ ЛОГИКИ И УСТРОЙСТВА НА ЕГО ОСНОВЕ | 2009 |

|

RU2394366C1 |

| Коммутатор аналоговых сигналов | 1981 |

|

SU978345A1 |

| Управляемый генератор импульсов | 1984 |

|

SU1188857A1 |

| ПЛТСНТВО- |л'^ | 1970 |

|

SU265566A1 |

| Датчик угловой скорости | 1985 |

|

SU1296949A1 |

| Преобразователь биполярного кода в однополярный | 1981 |

|

SU1058050A1 |

| МИКРОМОЩНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ С ВЫСОКОЙ НАГРУЗОЧНОЙ СПОСОБНОСТЬЮ | 1999 |

|

RU2172064C2 |

0-5

Даты

1971-01-01—Публикация